多芯片组件的封装结构及封装方法.pdf

Ch****49

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

多芯片组件的封装结构及封装方法.pdf

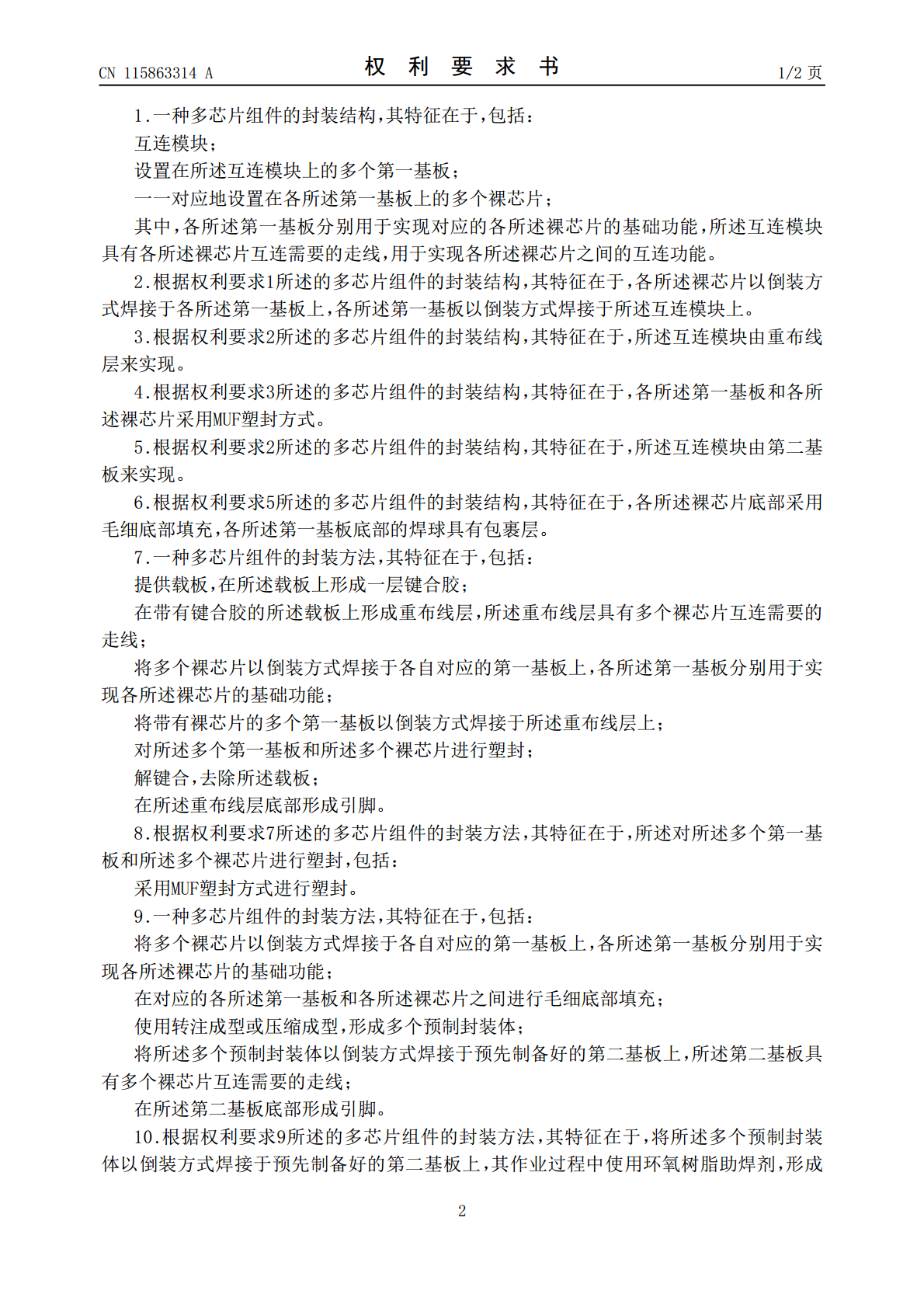

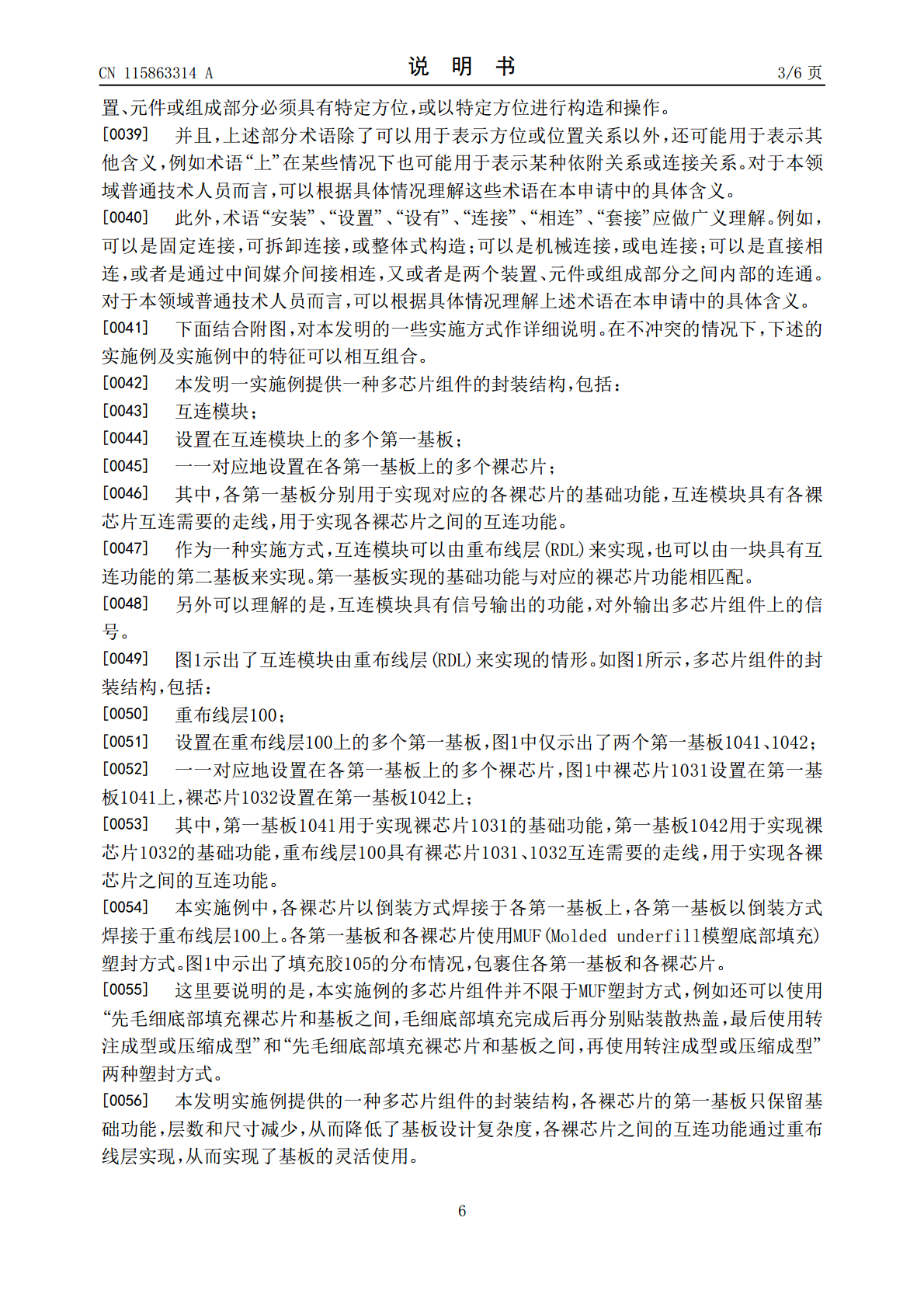

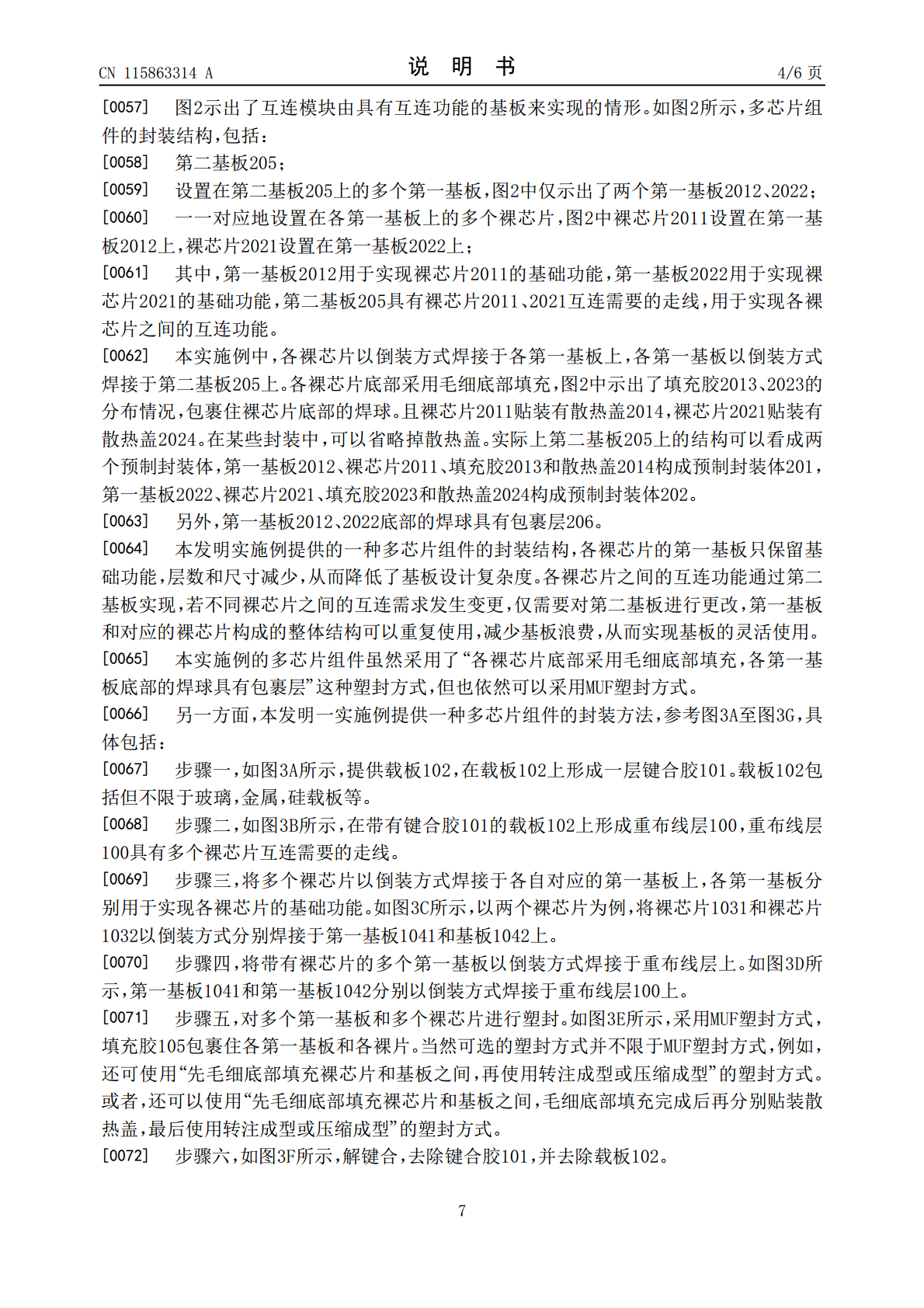

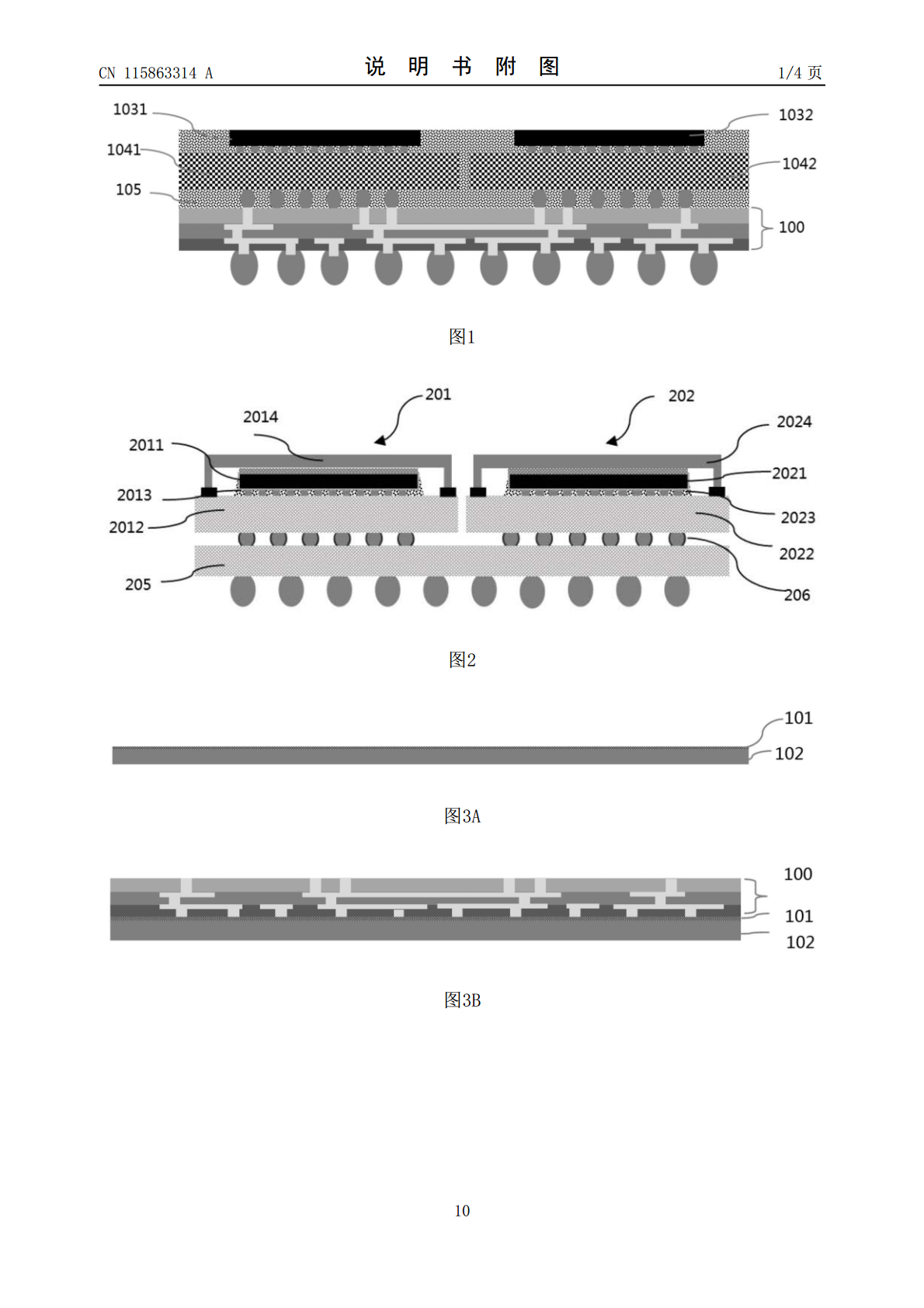

本发明提供一种多芯片组件的封装结构及封装方法,所述封装结构包括:互连模块;设置在互连模块上的多个第一基板;一一对应地设置在各第一基板上的多个裸芯片;其中,各第一基板分别用于实现对应的各裸芯片的基础功能,互连模块具有各裸芯片互连需要的走线,用于实现各裸芯片之间的互连功能。本发明能够简化基板设计,提高基板利用率。

多芯片封装结构、多芯片封装结构的制造方法.pdf

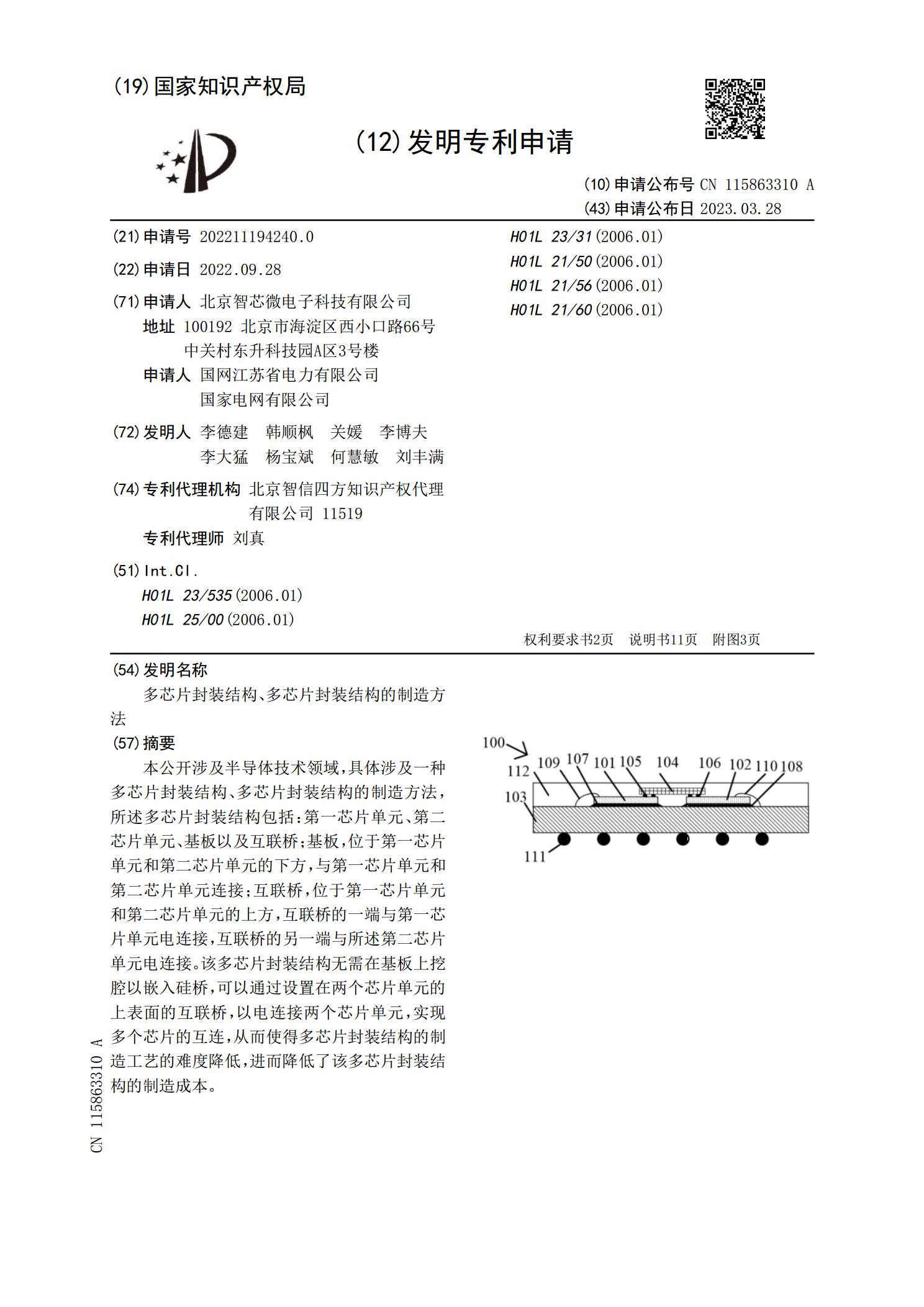

本公开涉及半导体技术领域,具体涉及一种多芯片封装结构、多芯片封装结构的制造方法,所述多芯片封装结构包括:第一芯片单元、第二芯片单元、基板以及互联桥;基板,位于第一芯片单元和第二芯片单元的下方,与第一芯片单元和第二芯片单元连接;互联桥,位于第一芯片单元和第二芯片单元的上方,互联桥的一端与第一芯片单元电连接,互联桥的另一端与所述第二芯片单元电连接。该多芯片封装结构无需在基板上挖腔以嵌入硅桥,可以通过设置在两个芯片单元的上表面的互联桥,以电连接两个芯片单元,实现多个芯片的互连,从而使得多芯片封装结构的制造工艺的

多芯片封装结构及封装方法.pdf

本发明提供一种多芯片封装结构及封装方法,封装结构包括基板、第一芯片组及第二芯片组,基板包括相对设置的顶面、底面以及贯穿顶面及底面的开孔,第一芯片组与基板电性连接,且第一芯片组面向顶面的第一表面上具有第一连接部,第二芯片组包括相对设置的第二表面及第三表面,第二表面面向第一表面且具有第二连接部,其中,第一连接部直接电性连接第二连接部,且至少部分第二芯片组位于开孔内或者位于开孔沿着基板的厚度方向的延伸空间内。本发明的第一芯片组与第二芯片组直接串接在一起,可省去额外的布线,进而提高传输效率,另外,开孔的设置不仅便

芯片封装方法及芯片封装结构.pdf

本发明提供一种芯片封装方法及芯片封装结构,在元件晶圆上形成有暴露用于晶片堆叠的预留位置表面的具有较低热膨胀系数的热膨胀系数过渡层,可以避免包封层对元件晶圆上的晶片和热膨胀系数过渡层包封后引起较大的热膨胀系数不匹配的问题,由此能够改善晶圆翘曲和应力引起的分层的问题,避免堆叠的晶片和包封层从元件晶圆上剥离,提高封装结构的性能;进一步的,所述热膨胀系数过渡层采用印刷电路板用阻焊剂材料形成,易于实现,不会产生副作用,并可以增强与后续包封层之间的粘附性,避免包封层从元件晶圆表面剥离。

芯片封装方法及芯片封装结构.pdf

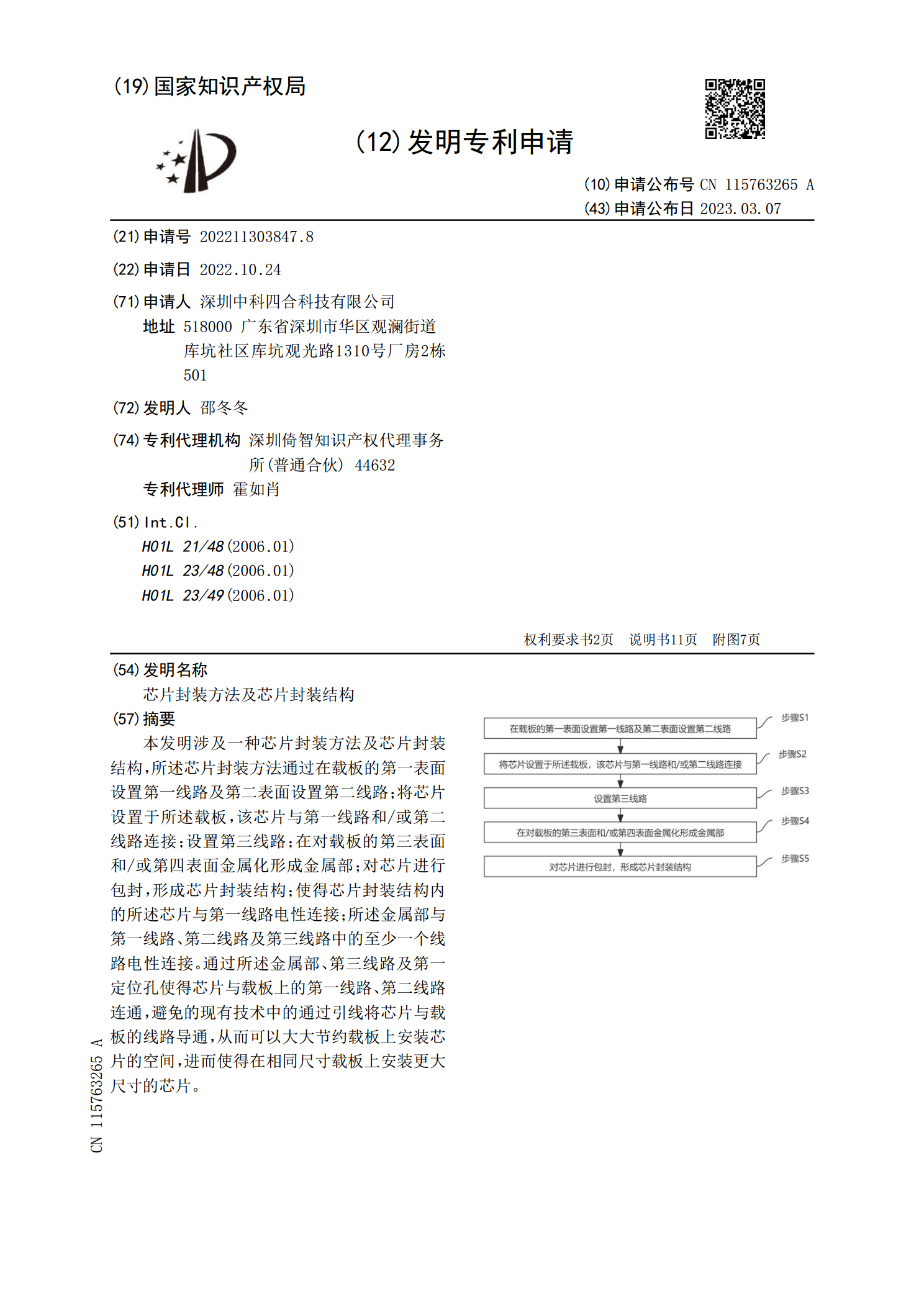

本发明涉及一种芯片封装方法及芯片封装结构,所述芯片封装方法通过在载板的第一表面设置第一线路及第二表面设置第二线路;将芯片设置于所述载板,该芯片与第一线路和/或第二线路连接;设置第三线路;在对载板的第三表面和/或第四表面金属化形成金属部;对芯片进行包封,形成芯片封装结构;使得芯片封装结构内的所述芯片与第一线路电性连接;所述金属部与第一线路、第二线路及第三线路中的至少一个线路电性连接。通过所述金属部、第三线路及第一定位孔使得芯片与载板上的第一线路、第二线路连通,避免的现有技术中的通过引线将芯片与载板的线路导通