半导体器件和包括其的数据存储系统.pdf

高格****gu

亲,该文档总共51页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

半导体器件和包括其的数据存储系统.pdf

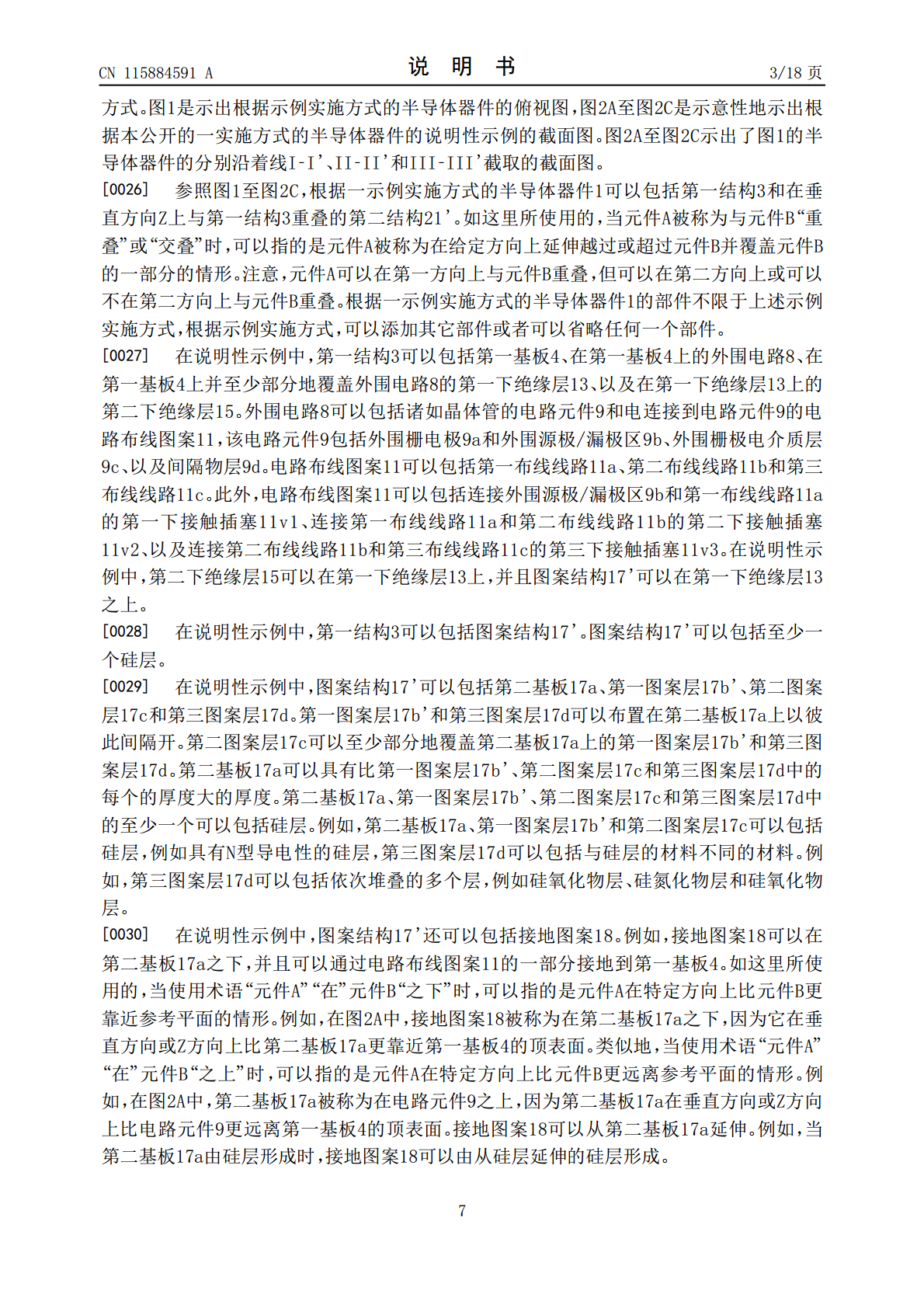

本公开提供了一种半导体器件和包括其的数据存储系统。该半导体器件包括:堆叠结构,包括在下部结构上的层间绝缘层和水平层;垂直存储结构,在垂直方向上穿过堆叠结构;第一阻挡结构和第二阻挡结构,在垂直方向上穿过堆叠结构并且彼此平行;穿过堆叠结构的支撑物图案;以及穿过堆叠结构的贯穿接触插塞。第一阻挡结构包括在第一方向上排列并彼此间隔开的第一阻挡图案以及在第一方向上排列并彼此间隔开的第二阻挡图案。第一阻挡图案和第二阻挡图案中的每个包括在第一方向上延伸的线形形状。在彼此相邻的第一阻挡图案和第二阻挡图案中,第一阻挡图案的一

半导体器件和包括其的数据存储系统.pdf

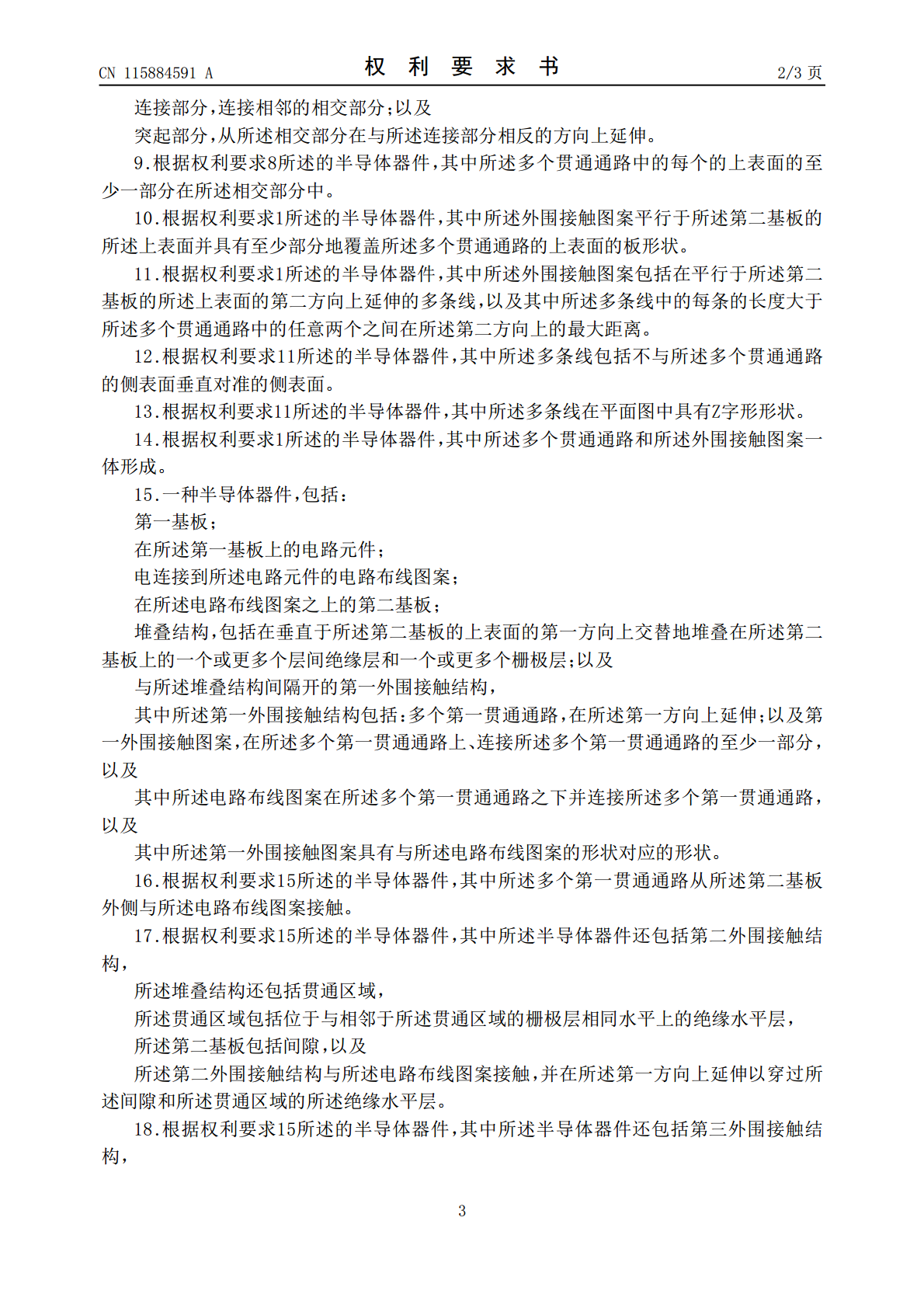

本公开涉及半导体器件和包括其的数据存储系统。该半导体器件包括:第一基板;第二基板,包括第一区域和第二区域;堆叠结构,在第一区域中并从第一区域延伸到第二区域,堆叠结构包括层间绝缘层和栅极层,其中栅极层包括在第二区域中具有台阶形状的栅极焊盘;覆盖绝缘层,至少部分地覆盖堆叠结构;上绝缘层,在堆叠结构和覆盖绝缘层上;外围接触结构,包括接触第二基板并与栅极层间隔开的多个贯通通路,以及外围接触图案,在所述多个贯通通路上并将所述多个贯通通路的至少一部分彼此连接;存储器垂直结构;支撑垂直结构;以及栅极接触插塞,在栅极焊盘

半导体器件及包括其的数据存储系统.pdf

一种半导体器件包括堆叠结构,该堆叠结构包括栅极堆叠区和虚设堆叠区。栅极堆叠区包括交替堆叠的层间绝缘层和栅电极。虚设堆叠区包括交替堆叠的虚设绝缘层和虚设水平层。分离结构穿透堆叠结构。垂直存储结构在第一区域中穿透栅极堆叠区。多个栅极接触结构在第二区域中电连接到栅电极。栅电极包括第一栅电极和设置在比第一栅电极的水平高的水平上的第二栅电极。每个栅极接触结构包括栅极接触插塞和第一绝缘间隔物。栅极接触插塞包括第一栅极接触插塞和第二栅极接触插塞,第一栅极接触插塞穿透第二栅电极并接触第一栅电极,第二栅极接触插塞接触第二栅

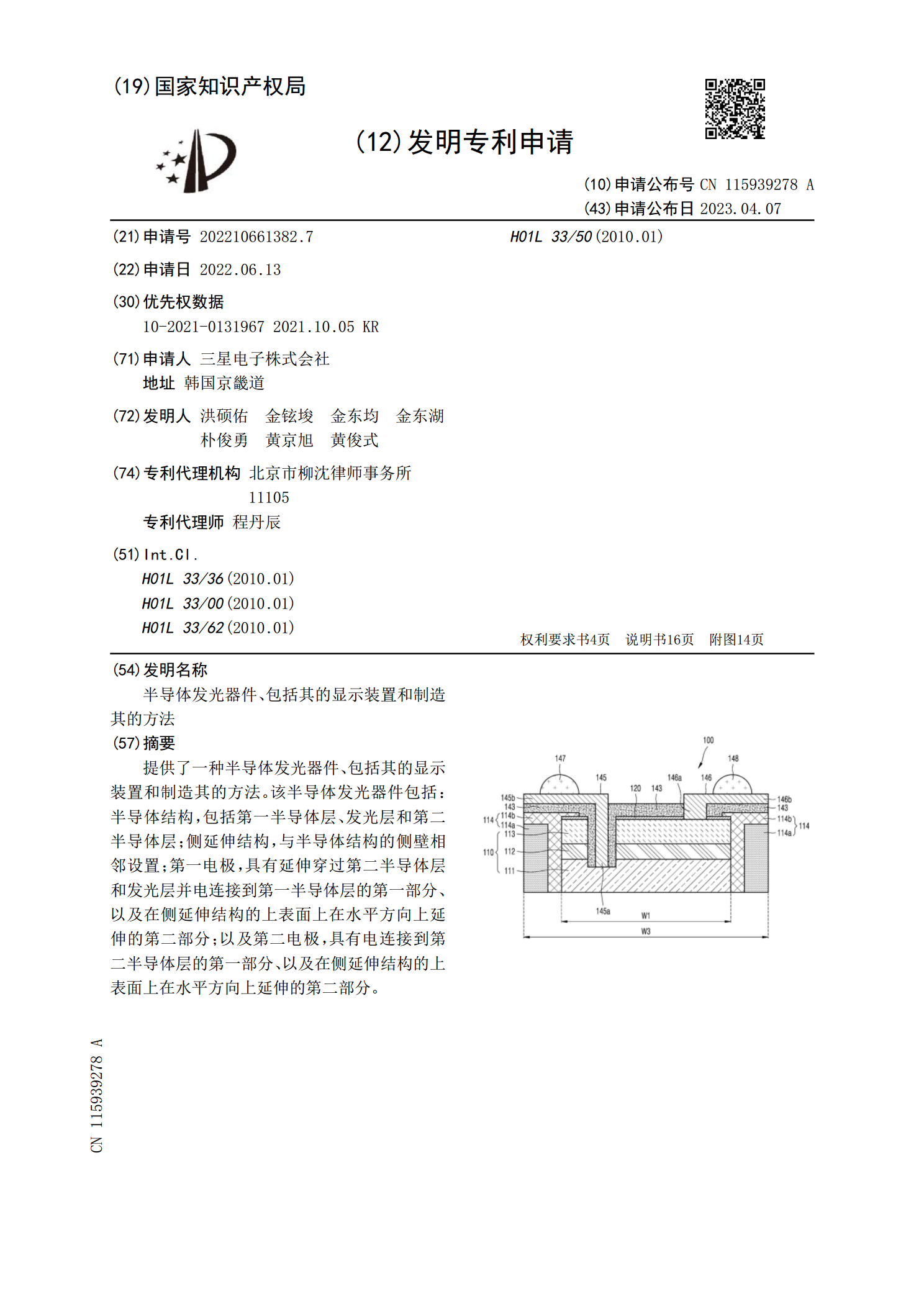

半导体发光器件、包括其的显示装置和制造其的方法.pdf

提供了一种半导体发光器件、包括其的显示装置和制造其的方法。该半导体发光器件包括:半导体结构,包括第一半导体层、发光层和第二半导体层;侧延伸结构,与半导体结构的侧壁相邻设置;第一电极,具有延伸穿过第二半导体层和发光层并电连接到第一半导体层的第一部分、以及在侧延伸结构的上表面上在水平方向上延伸的第二部分;以及第二电极,具有电连接到第二半导体层的第一部分、以及在侧延伸结构的上表面上在水平方向上延伸的第二部分。

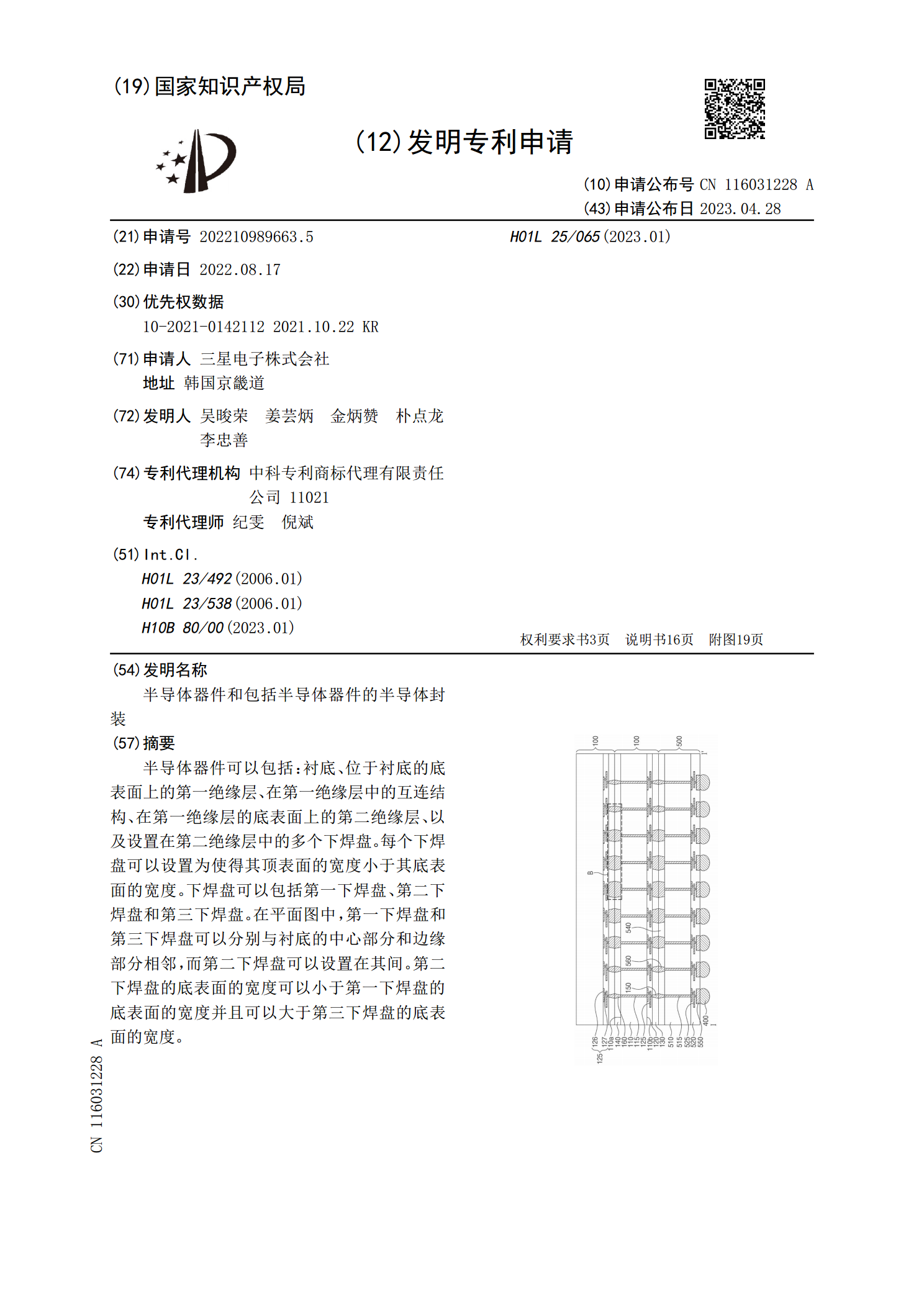

半导体器件和包括半导体器件的半导体封装.pdf

半导体器件可以包括:衬底、位于衬底的底表面上的第一绝缘层、在第一绝缘层中的互连结构、在第一绝缘层的底表面上的第二绝缘层、以及设置在第二绝缘层中的多个下焊盘。每个下焊盘可以设置为使得其顶表面的宽度小于其底表面的宽度。下焊盘可以包括第一下焊盘、第二下焊盘和第三下焊盘。在平面图中,第一下焊盘和第三下焊盘可以分别与衬底的中心部分和边缘部分相邻,而第二下焊盘可以设置在其间。第二下焊盘的底表面的宽度可以小于第一下焊盘的底表面的宽度并且可以大于第三下焊盘的底表面的宽度。