电子半导体器件和制备所述电子半导体器件的方法.pdf

青团****青吖

亲,该文档总共31页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

电子半导体器件和制备所述电子半导体器件的方法.pdf

本发明涉及电子半导体器件和制备所述电子半导体器件的方法。具体地,本发明涉及一种电子器件,其在第一电极与第二电极之间包含至少一个第一空穴传输层,其中所述第一空穴传输层包含:(i)至少一种由共价结合的原子构成的第一空穴传输基质化合物,和(ii)至少一种p型电掺杂剂,所述p型电掺杂剂选自金属盐以及包含金属阳离子和由至少4个共价结合的原子构成的至少一个阴离子和/或至少一个阴离子配体的电中性金属络合物,其中所述p型电掺杂剂的金属阳离子选自:碱金属;碱土金属、Pb、Mn、Fe、Co、Ni、Zn、Cd;处于氧化态(II

半导体器件、半导体器件的制备方法及电子设备.pdf

本发明提供一种半导体器件、半导体器件的制备方法及电子设备,涉及半导体技术领域。该半导体器件包括高压耗尽型碳化硅结型场效应晶体管,所述高压耗尽型碳化硅结型场效应晶体管包括第一栅极、第一漏极和第一源极;低压增强型氮化镓高电子迁移率晶体管,所述低压增强型氮化镓高电子迁移率晶体管包括第二栅极、第二漏极和第二源极;其中,所述第一栅极和所述第二源极连接,所述第一源极和所述第二漏极连接,半导体器件的源极为所述第二源极,所述半导体器件的栅极为所述第二栅极,所述半导体器件的漏极为所述第一漏极。该半导体器件为共源共栅结构,结

半导体器件的制备方法和半导体器件.pdf

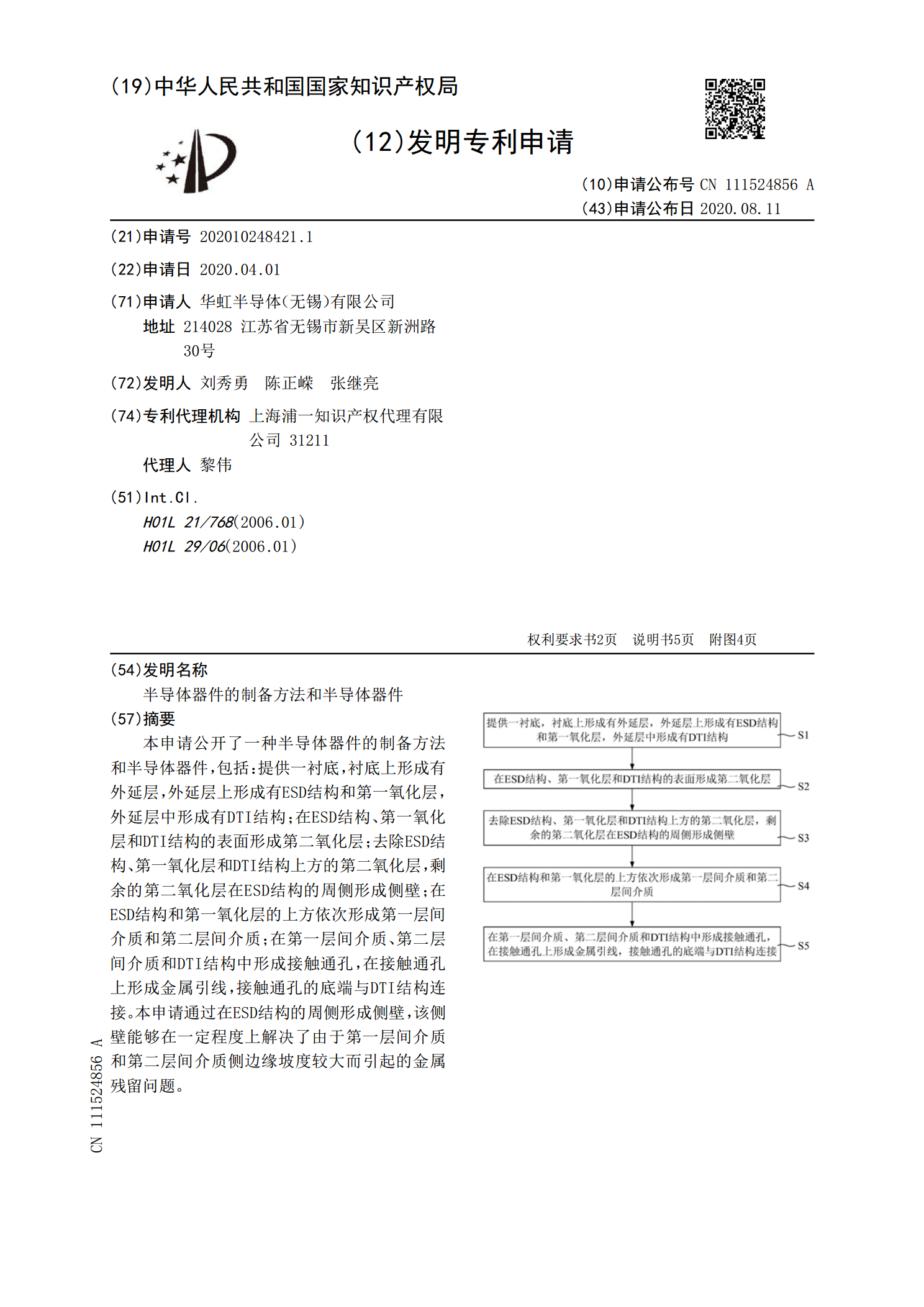

本申请公开了一种半导体器件的制备方法和半导体器件,包括:提供一衬底,衬底上形成有外延层,外延层上形成有ESD结构和第一氧化层,外延层中形成有DTI结构;在ESD结构、第一氧化层和DTI结构的表面形成第二氧化层;去除ESD结构、第一氧化层和DTI结构上方的第二氧化层,剩余的第二氧化层在ESD结构的周侧形成侧壁;在ESD结构和第一氧化层的上方依次形成第一层间介质和第二层间介质;在第一层间介质、第二层间介质和DTI结构中形成接触通孔,在接触通孔上形成金属引线,接触通孔的底端与DTI结构连接。本申请通过在ESD结

半导体器件的制备方法和半导体器件.pdf

本发明实施例公开了一种半导体器件的制备方法和半导体器件。方法包括:提供具有多个有源区的衬底,有源区包括源漏极区,位线接触区,字线段和字线绝缘结构;在源漏极区上形成保护层,且保护层覆盖字线绝缘结构并具有在位线接触区上形成的接触通道,接触通道连通到位线接触区;形成缓冲材料层,覆盖保护层以及接触通道的侧壁;刻蚀缓冲材料层,保留缓冲材料层位于接触通道的侧壁的部分,以形成缓冲层,缓冲层再定义接触通道的宽度;在保护层上及接触通道内形成位线材料层,位线材料层还覆盖缓冲层;图案化位线材料层,以在所述接触通道之上形成高于保

半导体器件和制备半导体器件的方法.pdf

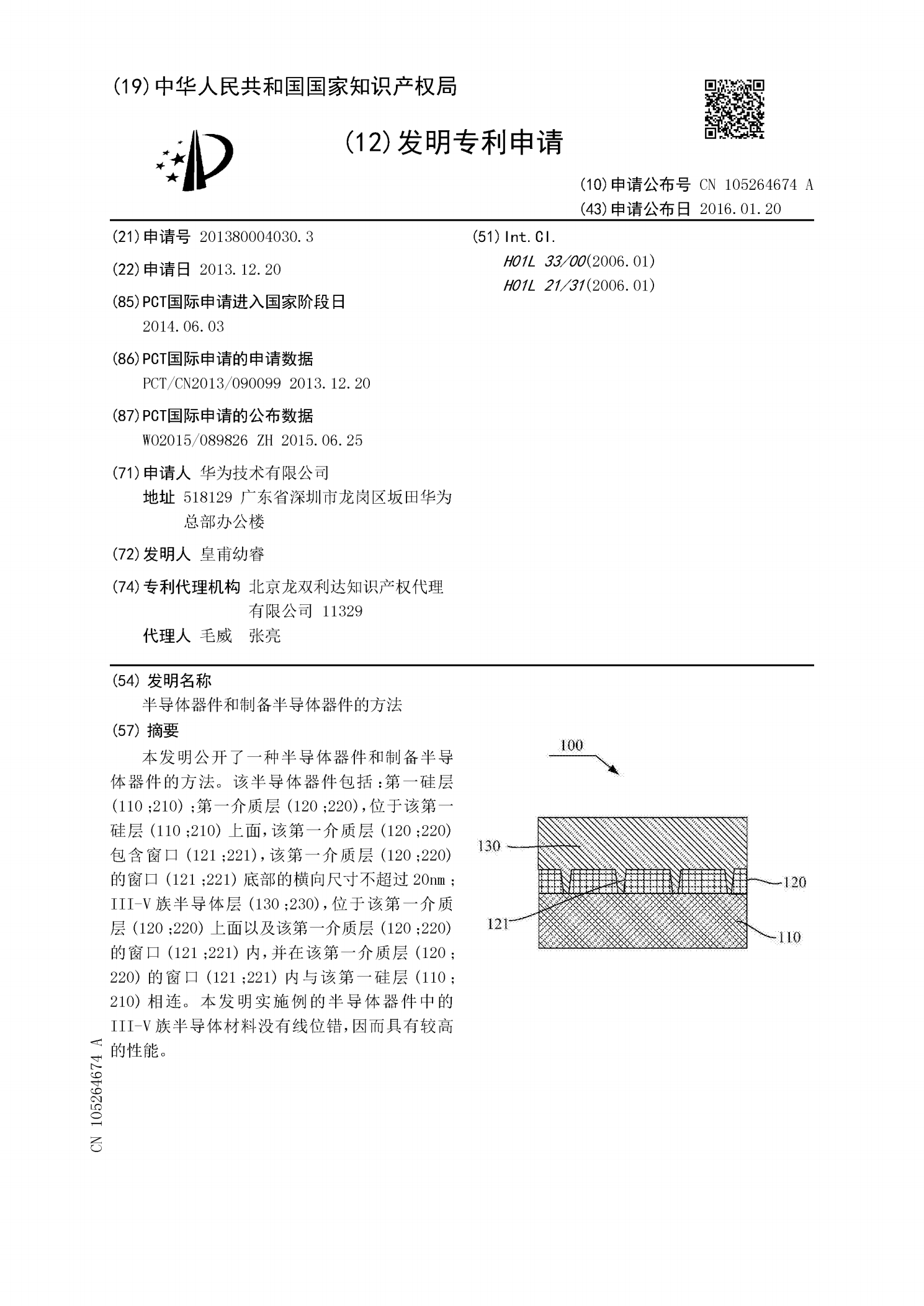

本发明公开了一种半导体器件和制备半导体器件的方法。该半导体器件包括:第一硅层(110;210);第一介质层(120;220),位于该第一硅层(110;210)上面,该第一介质层(120;220)包含窗口(121;221),该第一介质层(120;220)的窗口(121;221)底部的横向尺寸不超过20nm;III-V族半导体层(130;230),位于该第一介质层(120;220)上面以及该第一介质层(120;220)的窗口(121;221)内,并在该第一介质层(120;220)的窗口(121;221)内与该