一种射频前端集成芯片.pdf

景福****90

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种射频前端集成芯片.pdf

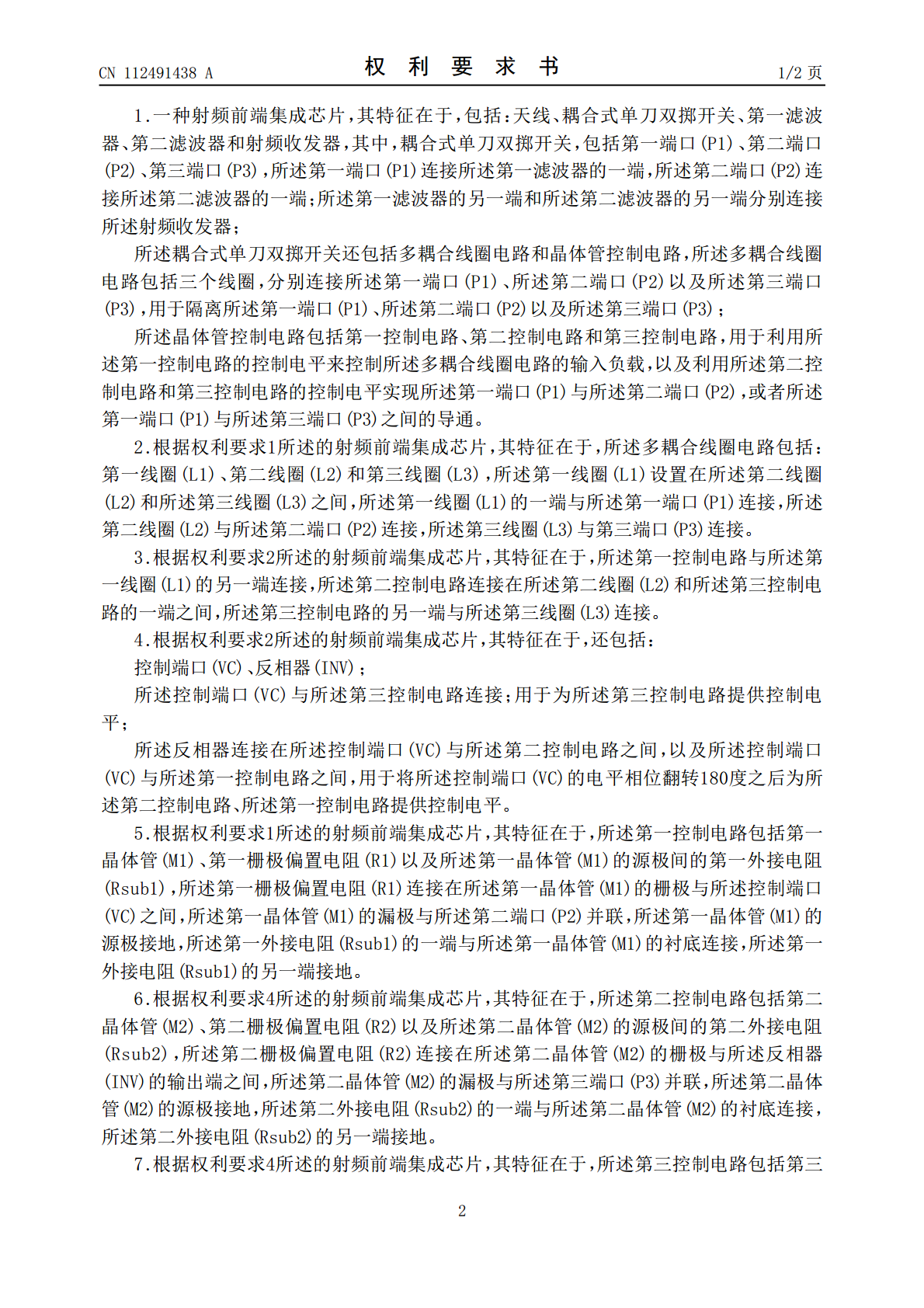

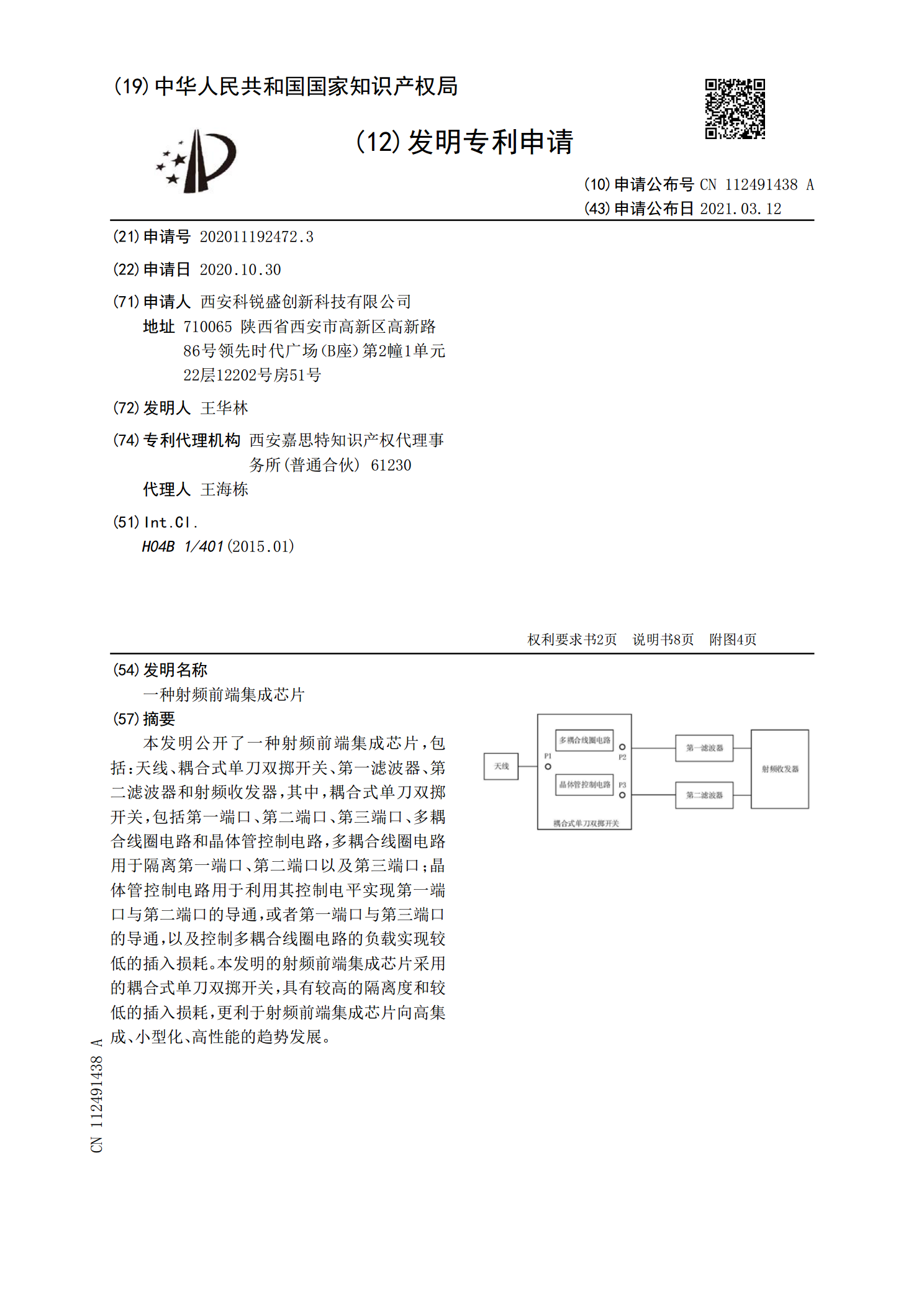

本发明公开了一种射频前端集成芯片,包括:天线、耦合式单刀双掷开关、第一滤波器、第二滤波器和射频收发器,其中,耦合式单刀双掷开关,包括第一端口、第二端口、第三端口、多耦合线圈电路和晶体管控制电路,多耦合线圈电路用于隔离第一端口、第二端口以及第三端口;晶体管控制电路用于利用其控制电平实现第一端口与第二端口的导通,或者第一端口与第三端口的导通,以及控制多耦合线圈电路的负载实现较低的插入损耗。本发明的射频前端集成芯片采用的耦合式单刀双掷开关,具有较高的隔离度和较低的插入损耗,更利于射频前端集成芯片向高集成、小型化

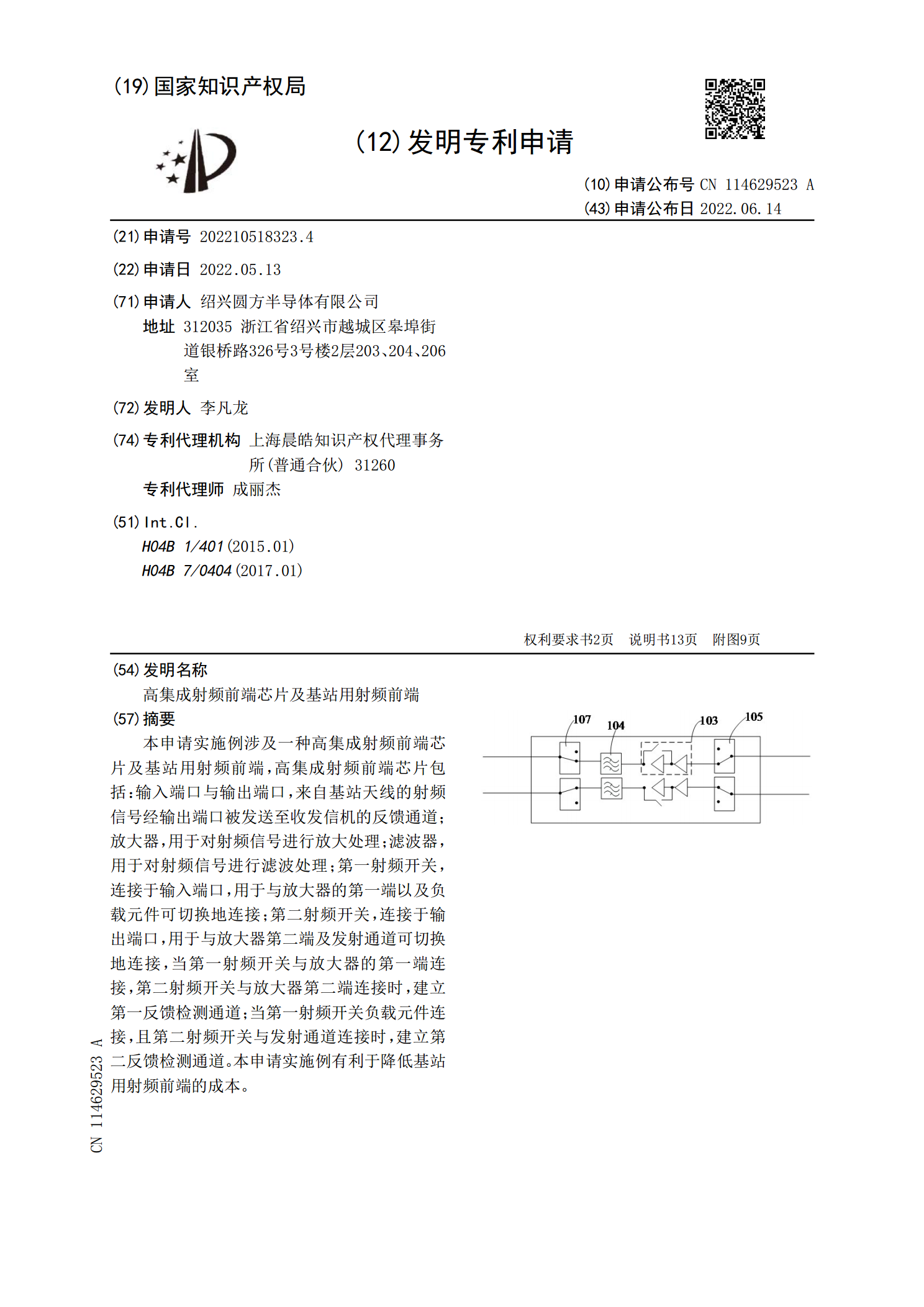

高集成射频前端芯片及基站用射频前端.pdf

本申请实施例涉及一种高集成射频前端芯片及基站用射频前端,高集成射频前端芯片包括:输入端口与输出端口,来自基站天线的射频信号经输出端口被发送至收发信机的反馈通道;放大器,用于对射频信号进行放大处理;滤波器,用于对射频信号进行滤波处理;第一射频开关,连接于输入端口,用于与放大器的第一端以及负载元件可切换地连接;第二射频开关,连接于输出端口,用于与放大器第二端及发射通道可切换地连接,当第一射频开关与放大器的第一端连接,第二射频开关与放大器第二端连接时,建立第一反馈检测通道;当第一射频开关负载元件连接,且第二射频

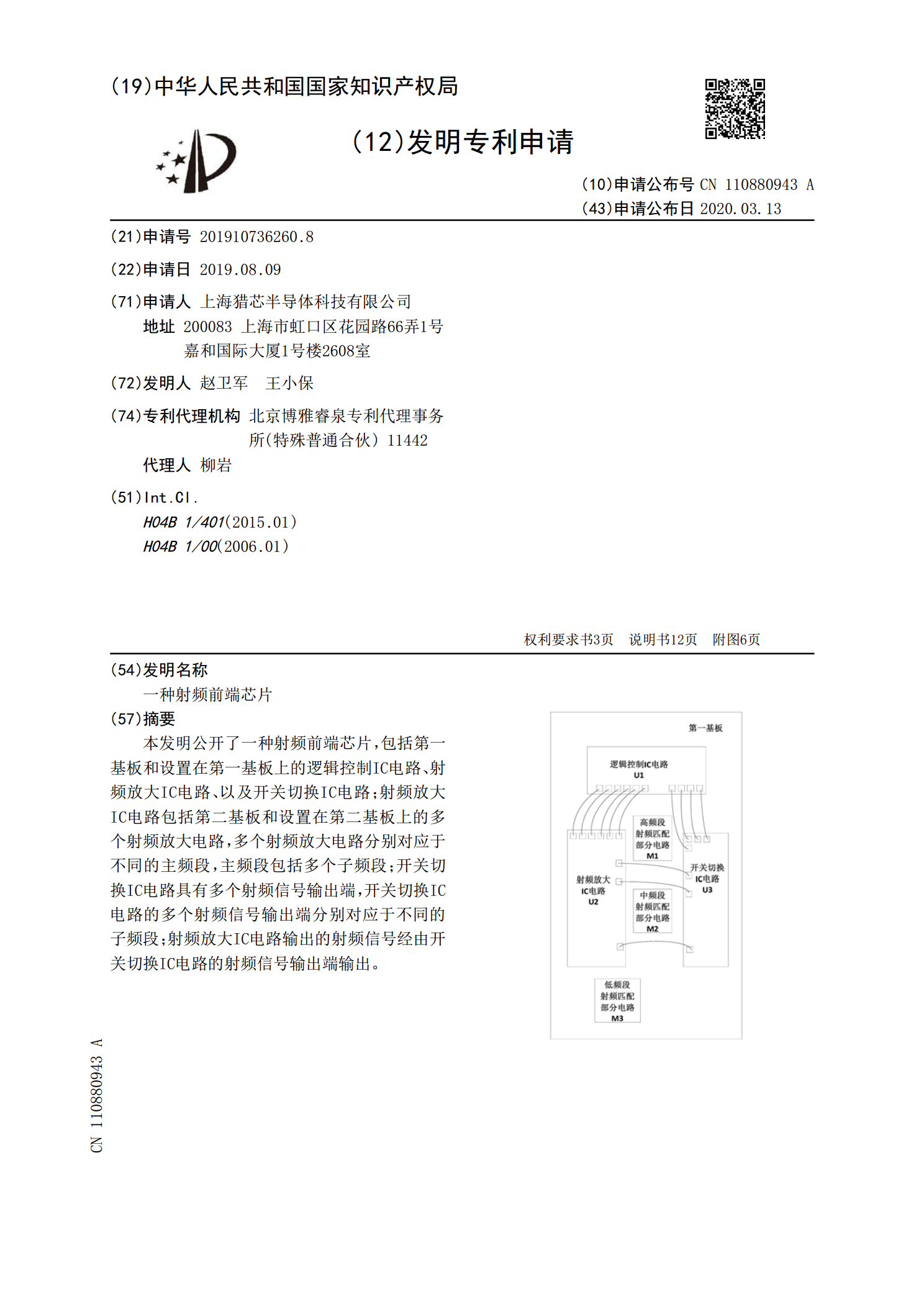

一种射频前端芯片.pdf

本发明公开了一种射频前端芯片,包括第一基板和设置在第一基板上的逻辑控制IC电路、射频放大IC电路、以及开关切换IC电路;射频放大IC电路包括第二基板和设置在第二基板上的多个射频放大电路,多个射频放大电路分别对应于不同的主频段,主频段包括多个子频段;开关切换IC电路具有多个射频信号输出端,开关切换IC电路的多个射频信号输出端分别对应于不同的子频段;射频放大IC电路输出的射频信号经由开关切换IC电路的射频信号输出端输出。

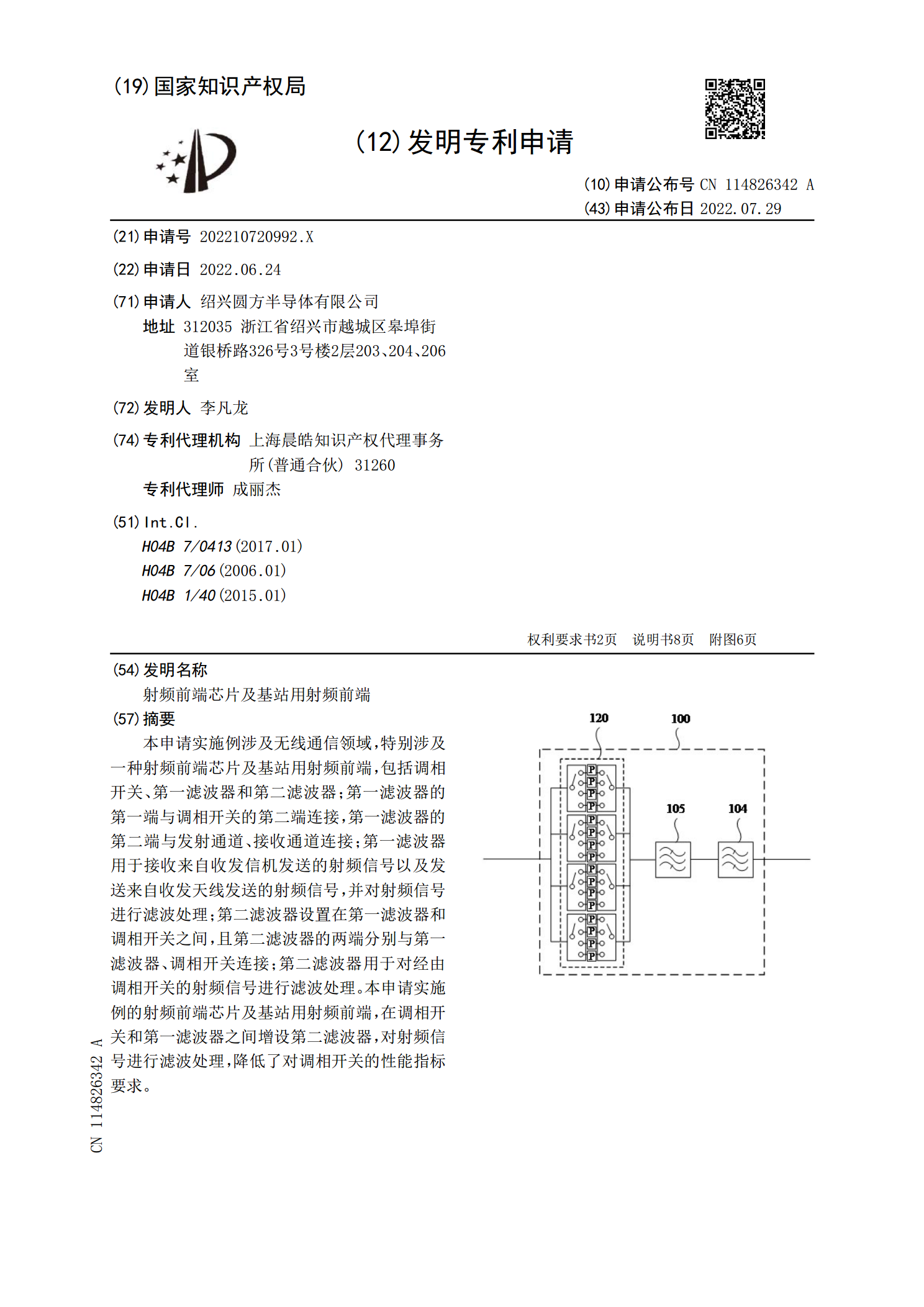

射频前端芯片及基站用射频前端.pdf

本申请实施例涉及无线通信领域,特别涉及一种射频前端芯片及基站用射频前端,包括调相开关、第一滤波器和第二滤波器;第一滤波器的第一端与调相开关的第二端连接,第一滤波器的第二端与发射通道、接收通道连接;第一滤波器用于接收来自收发信机发送的射频信号以及发送来自收发天线发送的射频信号,并对射频信号进行滤波处理;第二滤波器设置在第一滤波器和调相开关之间,且第二滤波器的两端分别与第一滤波器、调相开关连接;第二滤波器用于对经由调相开关的射频信号进行滤波处理。本申请实施例的射频前端芯片及基站用射频前端,在调相开关和第一滤波

单芯片集成WLAN射频收发机中前端电路研究.docx

单芯片集成WLAN射频收发机中前端电路研究本文主要探讨单芯片集成WLAM射频收发机中前端电路的研究。在目前的通信技术中,WLAN(无线局域网)已经成为一种常用的无线通信方式。单芯片集成WLAN射频收发机是实现WLAN通信的核心设备。而前端电路则是其中重要的组成部分。本文将从以下几个方面对单芯片集成WLAN射频收发机中前端电路进行探讨。一、前端电路的定义和作用前端电路是收发机中最先参与到信号处理中的电路,主要完成信号放大、过滤、匹配和偏置等功能。在单芯片集成WLAN射频收发机中,前端电路主要包括低噪声放大器