一种低功耗串行异步收发器及数据接收方法、介质.pdf

永香****能手

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种低功耗串行异步收发器及数据接收方法、介质.pdf

本公开涉及一种低功耗串行异步收发器(LPUART),低功耗串行异步收发器包括:带电模块,带电模块包括数据读写接口;被配置为在数据读写接口监测到第一个数据包时,产生复位信号;第一上电模块,被配置为与带电模块数据和信号连接;且在收到带电模块发出的复位信号后,在第一预设时长内完成上电;第二上电模块,被配置为与第一上电模块数据和信号连接;且在收到带电模块发出的复位信号后,在第二预设时长内完成上电;第一预设时长小于所述第二预设时长。本公开实现数据发送过程中耗能更低,过程中不会丢失数据,更加便捷。

基于SOC FPGA的串行收发器及数据接收发送方法.pdf

本发明提供一种基于SOCFPGA的串行收发器,包括现场可编程门阵列FPGA,所述现场可编程门阵列FPGA包含CPU接口通信模块、RAM存储器以及串行收发器接口模块;利用本发明,CPU可以直接发送整帧的数据,从而减小了CPU程序开发的复杂度;本发明实现了断帧功能,从而降低了CPU程序运行负荷;可以存储一整帧数据,大大减少了CPU内部资源浪费;现场可编程门阵列FPGA的灵活性和可扩展性,可以实现多个串行收发器的功能。

一种串行数据接收处理方法.pdf

本发明公开了一种串行数据接收处理方法,是通过一通信协议来实现的,该通信协议包括协议头、地址、长度、数据字节、校验位及结束符;接收处理采用中断接收,接收时先判断头字节、有效地址位,有地址位时则判断地址位,两者都正确时开始进行后面数据的正式接收,最后判定校验位和结束符是否都正确,如果都正确则表明数据接收正确,接收正确时开始处理解析,若不正确,此时接收的这帧数据不完全丢弃,将头字节移除FIFO缓存,其他字节留在缓存中,等待接收下一个字节后继续判断和接收。与现有技术相比,本发明,通过具体的系统试样验证,在数据传输

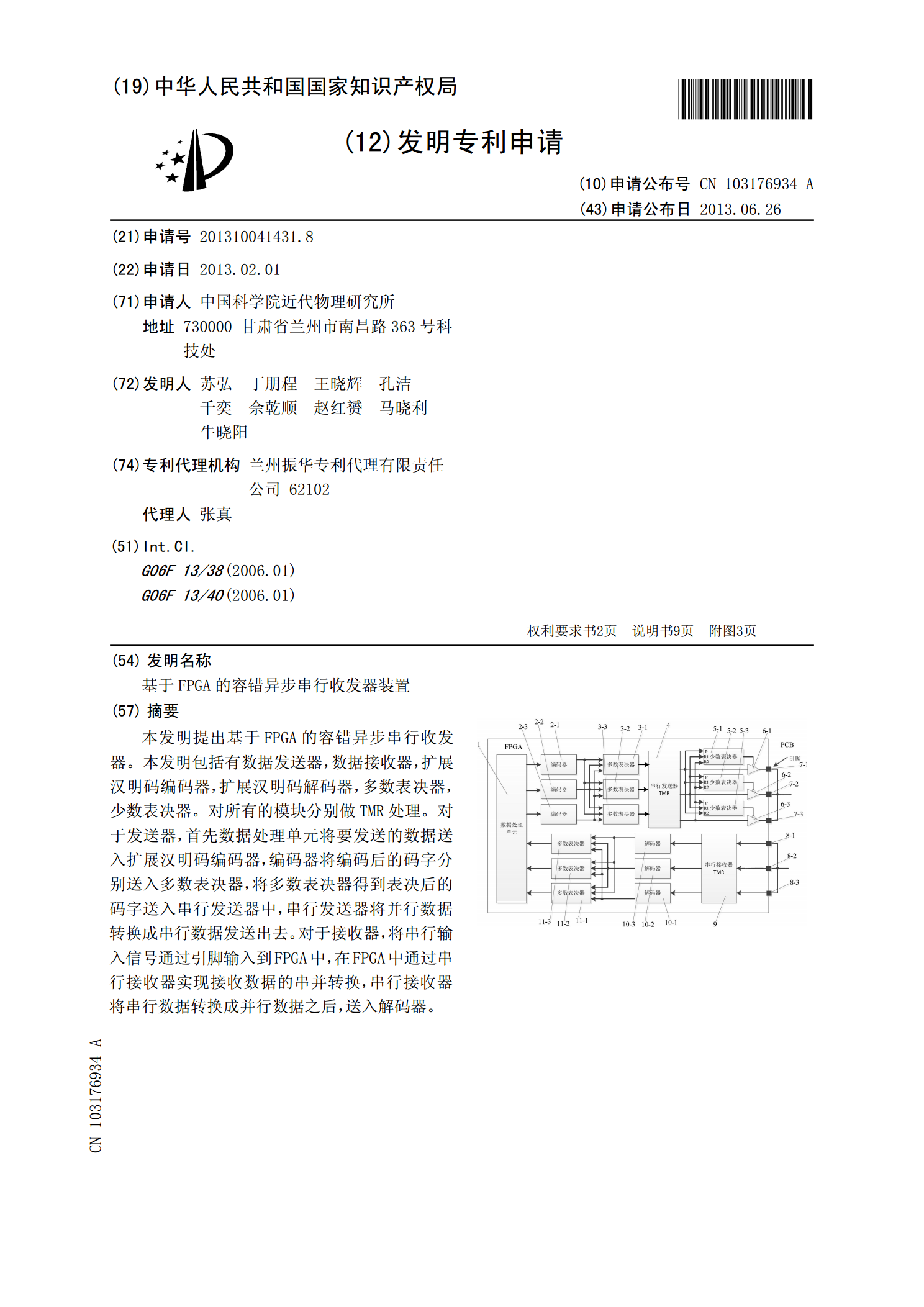

基于FPGA的容错异步串行收发器装置.pdf

本发明提出基于FPGA的容错异步串行收发器。本发明包括有数据发送器,数据接收器,扩展汉明码编码器,扩展汉明码解码器,多数表决器,少数表决器。对所有的模块分别做TMR处理。对于发送器,首先数据处理单元将要发送的数据送入扩展汉明码编码器,编码器将编码后的码字分别送入多数表决器,将多数表决器得到表决后的码字送入串行发送器中,串行发送器将并行数据转换成串行数据发送出去。对于接收器,将串行输入信号通过引脚输入到FPGA中,在FPGA中通过串行接收器实现接收数据的串并转换,串行接收器将串行数据转换成并行数据之后,送入

一种串行数据帧接收方法及装置.pdf

本发明提出了一种串行数据帧接收方法及装置,所述串行数据帧接收方法采用三线制方式接收同步串行RS‑422数据,通过判断光学舱平台发送的数据是否符合预设要求,保证了数据信号的正确获取,该方法可应用于稳定性、可靠性要求较高的串行传输中。本发明采取FPGA内多FIFO机制对不定周期串行数据帧进行接收,逻辑内实时判定数据帧头及FIFO中数据长度,若不满足协议要求,记录接收状态并更新参数信息后下传。多FIFO缓存既无额外芯片存储开销,也为CPU软件预留了更多的处理时间,优化了系统结构与处理方法。