基于FPGA的容错异步串行收发器装置.pdf

猫巷****傲柏

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的容错异步串行收发器装置.pdf

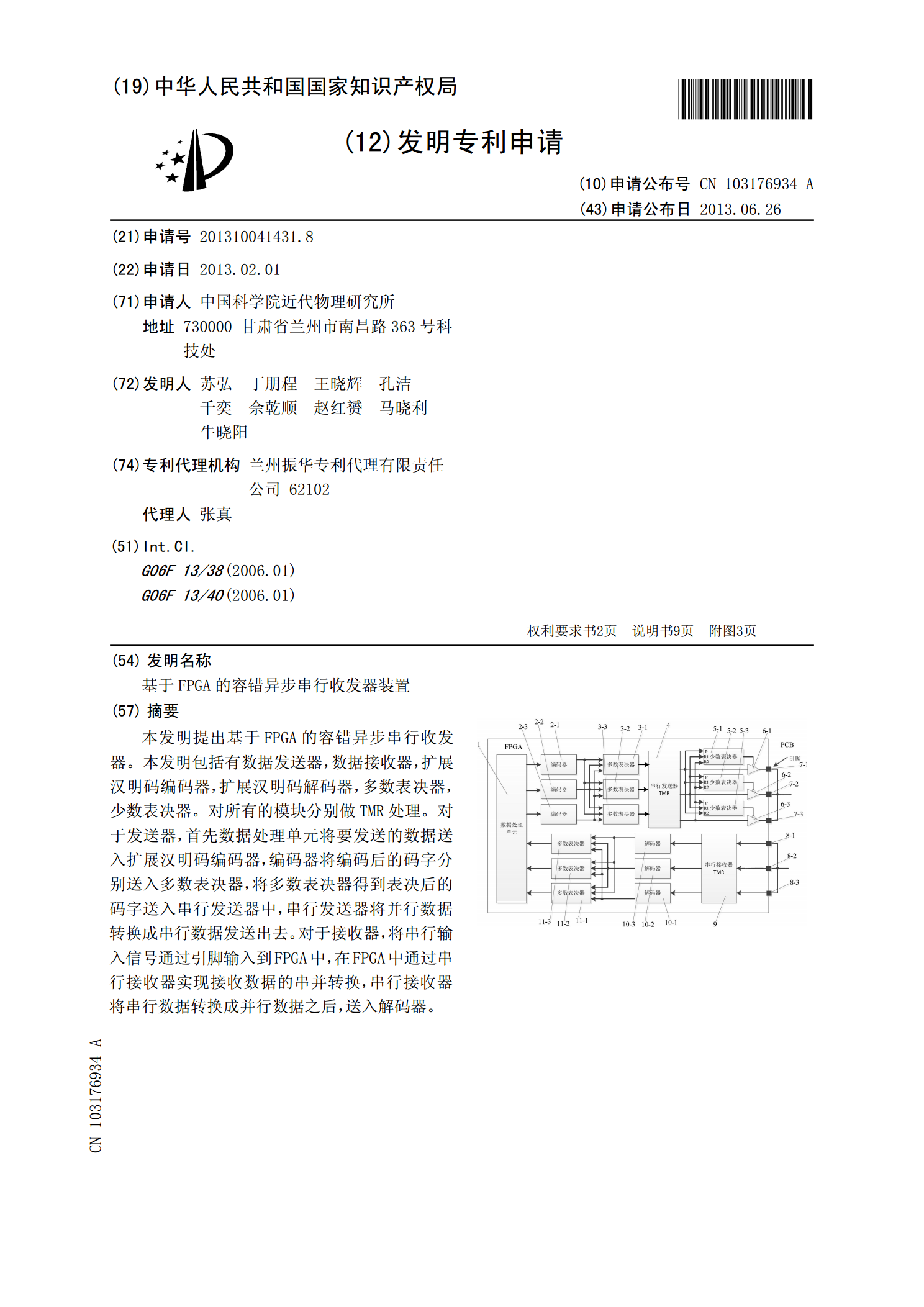

本发明提出基于FPGA的容错异步串行收发器。本发明包括有数据发送器,数据接收器,扩展汉明码编码器,扩展汉明码解码器,多数表决器,少数表决器。对所有的模块分别做TMR处理。对于发送器,首先数据处理单元将要发送的数据送入扩展汉明码编码器,编码器将编码后的码字分别送入多数表决器,将多数表决器得到表决后的码字送入串行发送器中,串行发送器将并行数据转换成串行数据发送出去。对于接收器,将串行输入信号通过引脚输入到FPGA中,在FPGA中通过串行接收器实现接收数据的串并转换,串行接收器将串行数据转换成并行数据之后,送入

基于FPGA实现异步串行通信.docx

基于FPGA实现异步串行通信基于FPGA实现异步串行通信摘要:随着信息技术的快速发展,串行通信在现代数字通信系统中起着至关重要的作用。为了满足不同的通信需求,异步串行通信成为一种常见的通信方式。本文将介绍基于FPGA(现场可编程逻辑门阵列)的异步串行通信的实现方法和其在通信系统中的应用。首先,对异步串行通信的基本原理进行介绍;然后,介绍FPGA的基本原理和特点;接着,详细阐述了如何使用FPGA实现异步串行通信;最后,总结了FPGA在异步串行通信中的优势和局限,并展望了未来的发展方向。关键词:异步串行通信、

基于FPGA的异步收发器模块设计.docx

基于FPGA的异步收发器模块设计异步收发器是数字电子电路中的重要组成部分,在不同的应用中广泛使用。它的主要作用是实现数据的传输和处理。基于FPGA的异步收发器模块设计是一项重要的任务,这篇论文将详细介绍这个问题。首先,介绍异步收发器的基本原理。异步收发器是一种数据传输电路,它能够在不同速度的系统之间进行数据传输。在异步收发器中,发送器和接收器之间没有时钟信号来同步数据传输。通常,发送器将数据转成一系列异步信号,由接收器进行恢复,然后将其转化回原始数据。在异步收发器中,控制信号是非常重要的。为了控制数据的传

基于FPGA的通用异步收发器设计.docx

基于FPGA的通用异步收发器设计基于FPGA的通用异步收发器设计摘要:本论文主要讨论了基于FPGA的通用异步收发器的设计。异步通信是一种无需使用时钟信号同步的通信方式,可以实现高速、灵活和可靠的数据传输。本文首先介绍了异步通信的原理和优势,然后详细阐述了基于FPGA的异步收发器的设计方法和实现过程。最后给出了设计的性能评估和未来改进的展望。关键词:FPGA,异步通信,收发器,设计,性能评估一、引言随着通信技术的发展和高速数据传输的需求不断增加,异步通信作为一种不依赖于时钟信号同步的通信方式,逐渐受到了广泛

基于FPGA的异步串行通信毕业论文.doc

电子科技大学成都学院本科毕业设计论文摘要III摘要为了适应全数字化自动控制更加广泛的应用采用FPGA对UART进行多模块的系统设计的方法使串口通信的集成度更高。对UART系统结构进行了多模块的分解。UART(通用异步收发器)是一种应用广泛的短距离串行传输接口常用于短距离、低速、低成本的通信中。本文采用Verilog语言设计了一个UART发送模块和接收模块从而可实现FPGA和PC机的异步串行通。利用Altera公司的EP1C6Q240I8芯片采用AltiumDesignerSummer09画出原理