半导体功率器件.pdf

一只****懿呀

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

功率半导体器件的加工方法及功率半导体器件.pdf

本申请涉及微电子技术领域,具体而言,涉及一种功率半导体器件的加工方法及功率半导体器件。功率半导体器件的加工方法包括以下步骤:在元胞区上刻蚀形成沟槽,在器件表面形成多晶硅层,多晶硅填满所述沟槽并在器件表面形成一定厚度;对元胞区部分的多晶硅层进行刻蚀,形成器件的栅极结构,对终端区部分的多晶硅层进行刻蚀形成器件的场板;其中,通过各向同性刻蚀方法刻蚀终端区部分的多晶硅层,所形成的场板的刻蚀剖面的侧壁与器件表面呈倾斜设置。通过变更刻蚀方法,采用各向同性的刻蚀方法将多晶硅层的边缘角度由直角刻蚀成斜角,ILD在垫积的时

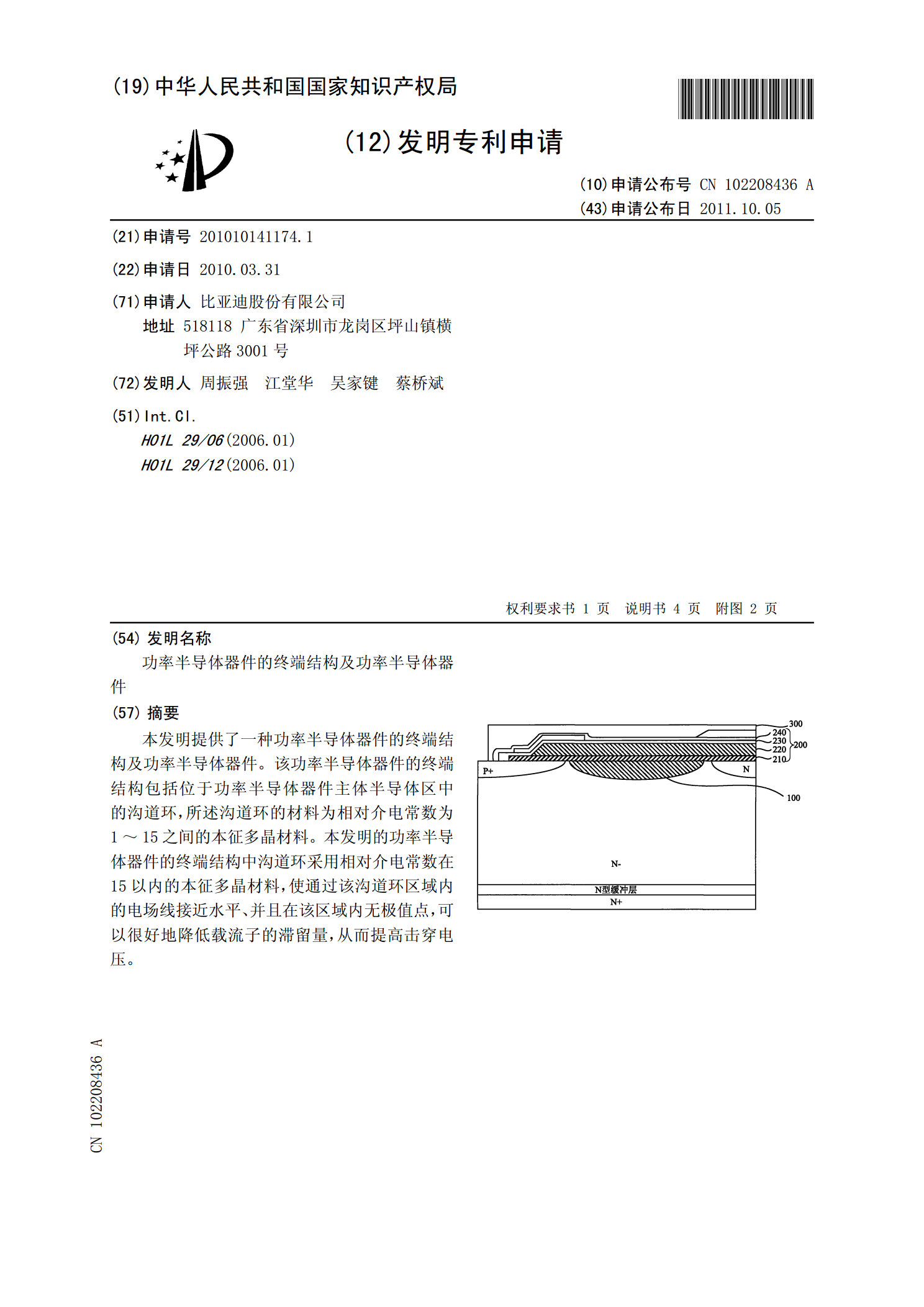

功率半导体器件的终端结构及功率半导体器件.pdf

本发明提供了一种功率半导体器件的终端结构及功率半导体器件。该功率半导体器件的终端结构包括位于功率半导体器件主体半导体区中的沟道环,所述沟道环的材料为相对介电常数为1~15之间的本征多晶材料。本发明的功率半导体器件的终端结构中沟道环采用相对介电常数在15以内的本征多晶材料,使通过该沟道环区域内的电场线接近水平、并且在该区域内无极值点,可以很好地降低载流子的滞留量,从而提高击穿电压。

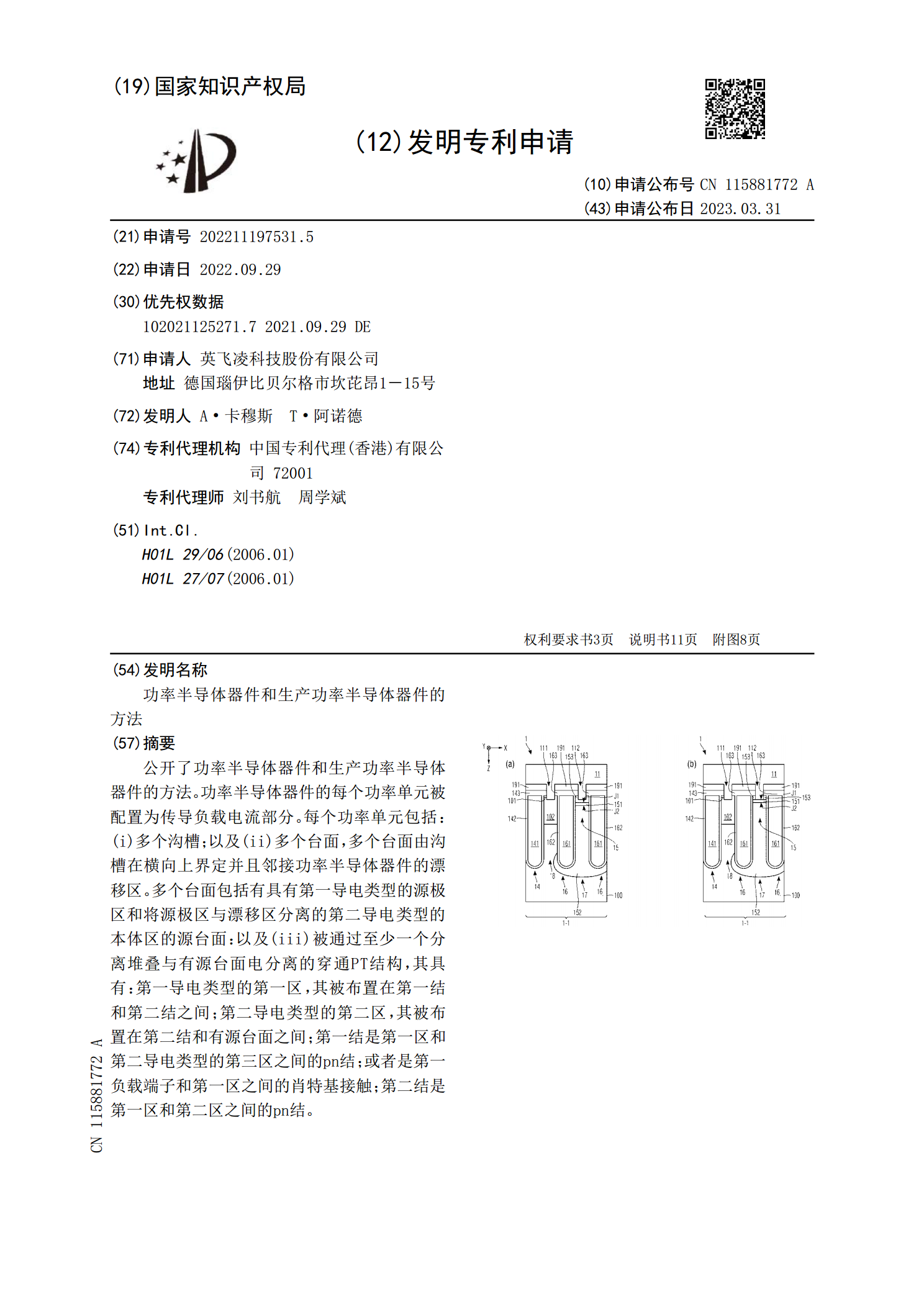

功率半导体器件和生产功率半导体器件的方法.pdf

公开了功率半导体器件和生产功率半导体器件的方法。功率半导体器件的每个功率单元被配置为传导负载电流部分。每个功率单元包括:(i)多个沟槽;以及(ii)多个台面,多个台面由沟槽在横向上界定并且邻接功率半导体器件的漂移区。多个台面包括有具有第一导电类型的源极区和将源极区与漂移区分离的第二导电类型的本体区的源台面:以及(iii)被通过至少一个分离堆叠与有源台面电分离的穿通PT结构,其具有:第一导电类型的第一区,其被布置在第一结和第二结之间;第二导电类型的第二区,其被布置在第二结和有源台面之间;第一结是第一区和第二

功率半导体器件封装结构和功率半导体器件模块.pdf

本发明提供一种功率半导体器件封装结构和功率半导体器件模块,功率半导体器件封装结构包括:下导电散热板,所述下导电散热板的一侧的部分表面具有沉槽;功率芯片,位于所述沉槽中,所述功率芯片与所述下导电散热板电连接。所述功率半导体器件封装结构的散热效果好、功率密度大且寄生电感低。

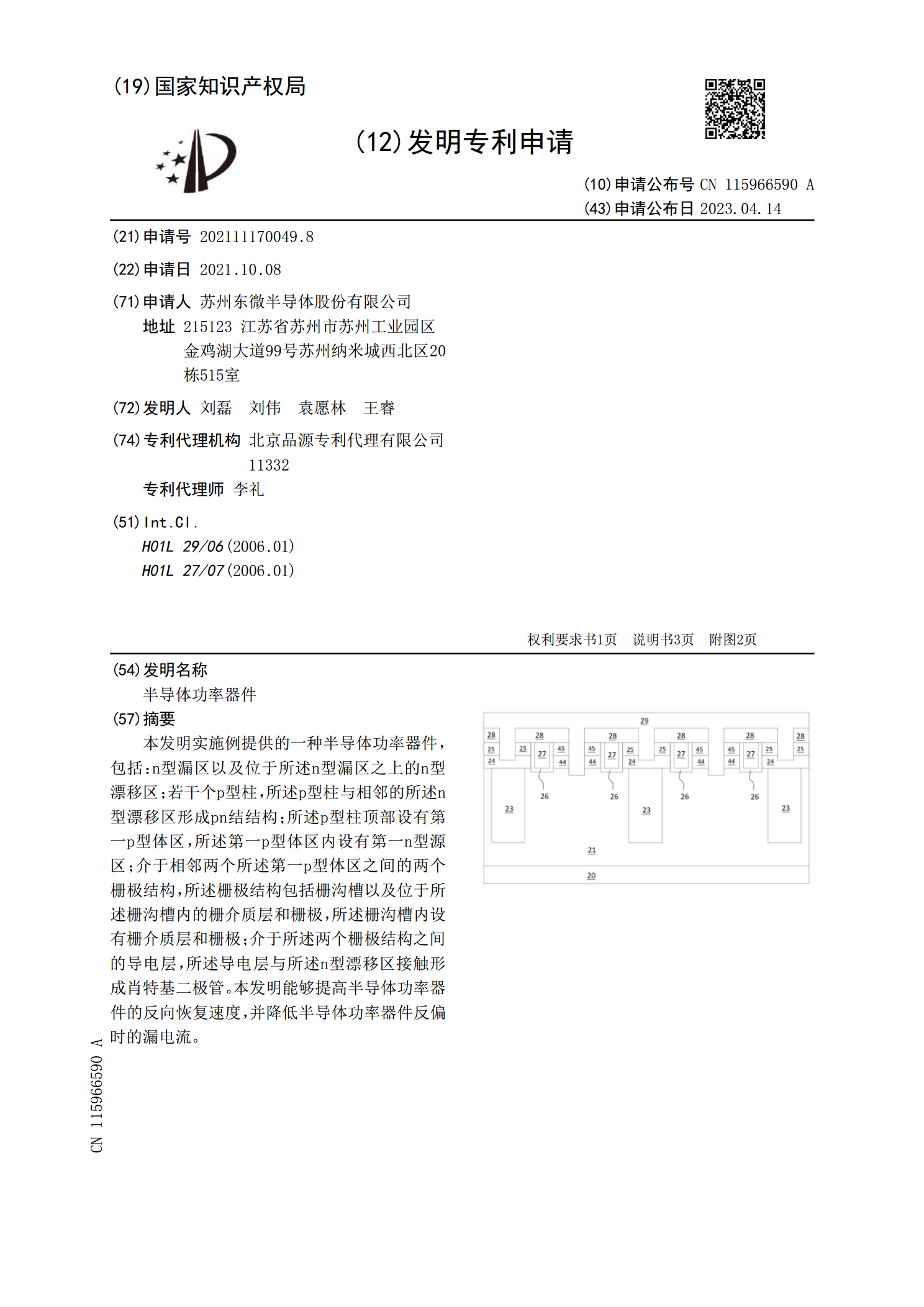

半导体功率器件.pdf

本发明实施例提供的一种半导体功率器件,包括:n型漏区以及位于所述n型漏区之上的n型漂移区;若干个p型柱,所述p型柱与相邻的所述n型漂移区形成pn结结构;所述p型柱顶部设有第一p型体区,所述第一p型体区内设有第一n型源区;介于相邻两个所述第一p型体区之间的两个栅极结构,所述栅极结构包括栅沟槽以及位于所述栅沟槽内的栅介质层和栅极,所述栅沟槽内设有栅介质层和栅极;介于所述两个栅极结构之间的导电层,所述导电层与所述n型漂移区接触形成肖特基二极管。本发明能够提高半导体功率器件的反向恢复速度,并降低半导体功率器件反偏