High-K电容介质刻蚀的方法.pdf

书生****萌哒

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

High-K电容介质刻蚀的方法.pdf

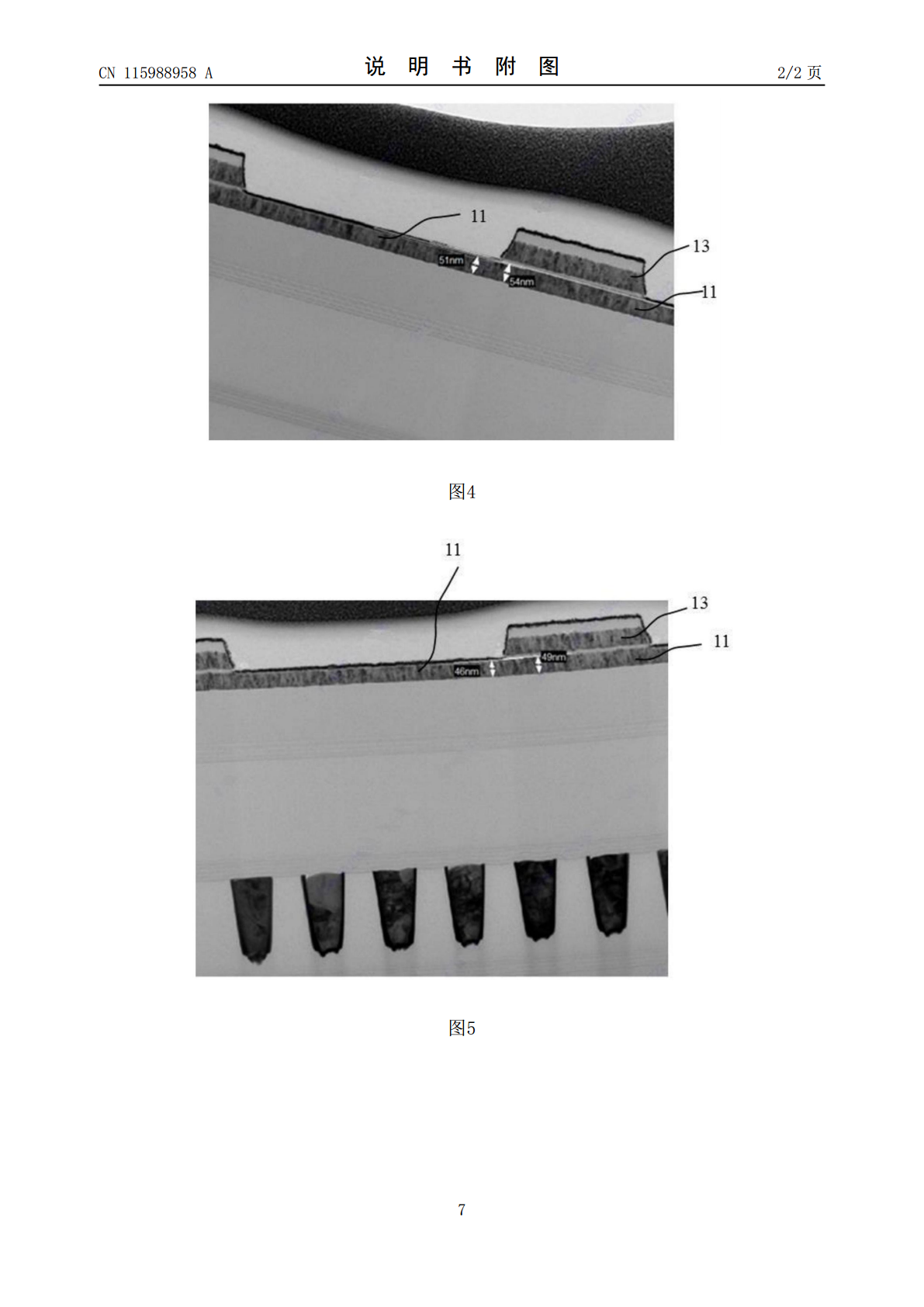

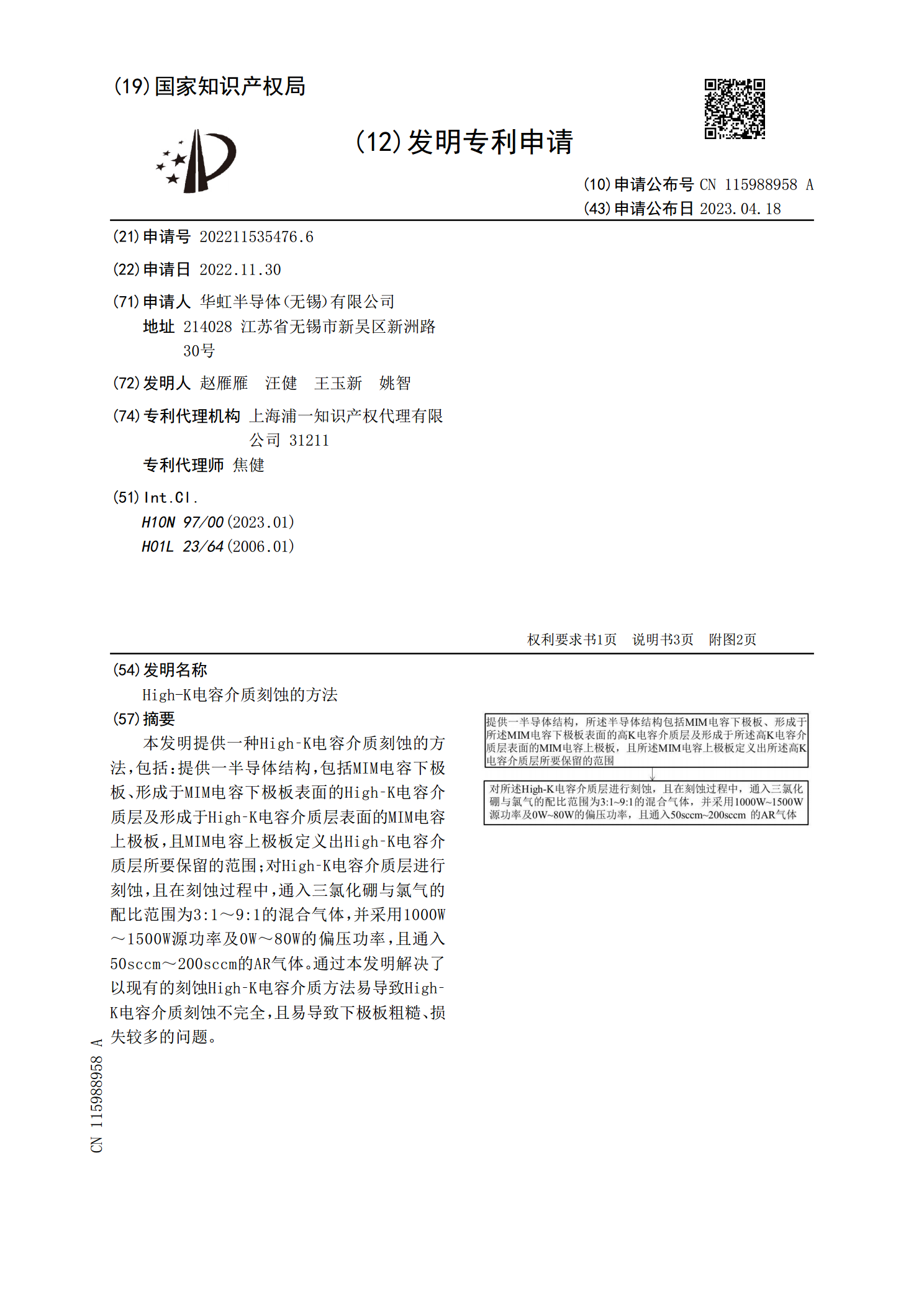

本发明提供一种High‑K电容介质刻蚀的方法,包括:提供一半导体结构,包括MIM电容下极板、形成于MIM电容下极板表面的High‑K电容介质层及形成于High‑K电容介质层表面的MIM电容上极板,且MIM电容上极板定义出High‑K电容介质层所要保留的范围;对High‑K电容介质层进行刻蚀,且在刻蚀过程中,通入三氯化硼与氯气的配比范围为3:1~9:1的混合气体,并采用1000W~1500W源功率及0W~80W的偏压功率,且通入50sccm~200sccm的AR气体。通过本发明解决了以现有的刻蚀High‑K

阻挡介质层的刻蚀方法.pdf

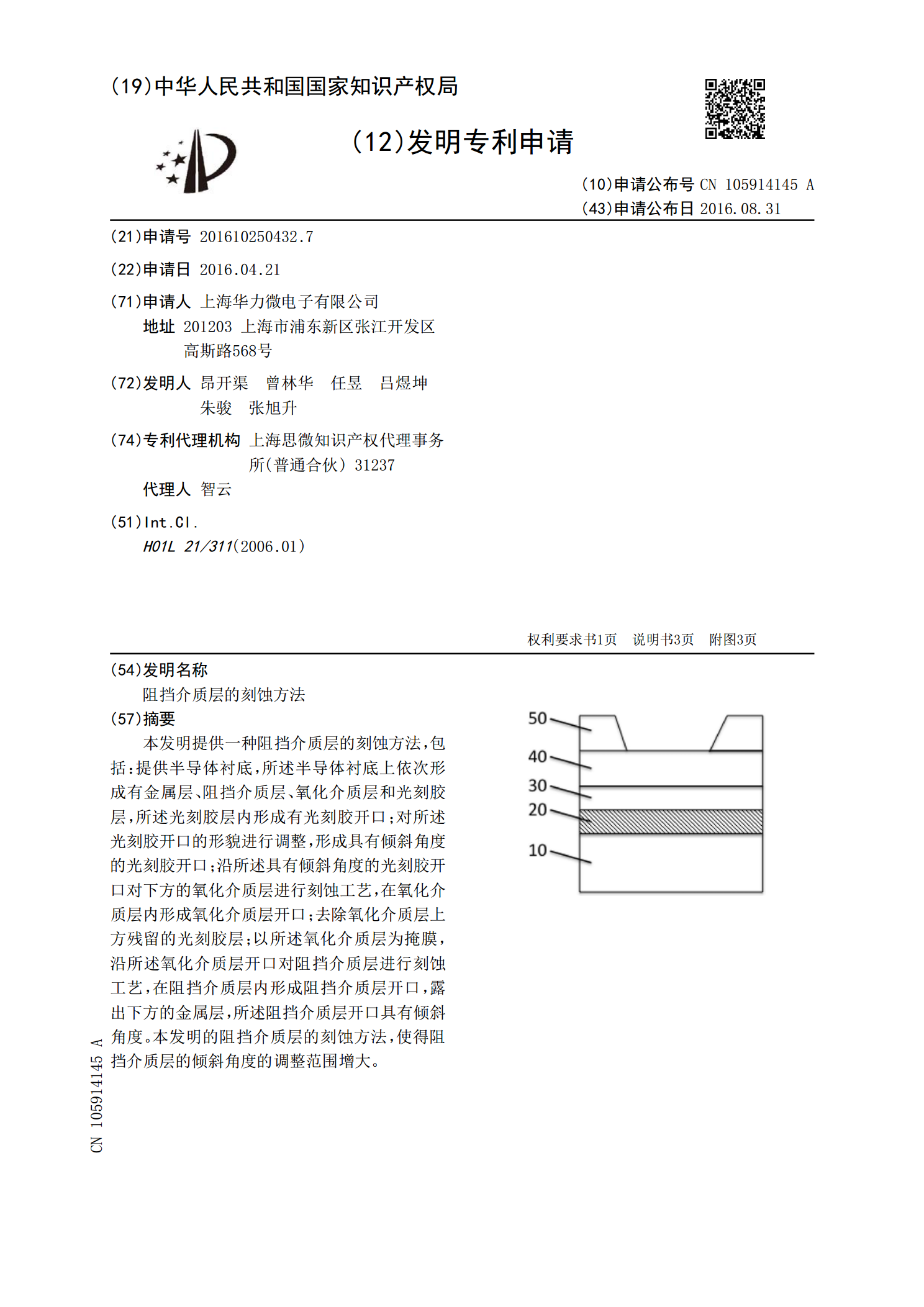

本发明提供一种阻挡介质层的刻蚀方法,包括:提供半导体衬底,所述半导体衬底上依次形成有金属层、阻挡介质层、氧化介质层和光刻胶层,所述光刻胶层内形成有光刻胶开口;对所述光刻胶开口的形貌进行调整,形成具有倾斜角度的光刻胶开口;沿所述具有倾斜角度的光刻胶开口对下方的氧化介质层进行刻蚀工艺,在氧化介质层内形成氧化介质层开口;去除氧化介质层上方残留的光刻胶层;以所述氧化介质层为掩膜,沿所述氧化介质层开口对阻挡介质层进行刻蚀工艺,在阻挡介质层内形成阻挡介质层开口,露出下方的金属层,所述阻挡介质层开口具有倾斜角度。本发明

层间介质层的刻蚀方法.pdf

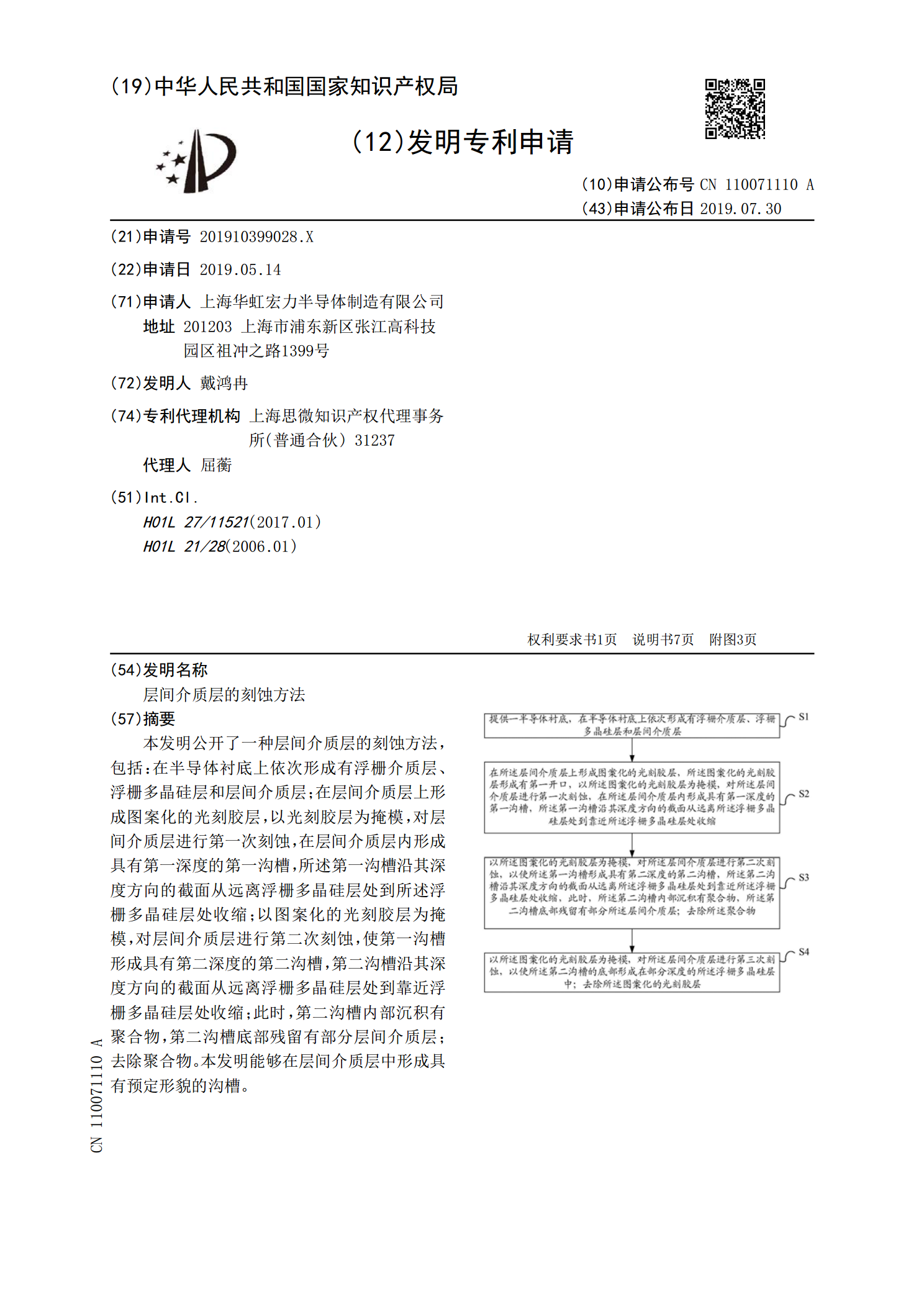

本发明公开了一种层间介质层的刻蚀方法,包括:在半导体衬底上依次形成有浮栅介质层、浮栅多晶硅层和层间介质层;在层间介质层上形成图案化的光刻胶层,以光刻胶层为掩模,对层间介质层进行第一次刻蚀,在层间介质层内形成具有第一深度的第一沟槽,所述第一沟槽沿其深度方向的截面从远离浮栅多晶硅层处到所述浮栅多晶硅层处收缩;以图案化的光刻胶层为掩模,对层间介质层进行第二次刻蚀,使第一沟槽形成具有第二深度的第二沟槽,第二沟槽沿其深度方向的截面从远离浮栅多晶硅层处到靠近浮栅多晶硅层处收缩;此时,第二沟槽内部沉积有聚合物,第二沟槽

电容笔书写方法、电容笔、屏幕及存储介质.pdf

本发明公开了一种电容笔书写方法、电容笔、屏幕以及存储介质,属于智能设备技术领域。该电容笔书写方法包括:获取电容笔的笔尖压力并按照预设周期检测屏幕按照所述预设周期发送的上行信号;当所述笔尖压力高于预设压力阈值且检测到所述上行信号存在异常时,按照预设时序发送多个下行信号至所述屏幕,以使所述屏幕根据所述多个下行信号在对应的多个目标位置显示笔尖的移动轨迹,所述多个目标位置为所述屏幕按照所述预设时序检测到的所述笔尖的接触位置。本申请实现了减少了电容笔书写断线的发生,从而提高电容笔的书写效果。

Highk与Lowk的分析.docx

High-k与Low-k的分析近十年来CPU业者每发表1款新主打CPU,就会顺带标榜该芯片所用的制程技术,最初只标榜尺寸缩密性制程,而近五年来更是强调各种新材质性制程,倘若不去了解新材质制程的意义,那么也将愈来愈不了解新CPU的价值意义……过去IBM微电子发表LowkDielectric(低介电质绝缘,或称:低介电常数绝缘)制程技术时,人们没有投入太多的注目,而今Intel在45nm制程的芯片产品发表后,也连带在45nm制程内使用了Highk/MetalGate(高介电质金属闸极)技术,使的最近笔者经常被