一种半导体器件及其制造方法.pdf

佳宁****么啦

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体器件及其制造方法.pdf

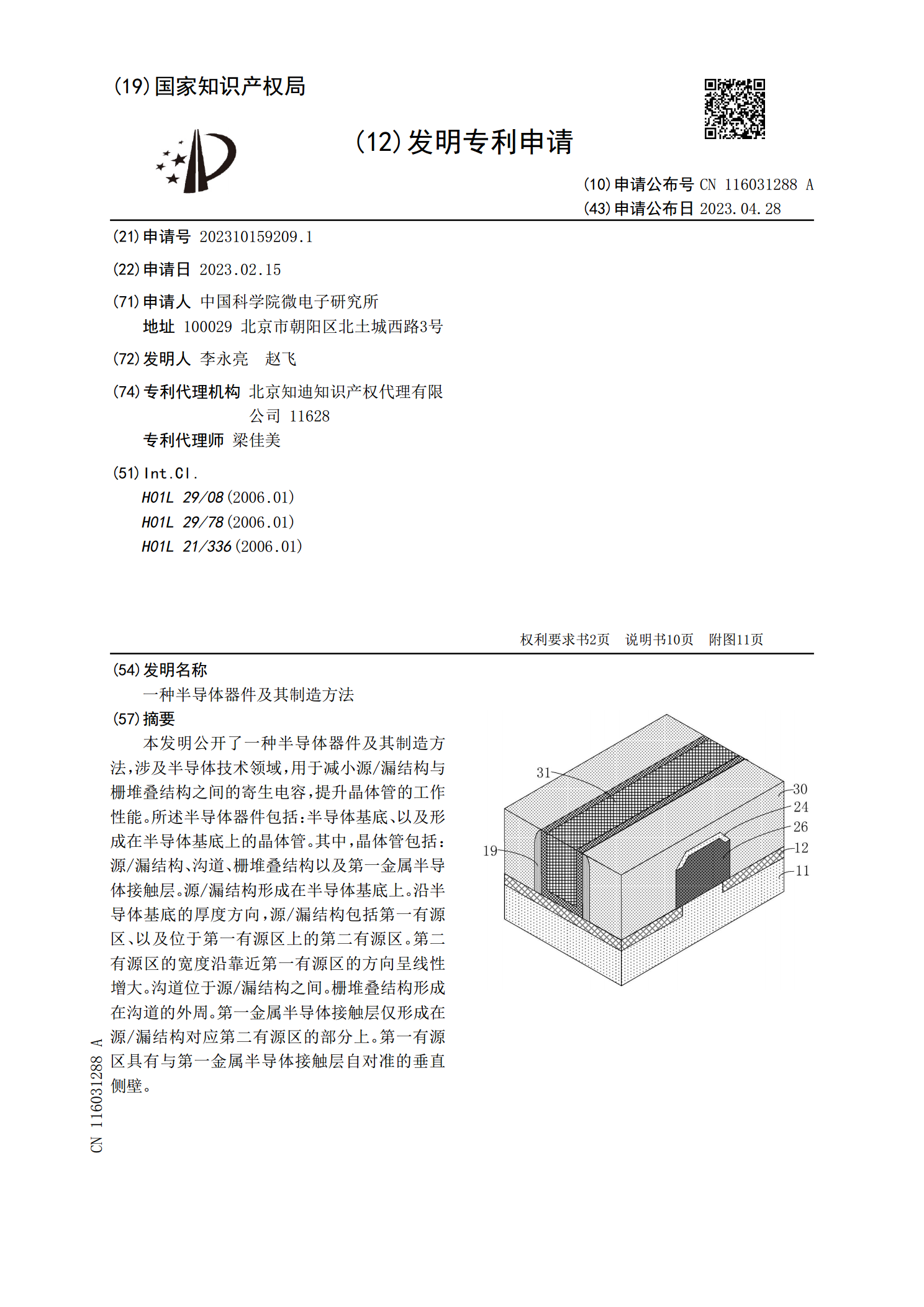

(19)国家知识产权局(12)发明专利申请(10)申请公布号CN116031288A(43)申请公布日2023.04.28(21)申请号202310159209.1(22)申请日2023.02.15(71)申请人中国科学院微电子研究所地址100029北京市朝阳区北土城西路3号(72)发明人李永亮赵飞(74)专利代理机构北京知迪知识产权代理有限公司11628专利代理师梁佳美(51)Int.Cl.H01L29/08(2006.01)H01L29/78(2006.01)H01L21/336(2006.01)权利

一种半导体器件及其制造方法.pdf

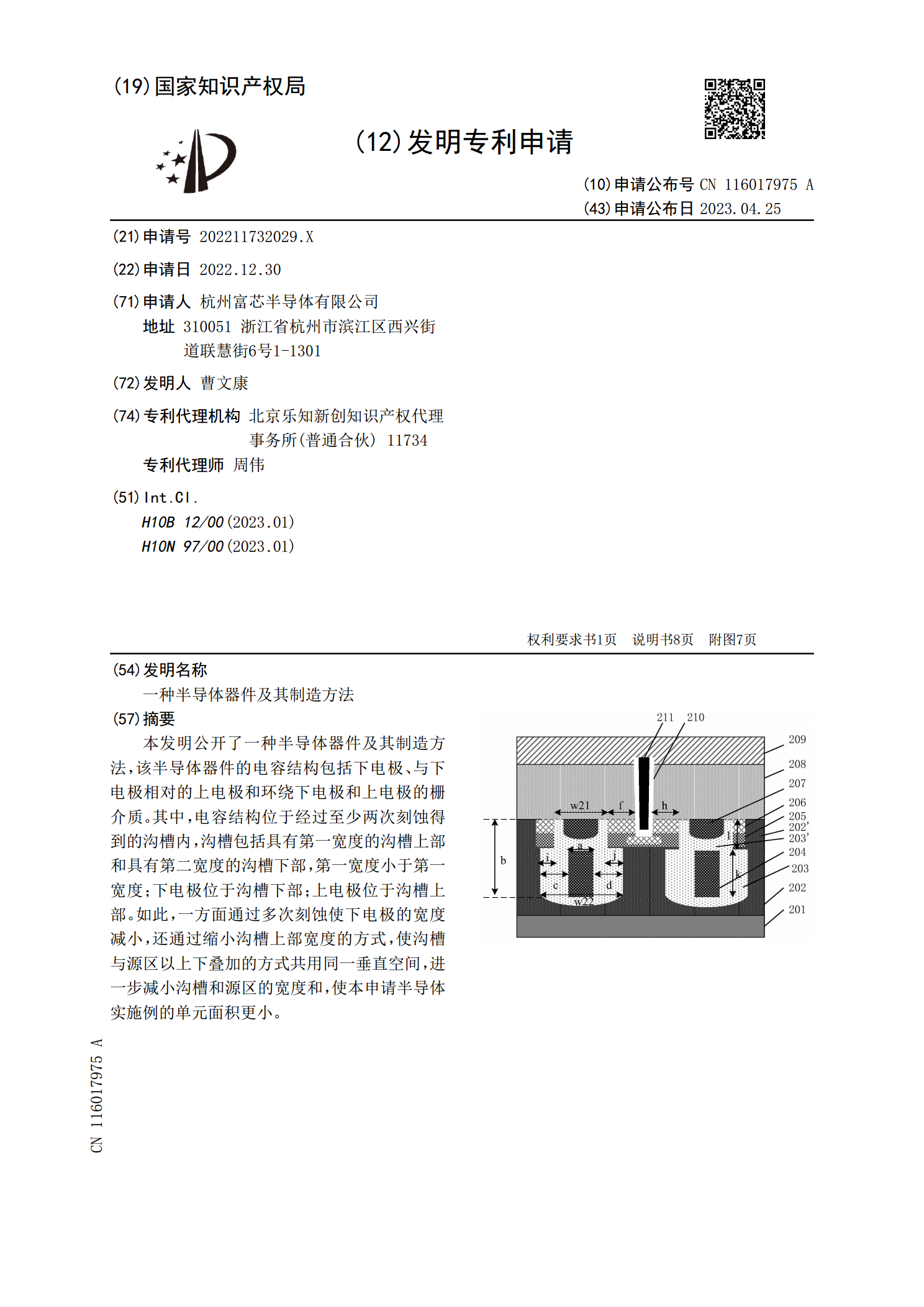

本发明公开了一种半导体器件及其制造方法,该半导体器件的电容结构包括下电极、与下电极相对的上电极和环绕下电极和上电极的栅介质。其中,电容结构位于经过至少两次刻蚀得到的沟槽内,沟槽包括具有第一宽度的沟槽上部和具有第二宽度的沟槽下部,第一宽度小于第一宽度;下电极位于沟槽下部;上电极位于沟槽上部。如此,一方面通过多次刻蚀使下电极的宽度减小,还通过缩小沟槽上部宽度的方式,使沟槽与源区以上下叠加的方式共用同一垂直空间,进一步减小沟槽和源区的宽度和,使本申请半导体实施例的单元面积更小。

一种半导体器件及其制造方法.pdf

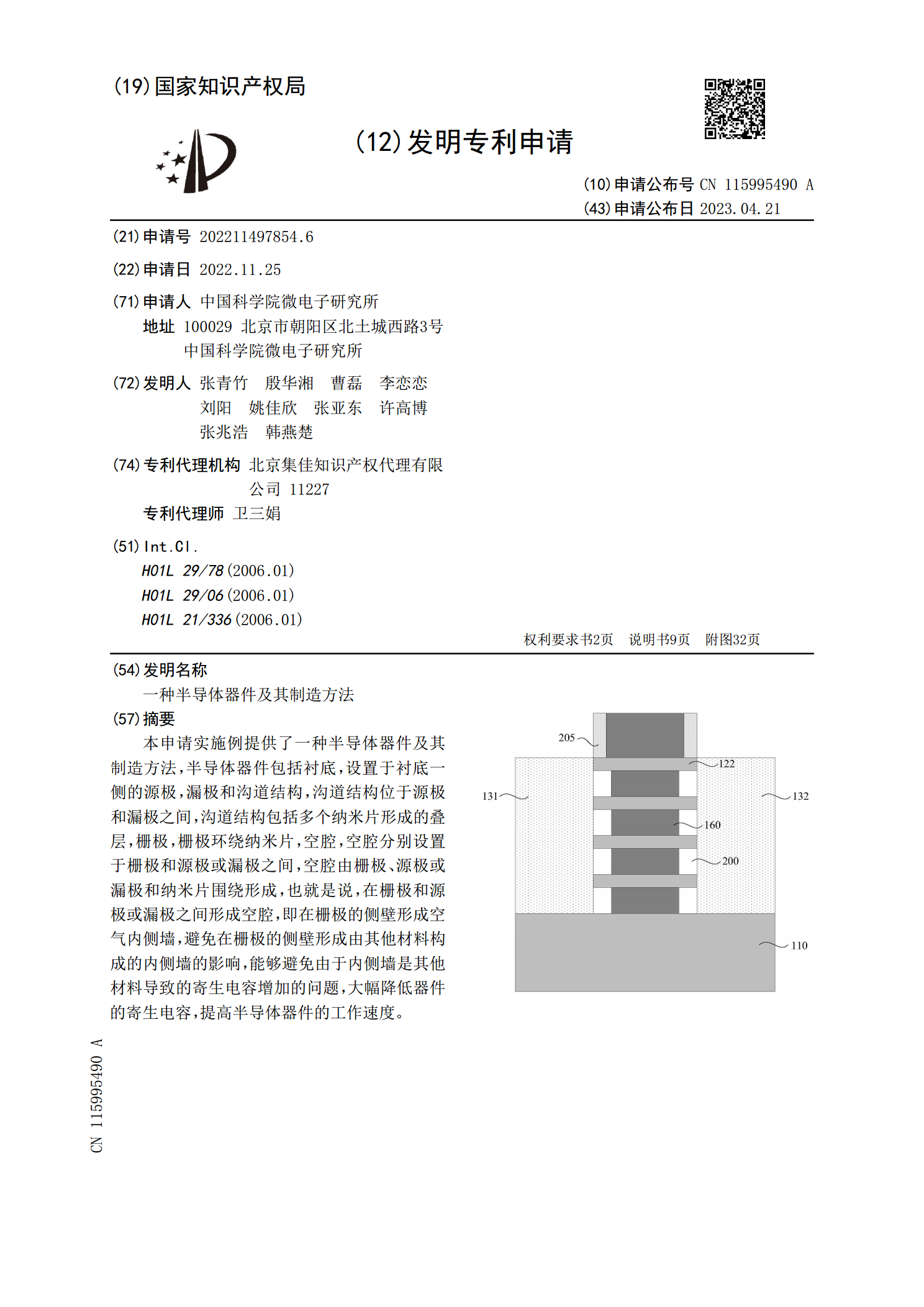

本申请实施例提供了一种半导体器件及其制造方法,半导体器件包括衬底,设置于衬底一侧的源极,漏极和沟道结构,沟道结构位于源极和漏极之间,沟道结构包括多个纳米片形成的叠层,栅极,栅极环绕纳米片,空腔,空腔分别设置于栅极和源极或漏极之间,空腔由栅极、源极或漏极和纳米片围绕形成,也就是说,在栅极和源极或漏极之间形成空腔,即在栅极的侧壁形成空气内侧墙,避免在栅极的侧壁形成由其他材料构成的内侧墙的影响,能够避免由于内侧墙是其他材料导致的寄生电容增加的问题,大幅降低器件的寄生电容,提高半导体器件的工作速度。

一种半导体器件及其制造方法.pdf

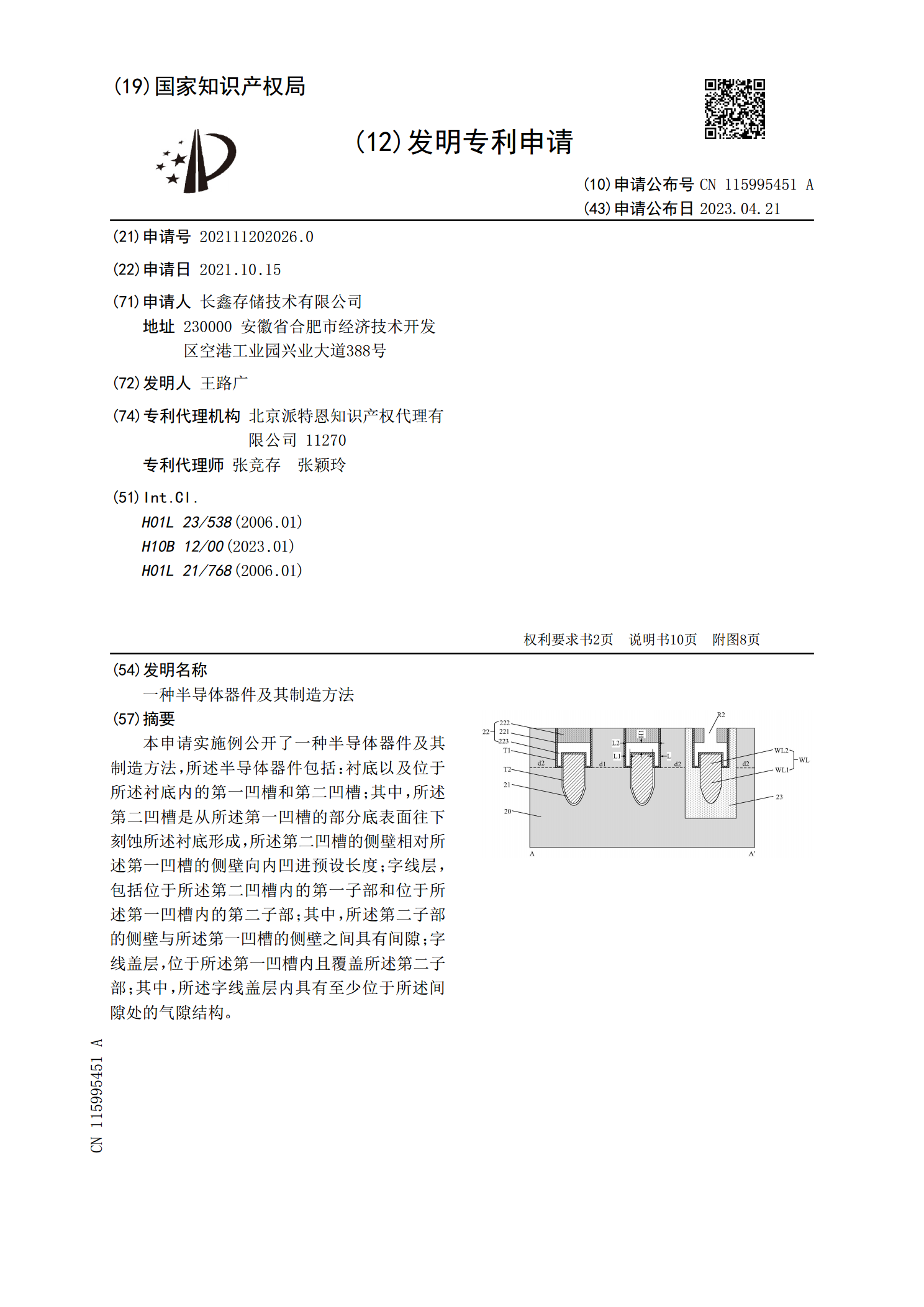

本申请实施例公开了一种半导体器件及其制造方法,所述半导体器件包括:衬底以及位于所述衬底内的第一凹槽和第二凹槽;其中,所述第二凹槽是从所述第一凹槽的部分底表面往下刻蚀所述衬底形成,所述第二凹槽的侧壁相对所述第一凹槽的侧壁向内凹进预设长度;字线层,包括位于所述第二凹槽内的第一子部和位于所述第一凹槽内的第二子部;其中,所述第二子部的侧壁与所述第一凹槽的侧壁之间具有间隙;字线盖层,位于所述第一凹槽内且覆盖所述第二子部;其中,所述字线盖层内具有至少位于所述间隙处的气隙结构。

一种半导体器件及其制造方法.pdf

本申请实施例提供了一种半导体器件及其制造方法,半导体器件包括衬底,设置于衬底一侧的源极,漏极和沟道结构,沟道结构位于源极和漏极之间,沟道结构包括多个纳米片形成的叠层,栅极,栅极环绕纳米片,空腔,空腔至少位于沟道结构和衬底之间,空腔由沟道结构、源极、漏极和衬底围绕形成,也就是说,沟道结构、源极和漏极下方为空腔,没有接触的膜层,构成了全浮空结构,可以大幅改善半导体器件的栅控性能,减小半导体器件亚阈值摆幅、降低漏电流和寄生电容,增加驱动电流,提高半导体器件的性能。