一种半导体器件及其制造方法.pdf

努力****采萍

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种半导体器件及其制造方法.pdf

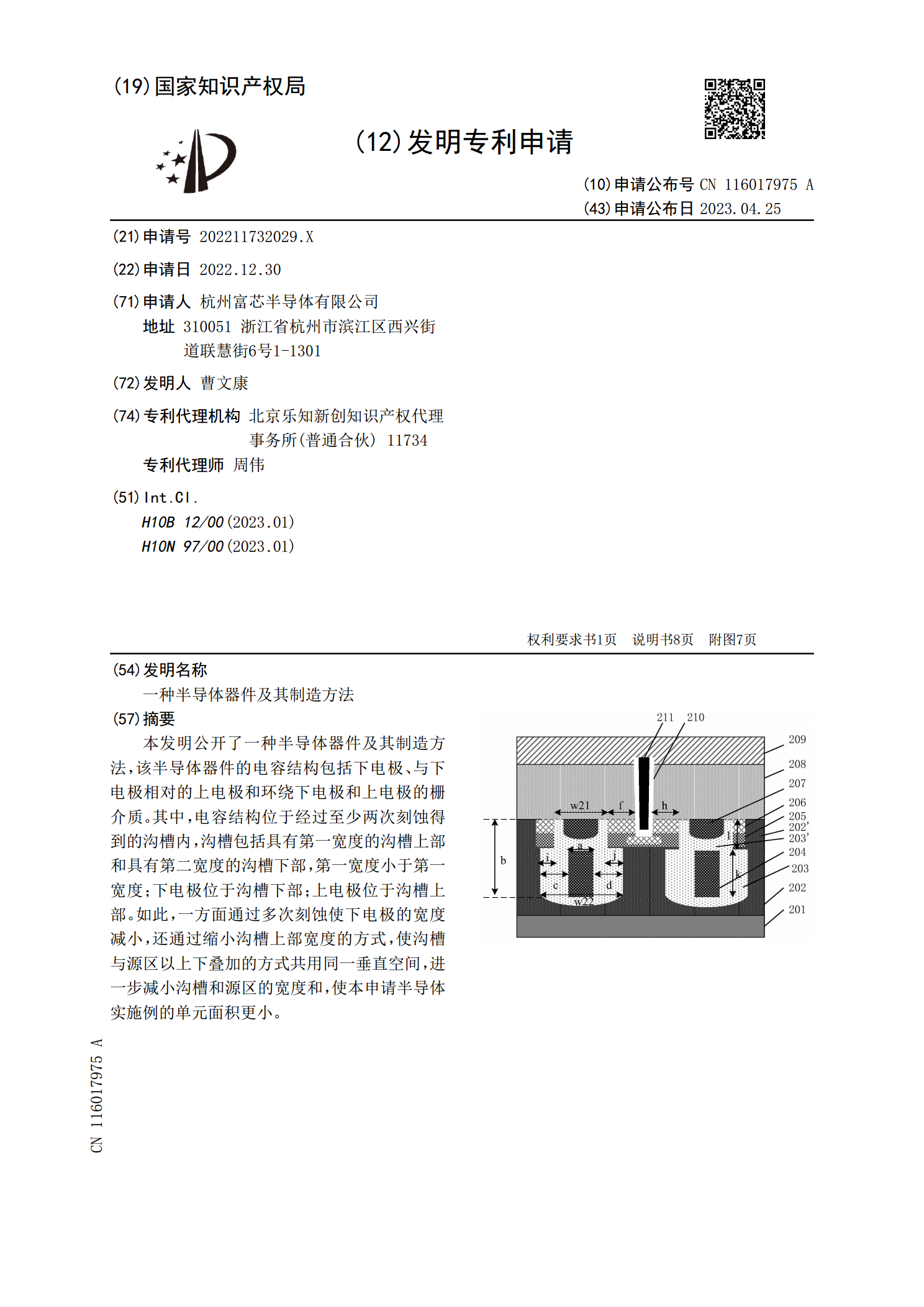

本发明公开了一种半导体器件及其制造方法,该半导体器件的电容结构包括下电极、与下电极相对的上电极和环绕下电极和上电极的栅介质。其中,电容结构位于经过至少两次刻蚀得到的沟槽内,沟槽包括具有第一宽度的沟槽上部和具有第二宽度的沟槽下部,第一宽度小于第一宽度;下电极位于沟槽下部;上电极位于沟槽上部。如此,一方面通过多次刻蚀使下电极的宽度减小,还通过缩小沟槽上部宽度的方式,使沟槽与源区以上下叠加的方式共用同一垂直空间,进一步减小沟槽和源区的宽度和,使本申请半导体实施例的单元面积更小。

一种半导体器件及其制造方法.pdf

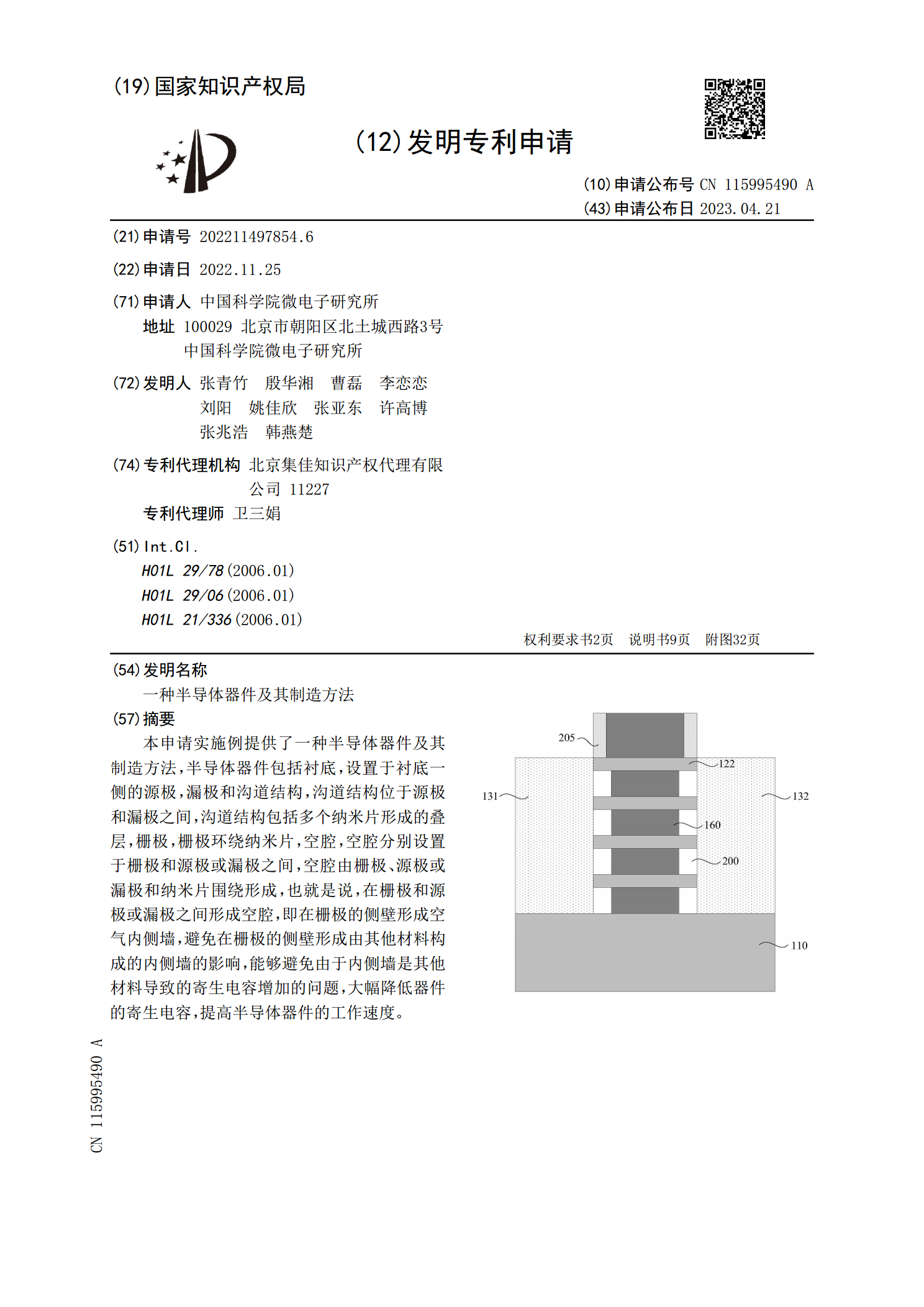

本申请实施例提供了一种半导体器件及其制造方法,半导体器件包括衬底,设置于衬底一侧的源极,漏极和沟道结构,沟道结构位于源极和漏极之间,沟道结构包括多个纳米片形成的叠层,栅极,栅极环绕纳米片,空腔,空腔分别设置于栅极和源极或漏极之间,空腔由栅极、源极或漏极和纳米片围绕形成,也就是说,在栅极和源极或漏极之间形成空腔,即在栅极的侧壁形成空气内侧墙,避免在栅极的侧壁形成由其他材料构成的内侧墙的影响,能够避免由于内侧墙是其他材料导致的寄生电容增加的问题,大幅降低器件的寄生电容,提高半导体器件的工作速度。

一种半导体器件及其制造方法.pdf

本申请实施例提供了一种半导体器件及其制造方法,半导体器件包括衬底,设置于衬底一侧的源极,漏极和沟道结构,沟道结构位于源极和漏极之间,沟道结构包括多个纳米片形成的叠层,栅极,栅极环绕纳米片,空腔,空腔至少位于沟道结构和衬底之间,空腔由沟道结构、源极、漏极和衬底围绕形成,也就是说,沟道结构、源极和漏极下方为空腔,没有接触的膜层,构成了全浮空结构,可以大幅改善半导体器件的栅控性能,减小半导体器件亚阈值摆幅、降低漏电流和寄生电容,增加驱动电流,提高半导体器件的性能。

一种半导体器件及其制造方法.pdf

本发明公开了一种半导体器件及其制造方法,包括:在金属衬底的存储区域依次沉积第一阻挡层和第一介电层;在存储区域的第一阻挡层和第一介电层中刻蚀出第一通孔,在第一通孔中沉积下电极,进行平坦化处理以使下电极的上表面和第一介电层的上表面平齐;在存储区域的第一介电层和下电极的表面依次沉积阻变层和第二阻挡层;在存储区域的第二阻挡层上沉积第二介电层;在存储区域的阻变层之上的各层中刻蚀出连通的第二通孔和线槽,所述第二通孔的底部与所述阻变层连通,所述第二通孔的顶部与所述线槽连通;在所述第二通孔和线槽中依次沉积抓氧层和上电极后

一种半导体器件及其制造方法.pdf

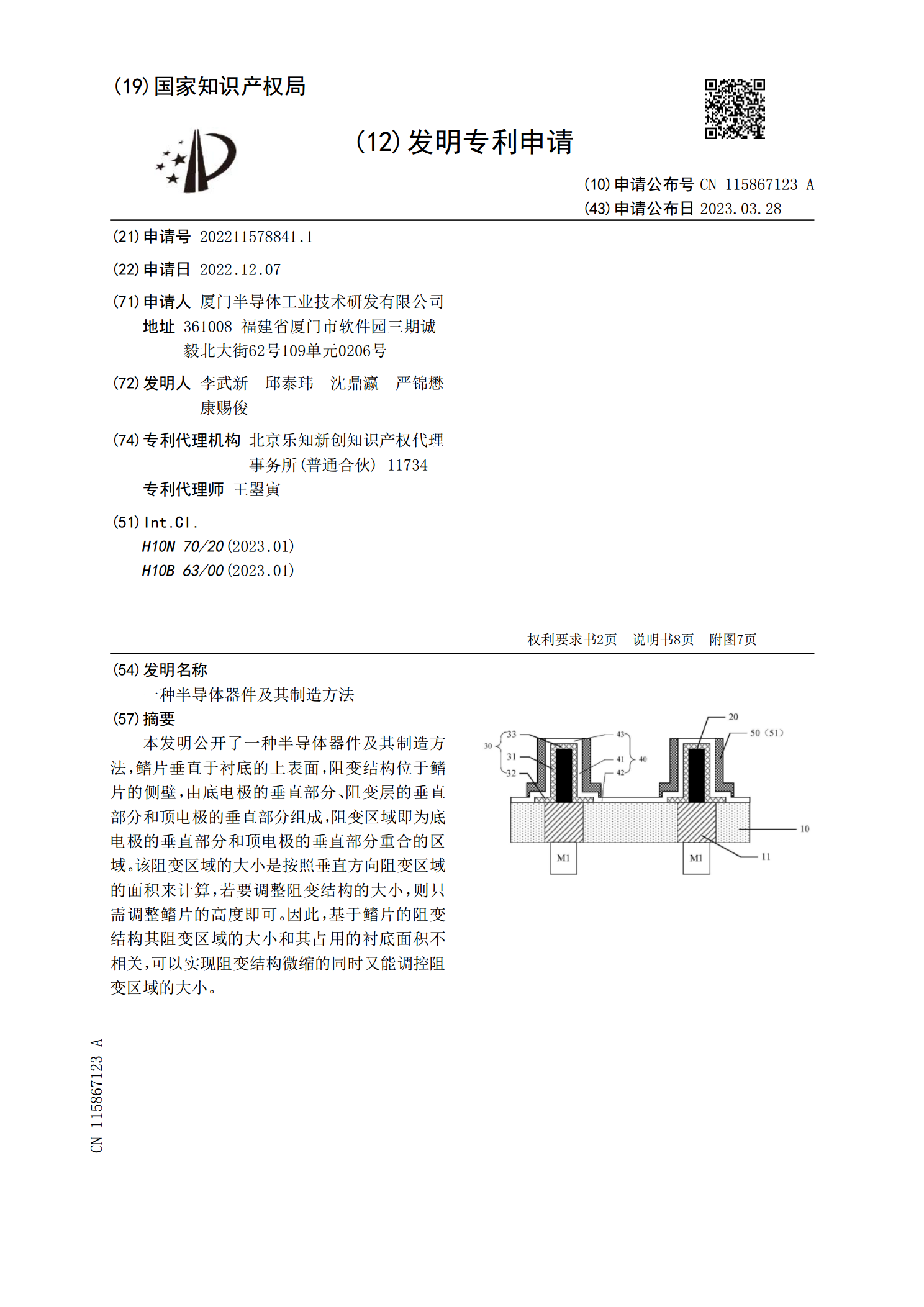

本发明公开了一种半导体器件及其制造方法,鳍片垂直于衬底的上表面,阻变结构位于鳍片的侧壁,由底电极的垂直部分、阻变层的垂直部分和顶电极的垂直部分组成,阻变区域即为底电极的垂直部分和顶电极的垂直部分重合的区域。该阻变区域的大小是按照垂直方向阻变区域的面积来计算,若要调整阻变结构的大小,则只需调整鳍片的高度即可。因此,基于鳍片的阻变结构其阻变区域的大小和其占用的衬底面积不相关,可以实现阻变结构微缩的同时又能调控阻变区域的大小。