一种基于n型导电SiC衬底的GaN完全垂直型电子器件及其制备方法.pdf

波峻****99

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种基于n型导电SiC衬底的GaN完全垂直型电子器件及其制备方法.pdf

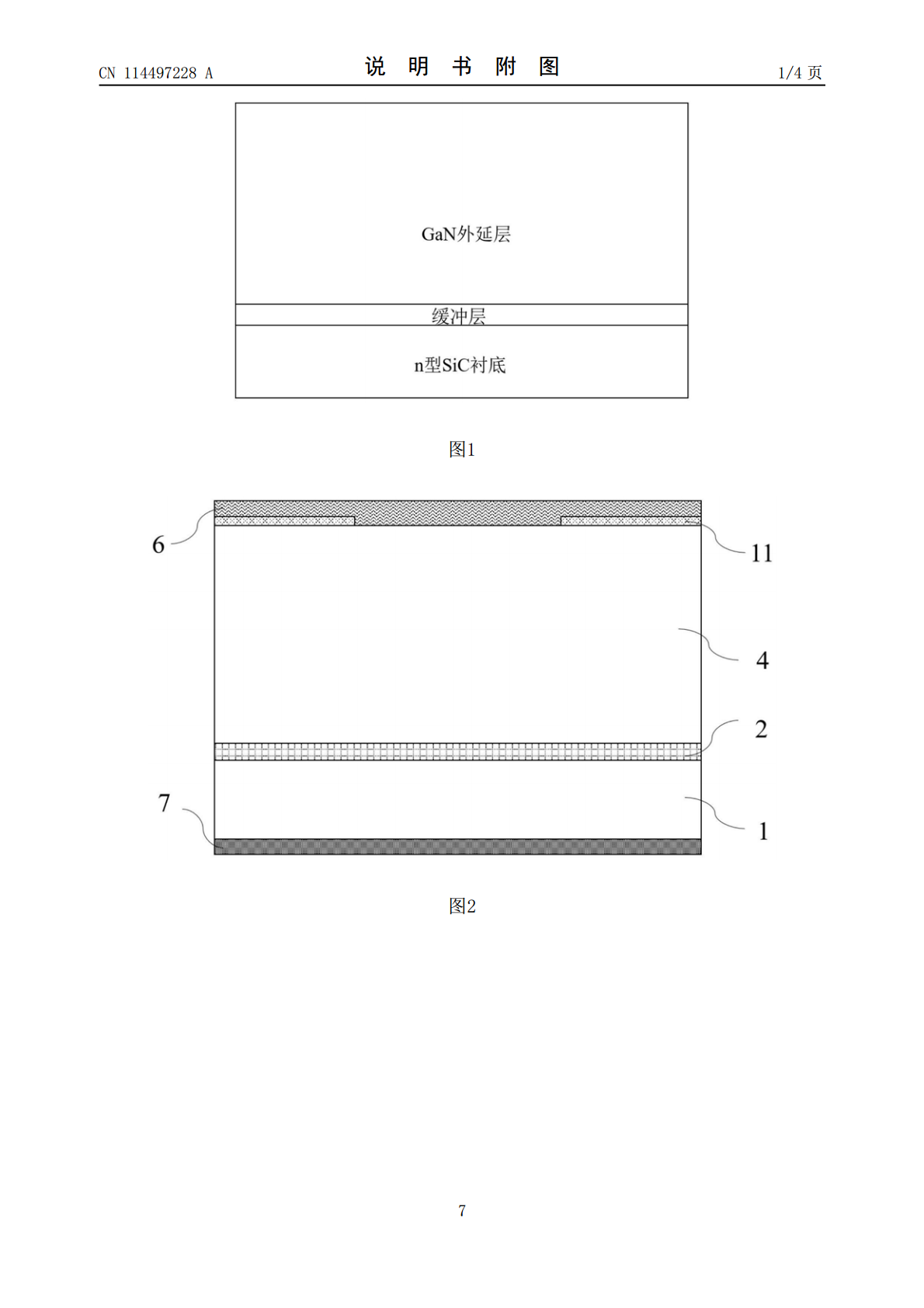

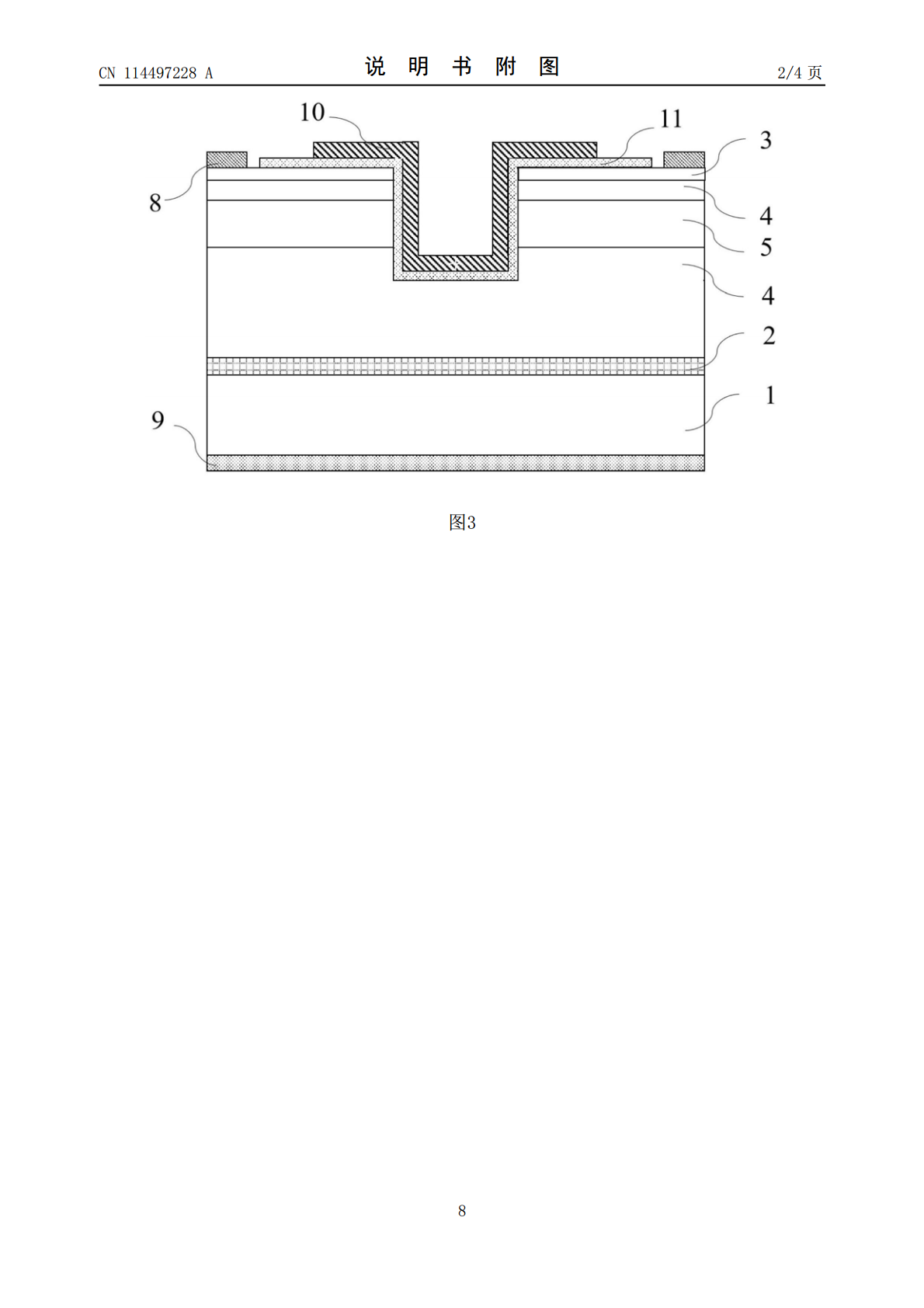

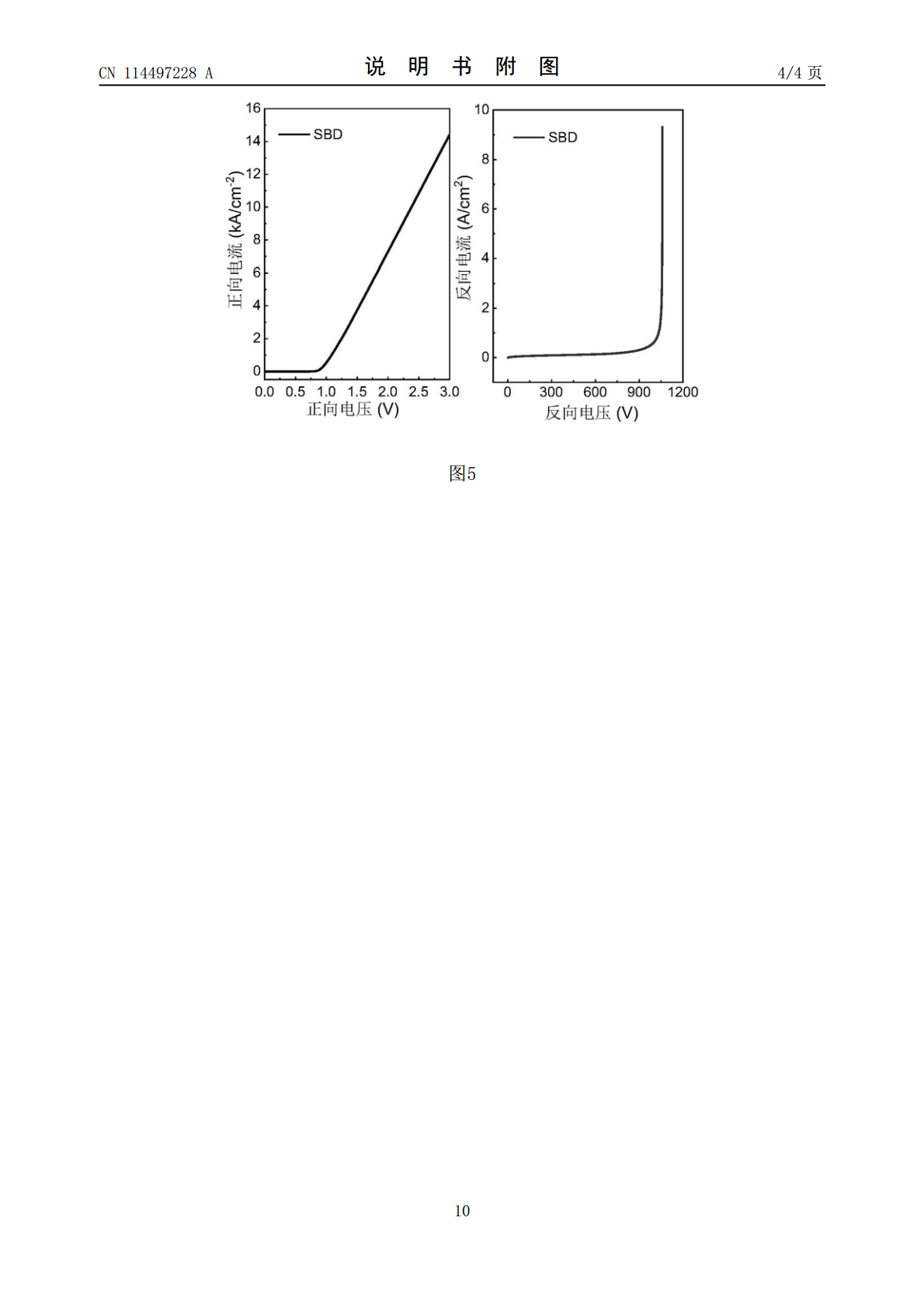

本发明涉及一种基于n型导电SiC衬底的GaN完全垂直型电子器件及其制备方法,从下至上依次包括漏极或阴极、n型导电SiC衬底、导电缓冲层、厚GaN外延层、源极或阳极;厚GaN外延层的厚度为1~100μm;本发明通过在n型导电SiC衬底上开发了导电缓冲层,在导电缓冲层通过外延生长,获得了无裂纹的厚GaN外延层,进而得到完全垂直型的GaN电子器件,改善了准垂直型器件的电流和电场拥挤的问题,静态电学性能优异,拥有良好的正反向电学特性;同时由于GaN比SiC材料的优势,本发明的完全垂直型的GaN电子器件性能更优,同

一种N型电池导电银浆及其制备方法.pdf

本发明公开了一种N型电池导电银浆及其制备方法,通过在银浆中引入了自制的双金属AlPb‑MOF材料,该双金属AlPb‑MOF材料的柔性多孔结构使银浆具有良好的印刷性能,在印刷烧结时MOF有机材料被烧尽后残留的铅、铝均匀混合,同时由于铅是重金属且具有较低的熔点,因此铅可以将质地轻的铝熔融带入至晶硅表面进而形成良好的欧姆接触,此外铅润湿性好,还可以使铝均匀地分布在晶硅表面获得良好的开路电压。本发明的电池导电银浆具有组分简单、易于获取、印刷性能优良、线型完美、导电性能优异等优点。

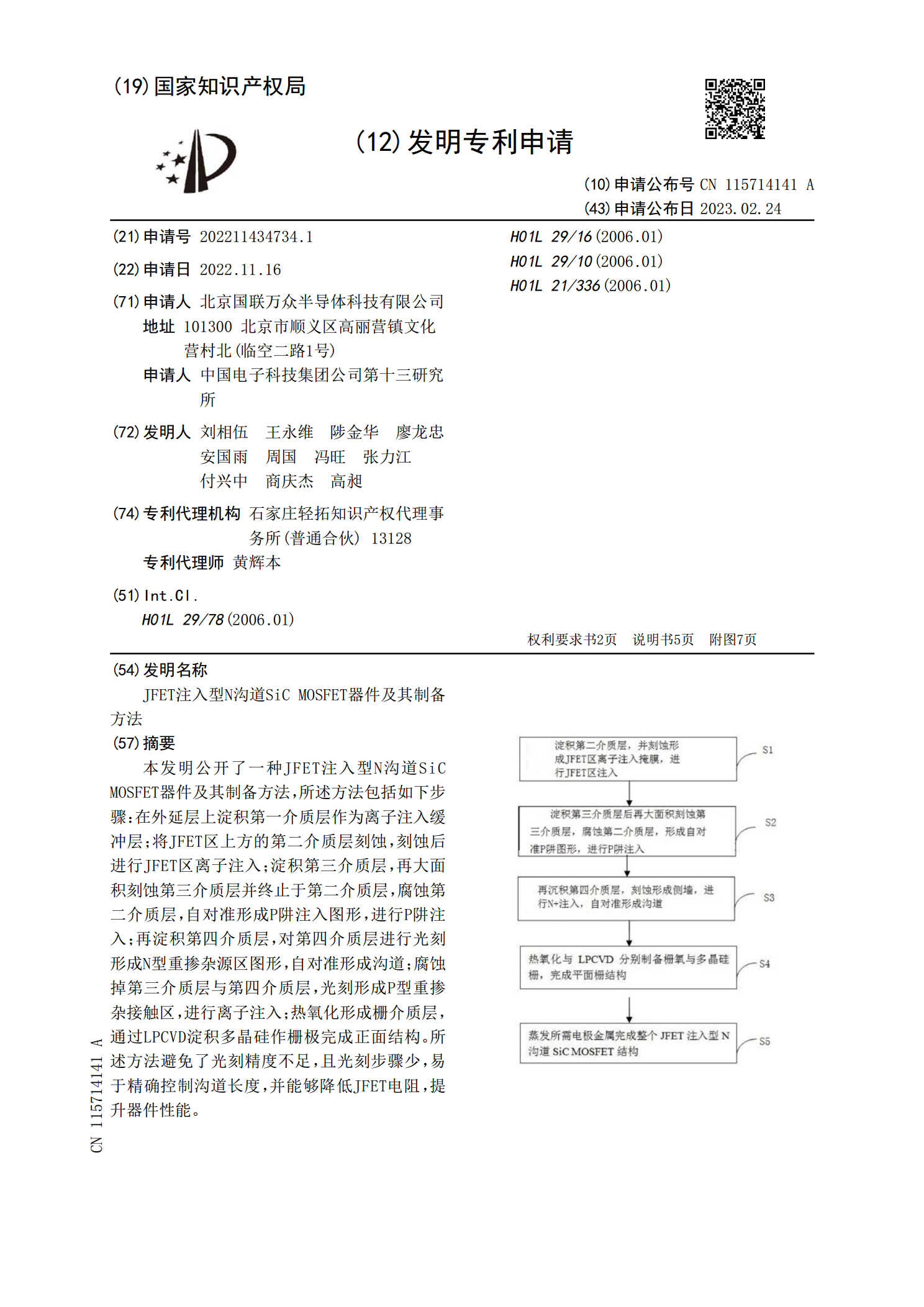

JFET注入型N沟道SiC MOSFET器件及其制备方法.pdf

本发明公开了一种JFET注入型N沟道SiCMOSFET器件及其制备方法,所述方法包括如下步骤:在外延层上淀积第一介质层作为离子注入缓冲层;将JFET区上方的第二介质层刻蚀,刻蚀后进行JFET区离子注入;淀积第三介质层,再大面积刻蚀第三介质层并终止于第二介质层,腐蚀第二介质层,自对准形成P阱注入图形,进行P阱注入;再淀积第四介质层,对第四介质层进行光刻形成N型重掺杂源区图形,自对准形成沟道;腐蚀掉第三介质层与第四介质层,光刻形成P型重掺杂接触区,进行离子注入;热氧化形成栅介质层,通过LPCVD淀积多晶硅作栅

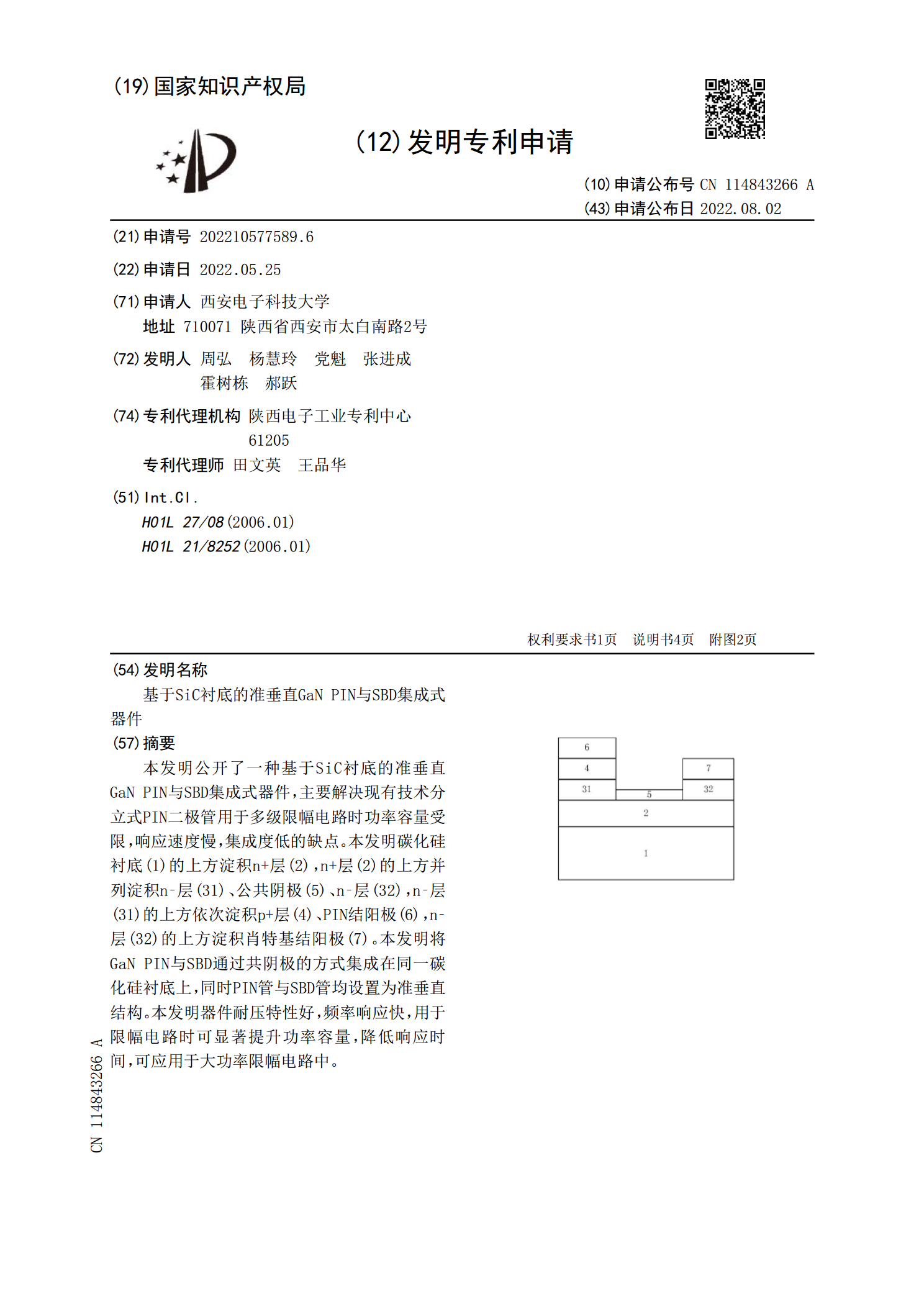

基于SiC衬底的准垂直GaN PIN与SBD集成式器件.pdf

本发明公开了一种基于SiC衬底的准垂直GaNPIN与SBD集成式器件,主要解决现有技术分立式PIN二极管用于多级限幅电路时功率容量受限,响应速度慢,集成度低的缺点。本发明碳化硅衬底(1)的上方淀积n+层(2),n+层(2)的上方并列淀积n?层(31)、公共阴极(5)、n?层(32),n?层(31)的上方依次淀积p+层(4)、PIN结阳极(6),n?层(32)的上方淀积肖特基结阳极(7)。本发明将GaNPIN与SBD通过共阴极的方式集成在同一碳化硅衬底上,同时PIN管与SBD管均设置为准垂直结构。本发明器件

用于制备n型SiC单晶的方法.pdf

本发明提供一种用于制备n型SiC单晶的方法,其包括以下步骤:(1)将助熔剂置于石墨坩埚中,并且将SiC籽晶固定在石墨坩埚上方的提拉杆上;(2)将所述石墨坩埚置于生长炉中,然后对所述生长炉抽真空;(3)加热石墨坩埚至所述助熔剂完全熔化以形成熔体,通入包含氮气的混合气体以控制生长炉内的气压并保持恒定的氮气分压;(4)下推提拉杆使得所述籽晶与熔体接触,进而生长n型SiC单晶。本发明的方法能够有效地通过液相法生长出高质量的、掺杂均匀的n型SiC单晶,而且能够实现氮掺杂浓度的大范围精确调控。同时,该方法还具有生长温