基于FPGA的IP核设计技术.pptx

胜利****实阿

亲,该文档总共64页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于FPGA的IP核设计技术.pptx

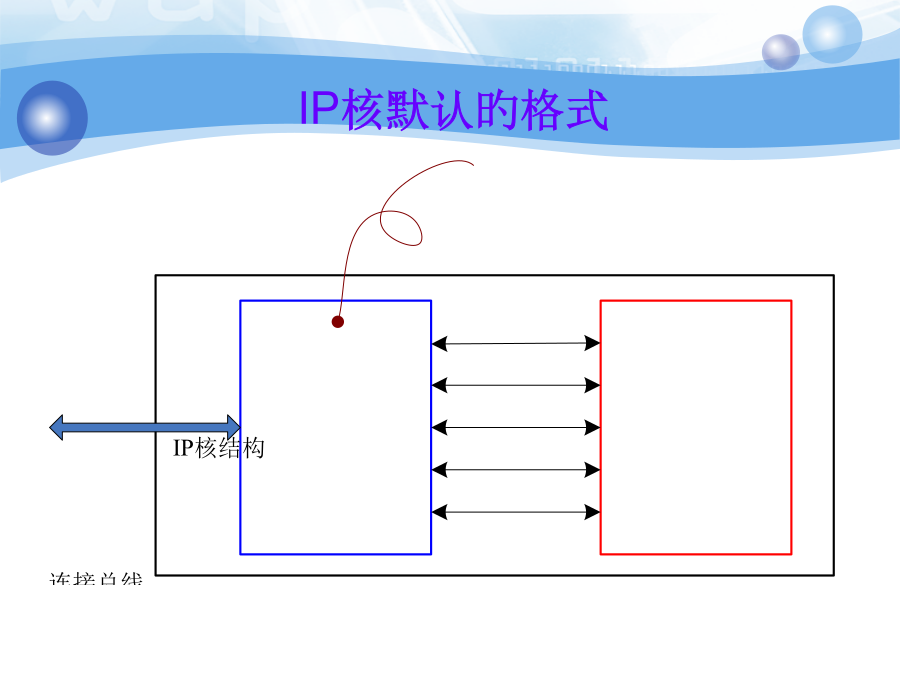

基于FPGA旳IP核设计技术IP核旳概念IP设计技术概述软核(SoftCore)固核(FirmCore)硬核(HardCore)IP设计与复用IP设计与复用IP核默认旳格式Altera企业旳Avalon总线Avalon-MM总线构造图回忆试验四:导入自定义IP核IP核阐明Altera能够提供给顾客使用旳3种IP形式:基本宏功能(Megafunctions/LPM)AlteraIP(MegaCore)AlteraIP合作伙伴(AMPP)旳IPAltera旳IP核AlteraIP在设计中旳作用在使用Alter

基于FPGA的IIS IP核设计.docx

基于FPGA的IISIP核设计IntroductionInrecentyears,thedevelopmentofdigitalsignalprocessingtechnologyhasbroughtgreatconveniencetopeople'slives.Atthesametime,theimprovementofdigitalsignalprocessingtechnologyalsoprovidesasolidfoundationforthedevelopmentofartificialint

基于FPGA的8051 IP核的设计与应用.docx

基于FPGA的8051IP核的设计与应用随着计算机的快速发展,嵌入式系统的需求也在不断增加,这就要求嵌入式系统的硬件设计具有更高的性能和更小的体积。因此,基于FPGA的8051IP核的设计与应用成为了现在嵌入式系统设计的热点之一。1.8051IP核的设计8051是一款典型的8位单片机微处理器,它功能强大,使用广泛。在传统的8051芯片上,它的时钟频率是12MHz,而且引脚数目相对较多。但是,在基于FPGA的8051IP核上,通过优化设计,可以将其时钟频率提高到50MHz以上,并且只需要少量的引脚。其主要优

基于FPGA的DDS IP核的研究与设计.docx

基于FPGA的DDSIP核的研究与设计摘要频率合成技术在现代通信系统中的应用越来越广泛,而数字频率合成器(DDS)作为其中一种较为成熟的实现方式,也受到了业界的广泛关注。本文主要介绍了基于FPGA的DDSIP核的研究与设计,包括了DDS的基本原理、传统实现方式的缺陷以及FPGA实现DDS的优势。同时,本文还介绍了DDSIP核的基本结构和核心部件的设计思路,并对设计的结果进行了验证和实现。实验结果表明,所设计的DDSIP核能够输出丰富的频率波形,并具备较高的频率精度和稳定性。本研究对于FPGA实现DDS技术

基于FPGA的UART IP核的设计实现.docx

基于FPGA的UARTIP核的设计实现IntroductionUniversalAsynchronousReceiver/Transmitter(UART)isawidelyusedcommunicationprotocolinembeddedsystems.Itprovidesasimpleandefficientwaytotransmitandreceivedatabetweentwodevices.FieldProgrammableGateArrays(FPGAs)arebecomingmorean