基于SOPC的实时图像存储系统的设计.docx

胜利****实阿

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

基于SOPC的实时图像存储系统的设计.docx

基于SOPC的实时图像存储系统的设计聂孟庆余愚摘要:基于目前实时图像存储的解决方案研究的现状与发展趋势,本文研究了基于SOPC技术的实时图像存储设计方案。使用ALTERA公司的NiosII软核处理器作为总控制器,采用CCD传感器加ADV7181B视频解码芯片进行实时图像数据采集,SDRAM用来存放实时图像数据与程序,VGA控制器控制实时图像显示。关键词:片上可编程系统;实时图像;视频解码;同步动态随机存储器1引言随着高速图像处理技术的应用领域不断扩大,对图像处理速度的要求也越来越高,当前基于软核处理器的图

基于SOPC的实时图像处理系统的设计的中期报告.docx

基于SOPC的实时图像处理系统的设计的中期报告尊敬的指导老师:我是负责基于SOPC的实时图像处理系统的设计的学生,现在向您汇报我们的中期进展情况。在前期的调研和设计阶段,我们已经确定了基于SOPC的实时图像处理系统的技术路线和主要功能模块。我们已经完成了硬件运算核心和外设的选型,包括选择了高性能的FPGA作为处理器,选择了CMOS图像传感器和LCD屏幕作为输入和输出设备,选择了SDRAM作为存储设备,以及选择了各种外设模块来支持图像采集、存储、显示、传输等功能。在实现方面,我们已经完成了基于Verilog

基于SOPC的实时红外图像采集处理系统设计的开题报告.docx

基于SOPC的实时红外图像采集处理系统设计的开题报告一、课题背景及研究意义红外成像技术是一种非接触式的无损检测技术,其具有无辐射、防干扰等特点,已广泛应用于工业、医疗、军事等领域。随着红外成像技术的不断发展和进步,其应用领域也越来越广泛,要求更高的实时性和精度,如红外成像系统的鲁棒性、识别率、速度等方面需要得到进一步提高。因此,设计一种基于SOPC的实时红外图像采集处理系统,不仅是提高传统红外成像系统实时性和精度的重要手段,也是为红外图像相关研究提供实验平台。二、研究内容及技术路线本课题的研究内容是设计一

基于SOPC的远程视频图像监控系统的设计.pdf

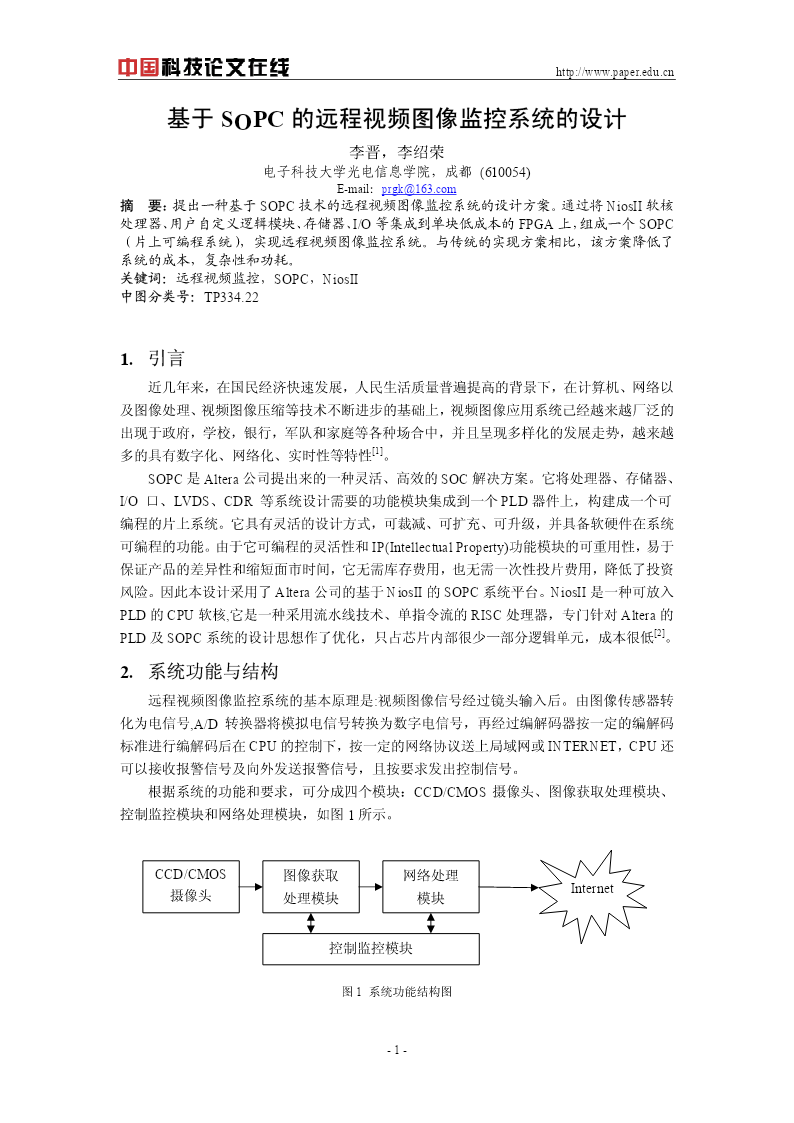

http://www.paper.edu.cn基于SOPC的远程视频图像监控系统的设计李晋,李绍荣电子科技大学光电信息学院,成都(610054)E-mail:prgk@163.com摘要:提出一种基于SOPC技术的远程视频图像监控系统的设计方案。通过将NiosII软核处理器、用户自定义逻辑模块、存储器、I/O等集成到单块低成本的FPGA上,组成一个SOPC(片上可编程系统),实现远程视频图像监控系统。与传统的实现方案相比,该方案降低了系统的成本,复杂性和功耗。关键词:远程视频监控,SOPC,NiosII中

基于SOPC的VOIP终端系统中存储系统的设计的综述报告.docx

基于SOPC的VOIP终端系统中存储系统的设计的综述报告SOPC(SystemonProgrammableChip)是一种基于可编程逻辑器件的嵌入式技术。其最大优点是可以根据需求灵活地组合不同的模块,实现不同的功能,同时减少系统成本和开发时间。本文将综述基于SOPC的VOIP终端系统中存储系统的设计。一、VOIP系统存储系统的需求VOIP终端系统需要存储一些重要的数据,例如通讯日志、联系人信息、语音邮件等。这些数据的存储需要满足以下需求:1.数据安全性:VOIP终端系统中的重要数据需要进行加密存储,以保障