基于SOPC的远程视频图像监控系统的设计.pdf

qw****27

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于SOPC的远程视频图像监控系统的设计.pdf

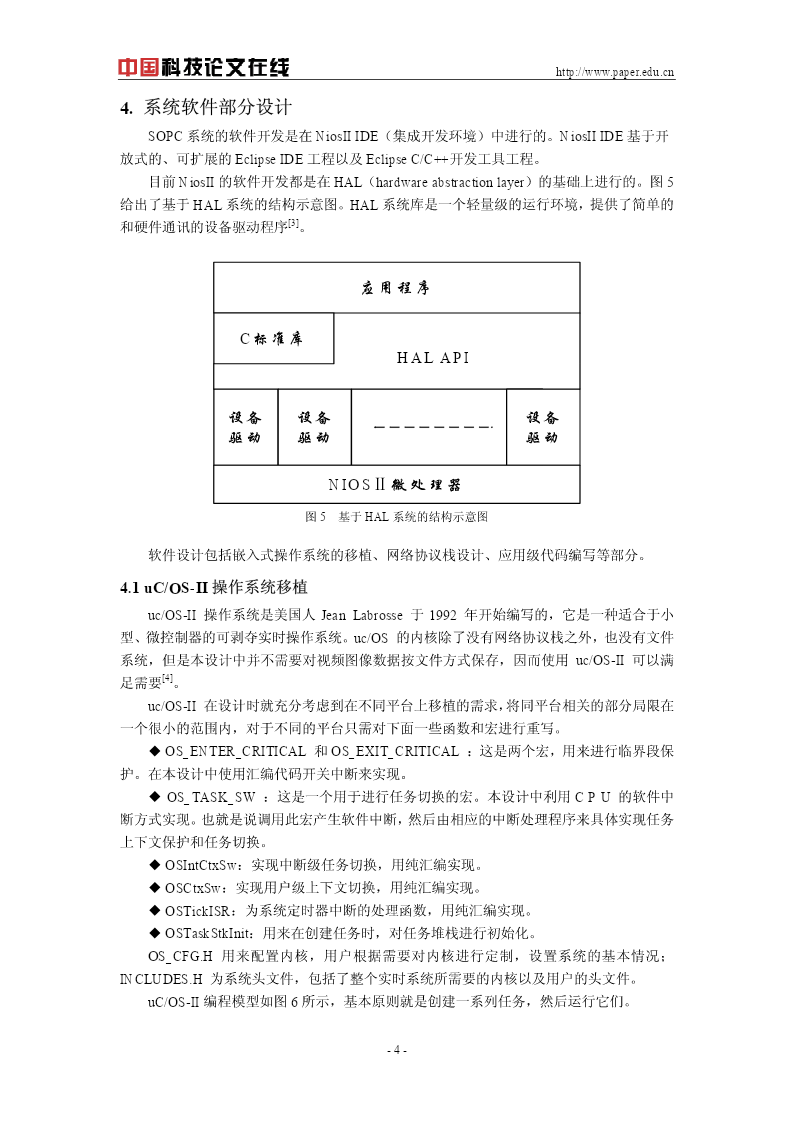

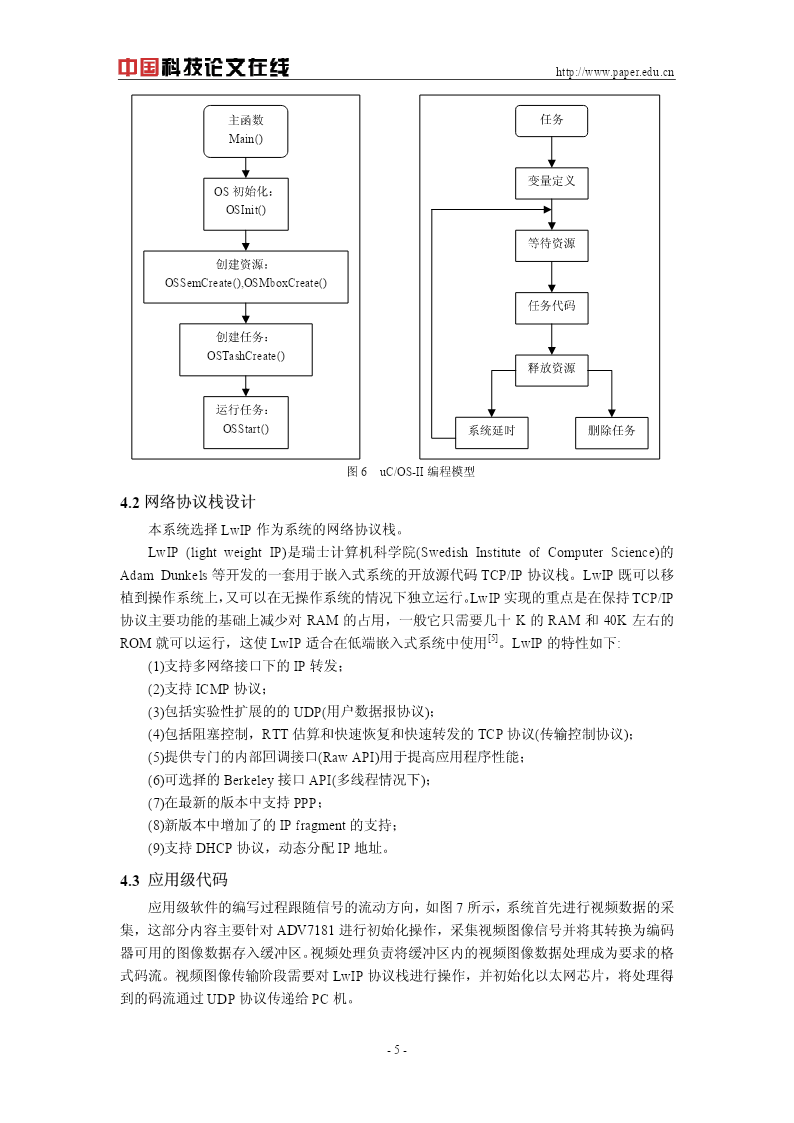

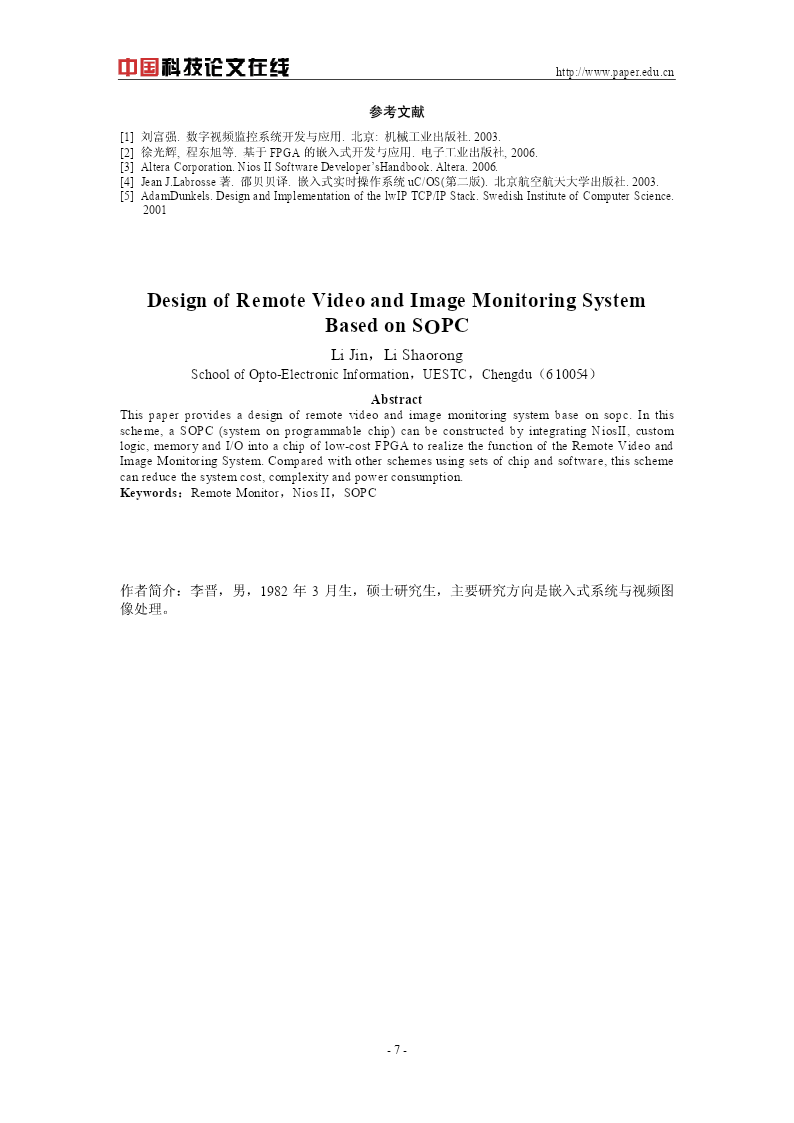

http://www.paper.edu.cn基于SOPC的远程视频图像监控系统的设计李晋,李绍荣电子科技大学光电信息学院,成都(610054)E-mail:prgk@163.com摘要:提出一种基于SOPC技术的远程视频图像监控系统的设计方案。通过将NiosII软核处理器、用户自定义逻辑模块、存储器、I/O等集成到单块低成本的FPGA上,组成一个SOPC(片上可编程系统),实现远程视频图像监控系统。与传统的实现方案相比,该方案降低了系统的成本,复杂性和功耗。关键词:远程视频监控,SOPC,NiosII中

基于SOPC技术的视频图像处理系统的设计.docx

基于SOPC技术的视频图像处理系统的设计摘要:随着视频技术的不断发展,视频图像处理技术也得到了广泛的应用。基于SOPC技术的视频图像处理系统是一种新型的图像处理系统,具有高效、可靠、灵活、低功耗等优点。本文介绍了基于SOPC技术的视频图像处理系统的设计思路和实现方法,并通过实验验证了其可行性和效果良好的特点,为该技术的进一步发展提供了一定的参考和借鉴价值。关键词:SOPC技术;视频图像处理;系统设计;实现方法;一、引言随着信息技术的不断发展,视频技术及其应用已经逐渐渗透到人们的生活中,乃至影响了人们的思想

基于FPGA SoPC的视频图像处理系统设计.pdf

基于FPGA+SoPC的视频图像处理系统设计摘要:随着信息科技技术的深入研究与应用,在很多行业领域都应用到视频图像。该文对视频图像处理系统设计分析与研究关键通过SoPC及FPGA两大处理技术。系统采用视频转换芯片SAA7113完成视频图像采集模块的设计,采用CY7C1049SRAM完成图像数据的存储,设计VGA显示输出控制关联模块,同时重新修改了显示芯片具体运作形式的配置信息,相结合产生VGA具有控制能力的信号;参考VGA显示器的运行原则,实现了VGA帧一致性信号与接口水平的提升。关键词:视频图像;图像处

基于IMS的远程视频监控系统设计.pdf

http://www.paper.edu.cn基于IMS的远程视频监控系统设计步日欣,吕玉琴,李巍海,刘刚北京邮电大学电子工程学院,北京(100876)E-mail:berisun@sohu.com摘要:面向最终用户的视频监控业务目前正在越来越受到关注,本文首先分析了IMS网络开放性的网络架构,在此基础之上,结合视频监控业务的业务需求和技术特点,提出了基于IMS网络的远程视频监控系统的架构设计,并且对组网方案、信令流程和计费管理作了相应的阐述,为在IMS网络上开发多样服务提供了参考。关键词:IP多媒体子系

基于SoPC的视频图像去雾设计.pptx

汇报人:CONTENTSPARTONEPARTTWOSoPC的定义SoPC的特点SoPC的应用领域PARTTHREE视频图像去雾的必要性去雾技术的分类去雾算法的原理PARTFOUR基于SoPC的去雾系统架构SoPC的硬件资源分配去雾算法的优化实现系统性能评估PARTFIVE实验环境与数据集实验过程与结果展示结果分析性能对比与优势分析PARTSIX本文工作总结去雾技术未来发展方向基于SoPC的去雾技术应用前景汇报人: