基于AD5724的数模转换电路设计.docx

胜利****实阿

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于AD5724的数模转换电路设计.docx

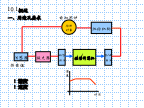

基于AD5724的数模转换电路设计张儒【摘要】数模转换电路在仪器信号模拟中起重要的作用,本文介绍了DAC芯片AD5724的工作原理以及工作方式设置,并在此基础上阐述了基于AD5724和FPGA的测井仪器信号模拟的实现方法,同时给出了硬件电路的电路图。通过多次试验,表明该电路工作稳定可靠,取得了良好效果。【关键词】AD5724;数模转换;FPGA【Abstract】DACcircuitplaysanimportantroleinthesignalsimulation,thispaperintroducest

基于STM32和AD5791的高精度数模转换电路设计.docx

基于STM32和AD5791的高精度数模转换电路设计摘要:现在很多智能仪表中,要求有超高精度的电压信号输出,而且要求刷新率高、噪声低,常规的处理电路比较复杂,难以实现自动校准。为了解决该问题,采用了20位的高精度数模转换器(DAC)AD5791,并应用于基于STM32的测量仪表中。本文详细介绍了软硬件设计。此系统实现了超高精度的单路可调电压输出,精度高和噪声低。关键词:数模转换器;STM32;AD57910引言现在很多智能测量仪表要求具有超高精度的电压信号,同时要求高稳定性、高线形度和低噪声、低温度漂移。

AI优化数模转换.pptx

数模转换基础概念数模转换基础概念数模转换基础概念数模转换基础概念AI在数模转换中的应用AI在数模转换中的应用AI在数模转换中的应用AI在数模转换中的应用AI优化算法概述AI优化算法概述AI优化算法概述AI优化算法概述优化算法的性能比较优化算法的性能比较优化算法的性能比较优化算法的性能比较基于AI的优化案例研究基于AI的优化案例研究基于AI的优化案例研究基于AI的优化案例研究AI优化数模转换的挑战AI优化数模转换的挑战AI优化数模转换的挑战AI优化数模转换的挑战未来发展趋势及前景未来发展趋势及前景未来发展趋

数模和模数转换.ppt

第五讲数模和模数转换5.1概述能将模拟量转换为数字量的电路称为模数转换器,简称A/D转换器或ADC;能将数字量转换为模拟量的电路称为数模转换器,简称D/A转换器或DAC。ADC和DAC是沟通模拟电路和数字电路的桥梁,也可称之为两者之间的接口。5.2D/A转换器将输入的每一位二进制代码按其权的大小转换成相应的模拟量,然后将代表各位的模拟量相加,所得的总模拟量就与数字量成正比,这样便实现了从数字量到模拟量的转换。转换特性(1)分辨率分辨率用输入二进制数的有效位数表示。在分辨率为n位的D/A转换器中,输出电压能

数模和模数转换.ppt

10.1概述一、用途及要求二、分类10.2D/A转换器10.2.1权电阻网络D/A转换器电路结构和工作原理10.2.2倒T形电阻网络型D/A转换器令:10.2.3D/A转换器的主要技术指标D111101…10.3.1A/D转换的一般步骤取样—保持电路:2.量化与编码并行比较型A/D转换器真值表10.3.3逐次渐近型A/D转换器8位逐次比较型A/D转换器波形图t=T1t=T1=2nTC10.3.5A/D转换器的主要技术指标第10章作业