数模和模数转换.ppt

sy****28

亲,该文档总共29页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数模和模数转换.ppt

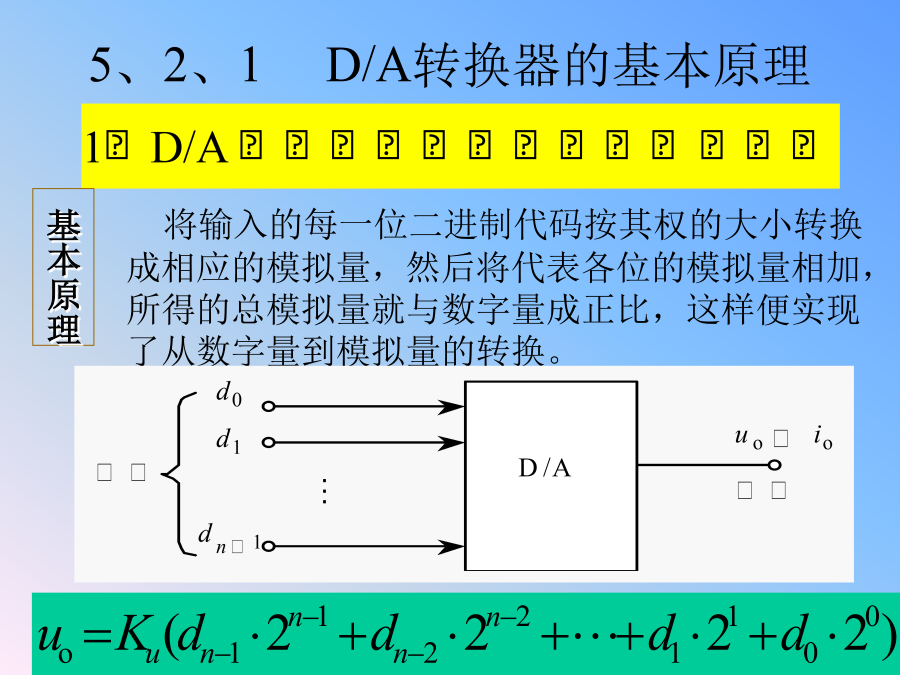

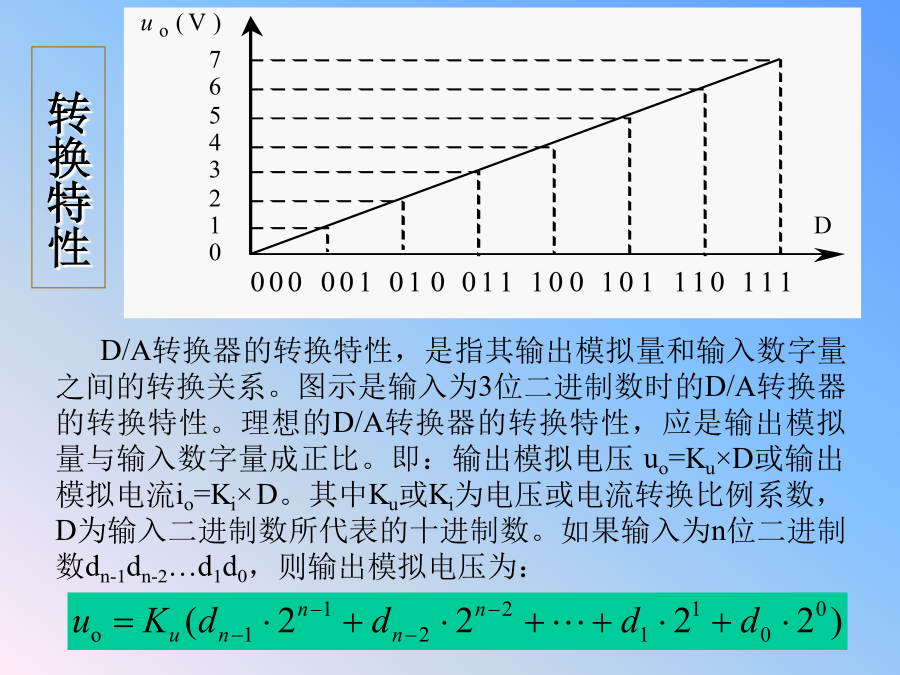

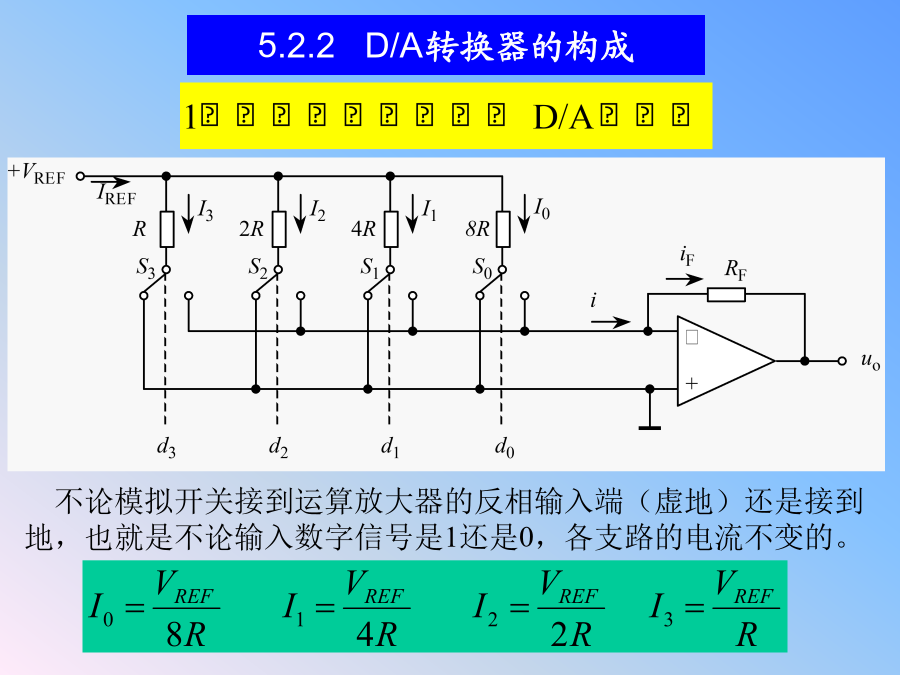

第五讲数模和模数转换5.1概述能将模拟量转换为数字量的电路称为模数转换器,简称A/D转换器或ADC;能将数字量转换为模拟量的电路称为数模转换器,简称D/A转换器或DAC。ADC和DAC是沟通模拟电路和数字电路的桥梁,也可称之为两者之间的接口。5.2D/A转换器将输入的每一位二进制代码按其权的大小转换成相应的模拟量,然后将代表各位的模拟量相加,所得的总模拟量就与数字量成正比,这样便实现了从数字量到模拟量的转换。转换特性(1)分辨率分辨率用输入二进制数的有效位数表示。在分辨率为n位的D/A转换器中,输出电压能

数模和模数转换.ppt

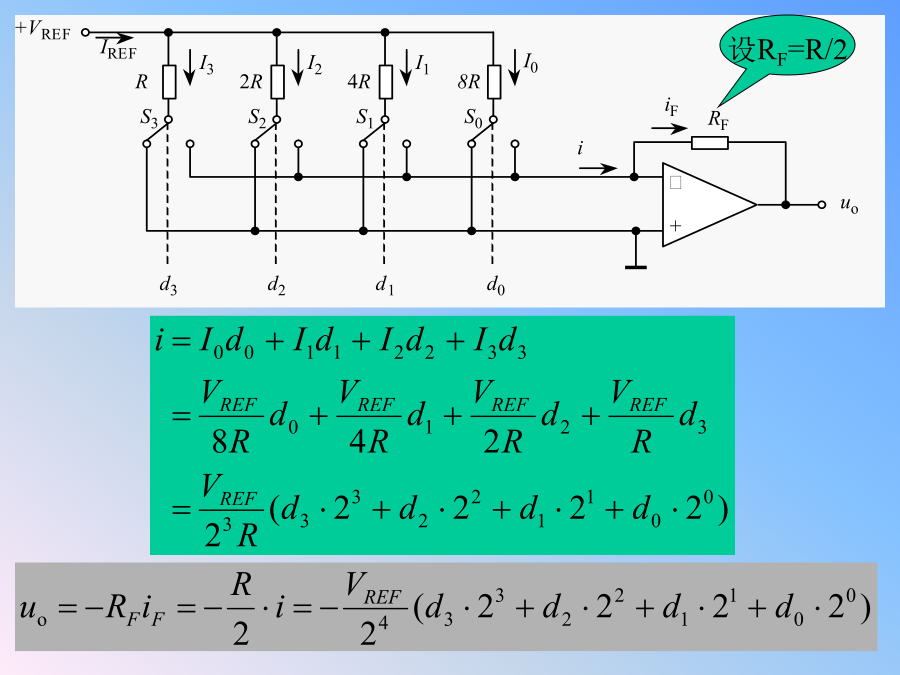

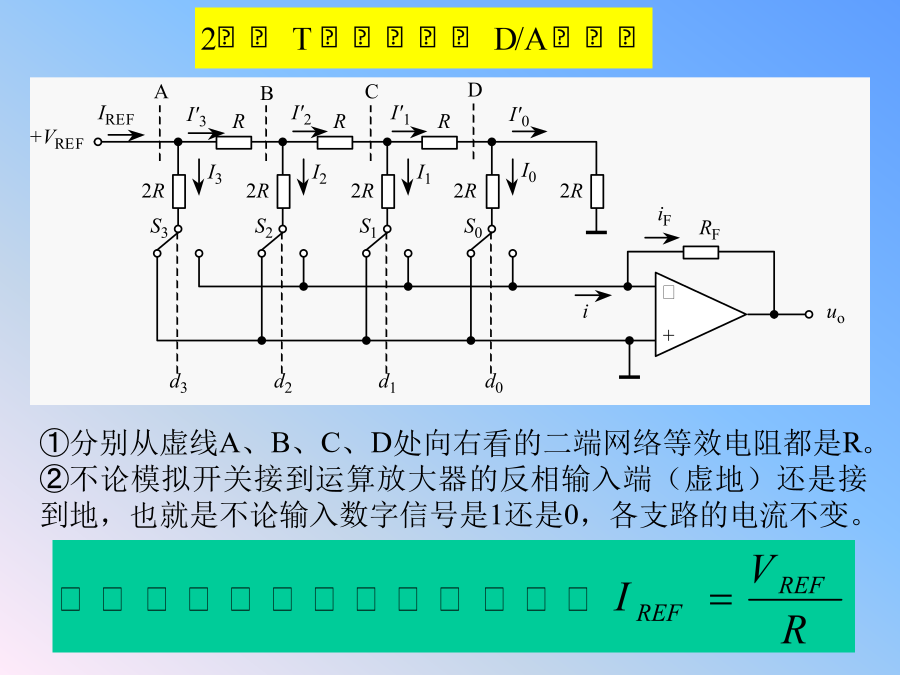

10.1概述一、用途及要求二、分类10.2D/A转换器10.2.1权电阻网络D/A转换器电路结构和工作原理10.2.2倒T形电阻网络型D/A转换器令:10.2.3D/A转换器的主要技术指标D111101…10.3.1A/D转换的一般步骤取样—保持电路:2.量化与编码并行比较型A/D转换器真值表10.3.3逐次渐近型A/D转换器8位逐次比较型A/D转换器波形图t=T1t=T1=2nTC10.3.5A/D转换器的主要技术指标第10章作业

数模和模数转换PPT课件.pptx

把模拟量转化为数字量的过程称为模-数转换,把相应的转换器件称为模-数转换器(Analog-DigitalConverter,简称A/D转换器或ADC)。A/D、D/A转换器在数字系统中的应用框图9.2D/A转换电路DAC输入的n位二进制数字信息Dn(Bn-1,Bn-2,…,B1、B0),当n=3时,DAC的输出与输入转换特性图,输出为阶梯波。2.电压型DAC3.电流型DAC9.2.2倒T型电阻网络D/A转换器倒T型电阻网络DAC采用R-2R两种电阻构成电阻网络。(1)当某位数码为1时,其相应的模拟开关把该

数模和模数转换器.ppt

第10章数模和模数转换器10.1概述模拟量数字信号输出模拟电压uO=D△=(Dn-12n-1+Dn-22n-2++D121+D020)△10.1.1D/A转换器的构成设RF=R/2S0I模拟开关Si受相应数字位Di控制。当Di=1时,开关合向“1”侧,相应支路电流Ii输出;Di=0时,开关合向“0”侧,Ii流入地而不能输出。误差分析一种简化的CMOS开关型D/A转换器CMOS开关电路的组成及工作原理(1)分辨率分辨率用输入二进制数的有效位数表示。在分辨率为n位的D/A转换器中,输出电压能区分2n个不

第6章数模和模数的转换.ppt

第6章数模和模数转换第6章数模和模数转换概述6.1.1D/A转换原理本节小结:6.3A/D转换器模拟电子开关S在采样脉冲CPS的控制下重复接通、断开的过程。S接通时,ui(t)对C充电,为采样过程;S断开时,C上的电压保持不变,为保持过程。在保持过程中,采样的模拟电压经数字化编码电路转换成一组n位的二进制数输出。t0时刻S闭合,CH被迅速充电,电路处于采样阶段。由于两个放大器的增益都为1,因此这一阶段uo跟随ui变化,即uo=ui。t1时刻采样阶段结束,S断开,电路处于保持阶段。若A2的输入阻抗为无穷大,