数字信号处理系统的实现下.pptx

文库****品店

亲,该文档总共52页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

数字信号处理系统的实现下.pptx

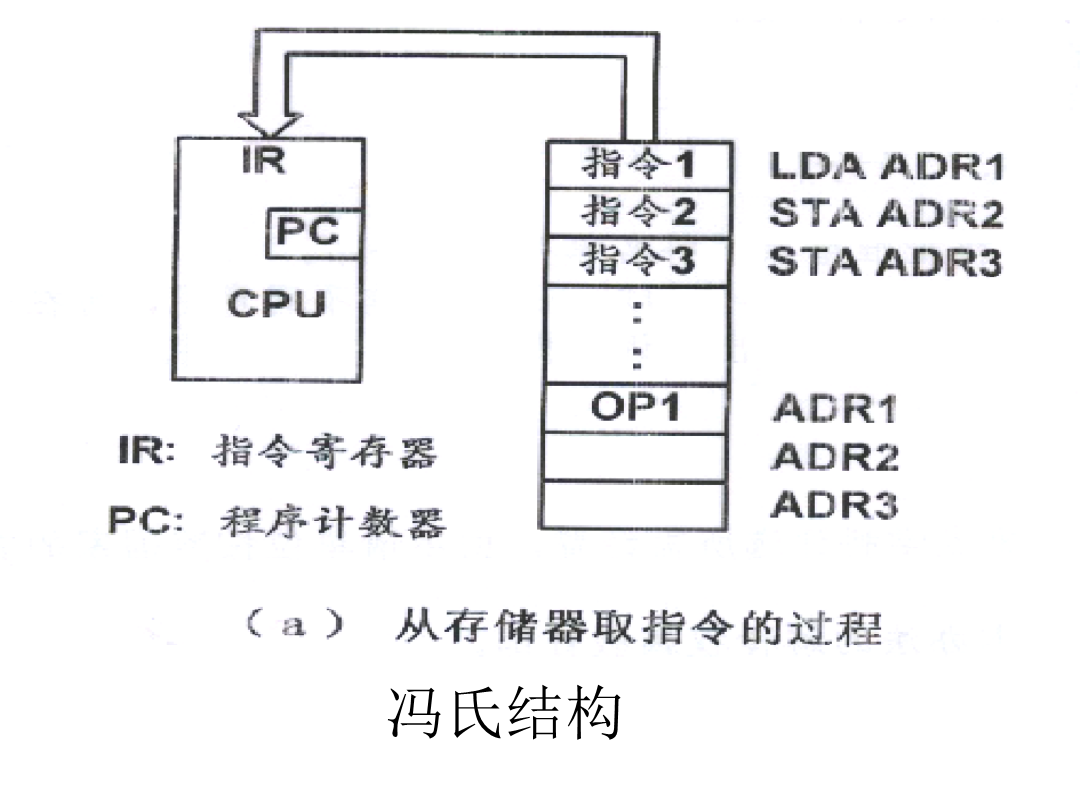

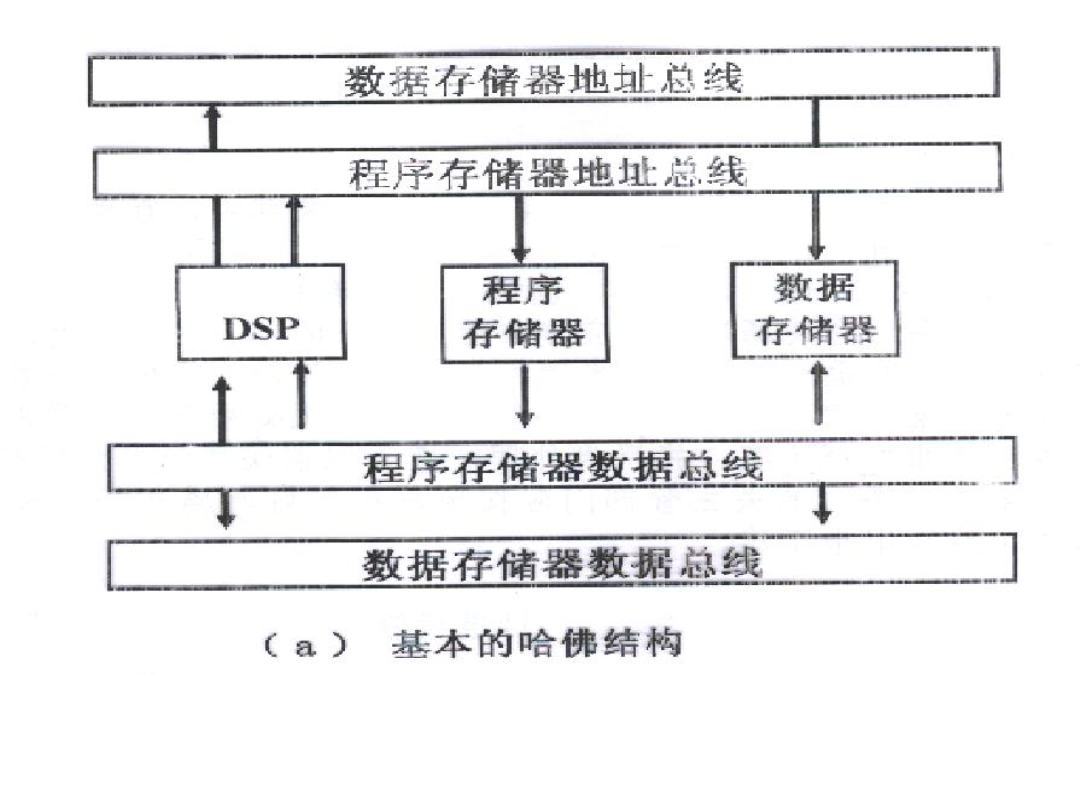

5.6数字信号处理硬件-数字信号处理器一、数字信号处理器的发展概况最早问世的6种DSP每隔10年DSP芯片的发展冯氏结构2)具有高速阵列乘法器等专用硬件。精度至少为16×16位定点,一些DSP的片内已含有40×40位的浮点乘法器。3)具有高速的片内数据存储器和程序存储器。对于一些简单、单一的操作,例如卷积、相关等,可以在片内完成,避免与外部的低速存储器打交道。新近的DSP产品均为双端口片内RAM。并行接口串行接口DMA多处理器并行的链路接口全局存储器的控制逻辑和接口TMS320C2000系列TMS320C

数字信号处理方法、数字信号处理系统及雷达芯片.pdf

本发明揭示了一种数字信号处理方法、数字信号处理系统及雷达芯片,所述数字信号处理方法包括:获取毫米波回波信号的原始数据;对原始数据进行截取和/或补零操作;基于FFT获取一维距离FFT数据;提取距离域上的有效目标数据;将距离域上的有效目标数据进行缓存,并将预设时间周期内的数据按多普勒维度方向顺序排列;基于多普勒效应和FFT获取二维多普勒FFT数据;提取距离多普勒二维域上的有效目标数据。本发明以毫米波回波信号的原始数据为输入,经过处理后能够选择性输出多种数据,提取得到高层级的有效雷达目标数据输出给毫米波雷达芯片

透镜声纳数字信号处理系统设计与实现的任务书.docx

透镜声纳数字信号处理系统设计与实现的任务书一、任务背景透镜声纳作为一种探测工具,已经被广泛应用于海洋、水下等领域。其原理是利用声波在大气和水中传播的速度不同,通过声波的反射、折射等现象,实现对目标的探测与测量。而透镜声纳的特点就在于其能够将声波通过一个透镜进行聚焦,从而实现对目标的定位、成像等功能。透镜声纳的数字信号处理涉及到很多方面,比如数字滤波、波束形成、目标检测等,这些都是影响声纳能力的关键因素。因此设计一种高效、精确的透镜声纳数字信号处理系统非常有必要。二、项目目标1.确定透镜声纳数字信号处理系统

干涉型光纤陀螺数字信号处理系统研究的开题报告.docx

干涉型光纤陀螺数字信号处理系统研究的开题报告一、选题背景和意义随着信息时代的到来,导航和定位技术在现代社会中得到广泛应用,而光纤陀螺作为一种高精度、高稳定性的惯性导航传感器,被广泛用于航空、航天、海洋等领域的导航定位中。光纤陀螺通过检测光纤的干涉效应来测量转角变化,其输出结果可用于导航系统中,因此光纤陀螺的性能对导航定位精度影响十分重要。目前国内外已有很多关于光纤陀螺的研究,但其数字信号处理系统设计仍存在诸多难题,例如光源稳定性、信号采样频率、信号噪声等问题。因此,研究光纤陀螺数字信号处理系统,对于提高光

基于向量矩阵乘法器的光学数字信号处理系统的研究的开题报告.docx

基于向量矩阵乘法器的光学数字信号处理系统的研究的开题报告一、研究背景光学数字信号处理系统已经成为一个非常重要的领域,在数字信号处理、光通信、光学成像等领域都有着广泛的应用。其中,向量矩阵乘法器(VMM)作为光学数字信号处理器的一种重要形式,在光学神经网络、光学卷积神经网络以及光学多铁元件等方面都具有着非常重要的应用和前景。传统的数字信号处理器一般采用电子器件进行运算,但是其速度和精度存在一定的局限性。而光学数字信号处理器可以利用其并行的特点,在运算速度和精度方面有很大的优势。尤其是在大规模数据处理的情况下