新型多核网络处理器.pptx

胜利****实阿

亲,该文档总共63页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

新型多核网络处理器.pptx

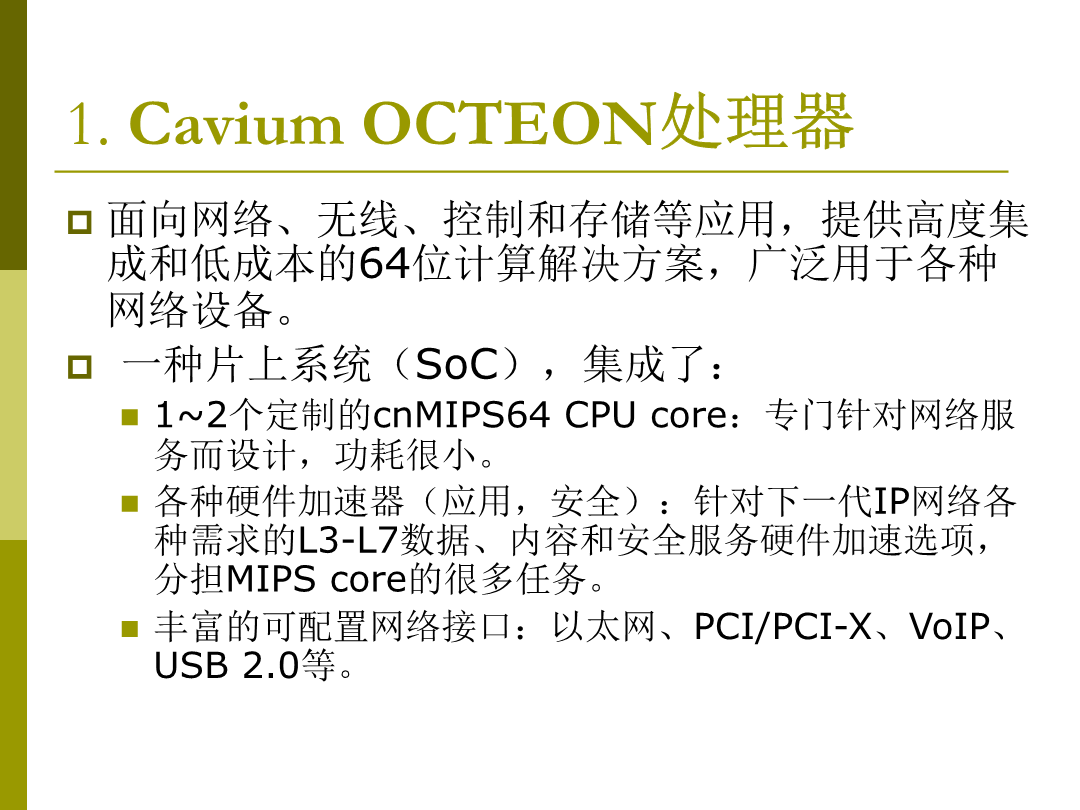

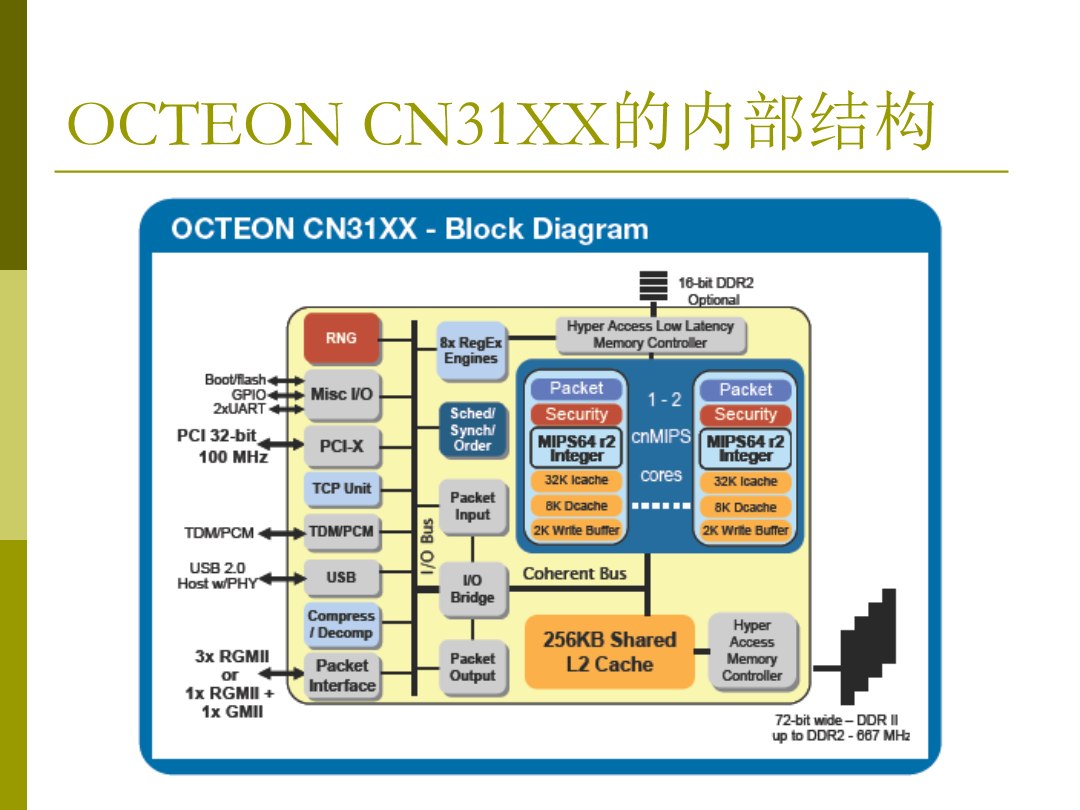

新型多核网络处理器主要参考文献研发背景现状新型NP与传统NP的不同主要的多核NP半导体厂商1.CaviumOCTEON处理器OCTEONCN31XX的内部结构CN31XX的组成CN31XX的组成(续)CN31XX的组成(续)性能2.BroadcomBCM14803.RMIXLR处理器XLR732的内部结构XLR处理器的设计特色XLR处理器内部结构XLR的专利设计3.1处理器核线程调度--Eagerround-robin线程调度—Multithreadedfixed-cyclescheduling线程调度-

多核处理器创新型多核处理器的发展.docx

多核处理器创新型多核处理器的发展布线延迟将影响目前主流商用超标量和vliw技术的长远发展。目前,一些新型多核处理器结构初露端倪,它们依赖于开发指令级并行性以外的其他更粗粒度的并行性,如数据级并行性和线程级并行性,以实现更高性能和应用效能。仅靠扩充目前占主流的超标量和vliw技术,要实现新一代处理器是十分困难的,其中一个主要原因是布线延迟问题。随着芯片制造技术的发展,一个时钟周期中信号在芯片内所能传输的范围越来越小。特别当未来采用35纳米以下设计技术时,在一个时钟周期内信号所能传输的范围仅为芯片

多核处理器创新型多核处理器的发展.docx

多核处理器创新型多核处理器的发展布线延迟将影响目前主流商用超标量和vliw技术的长远发展。目前一些新型多核处理器结构初露端倪它们依赖于开发指令级并行性以外的其他更粗粒度的并行性如数据级并行性和线程级并行性以实现更高性能和应用效能。仅靠扩充目前占主流的超标量和vliw技术要实现新一代处理器是十分困难的其中一个主要原因是布线延迟问题。随着芯片制造技术的发展一个时钟周期中信号在芯片内所能传输的范围越来越小。特别当未来采用35纳米以下设计技术时在一个时钟周期内信号所能传输的范围

多核处理器创新型多核处理器的发展.docx

多核处理器创新型多核处理器的发展布线延迟将影响目前主流商用超标量和vliw技术的长远发展。目前,一些新型多核处理器结构初露端倪,它们依赖于开发指令级并行性以外的其他更粗粒度的并行性,如数据级并行性和线程级并行性,以实现更高性能和应用效能。仅靠扩充目前占主流的超标量和vliw技术,要实现新一代处理器是十分困难的,其中一个主要原因是布线延迟问题。随着芯片制造技术的发展,一个时钟周期中信号在芯片内所能传输的范围越来越小。特别当未来采用35纳米以下设计技术时,在一个时钟周期内信号所能传输的范围仅为芯片面积的1%。

多核处理器创新型多核处理器的发展.docx

多核处理器创新型多核处理器的发展布线延迟将影响目前主流商用超标量和vliw技术的长远发展。目前一些新型多核处理器结构初露端倪它们依赖于开发指令级并行性以外的其他更粗粒度的并行性如数据级并行性和线程级并行性以实现更高性能和应用效能。仅靠扩充目前占主流的超标量和vliw技术要实现新一代处理器是十分困难的其中一个主要原因是布线延迟问题。随着芯片制造技术的发展一个时钟周期中信号在芯片内所能传输的范围越来越小。特别当未来采用35纳米以下设计技术时在一个时钟周期内信号所能传输的范围