并行FLASH访问系统和方法.pdf

白凡****12

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

并行FLASH访问系统和方法.pdf

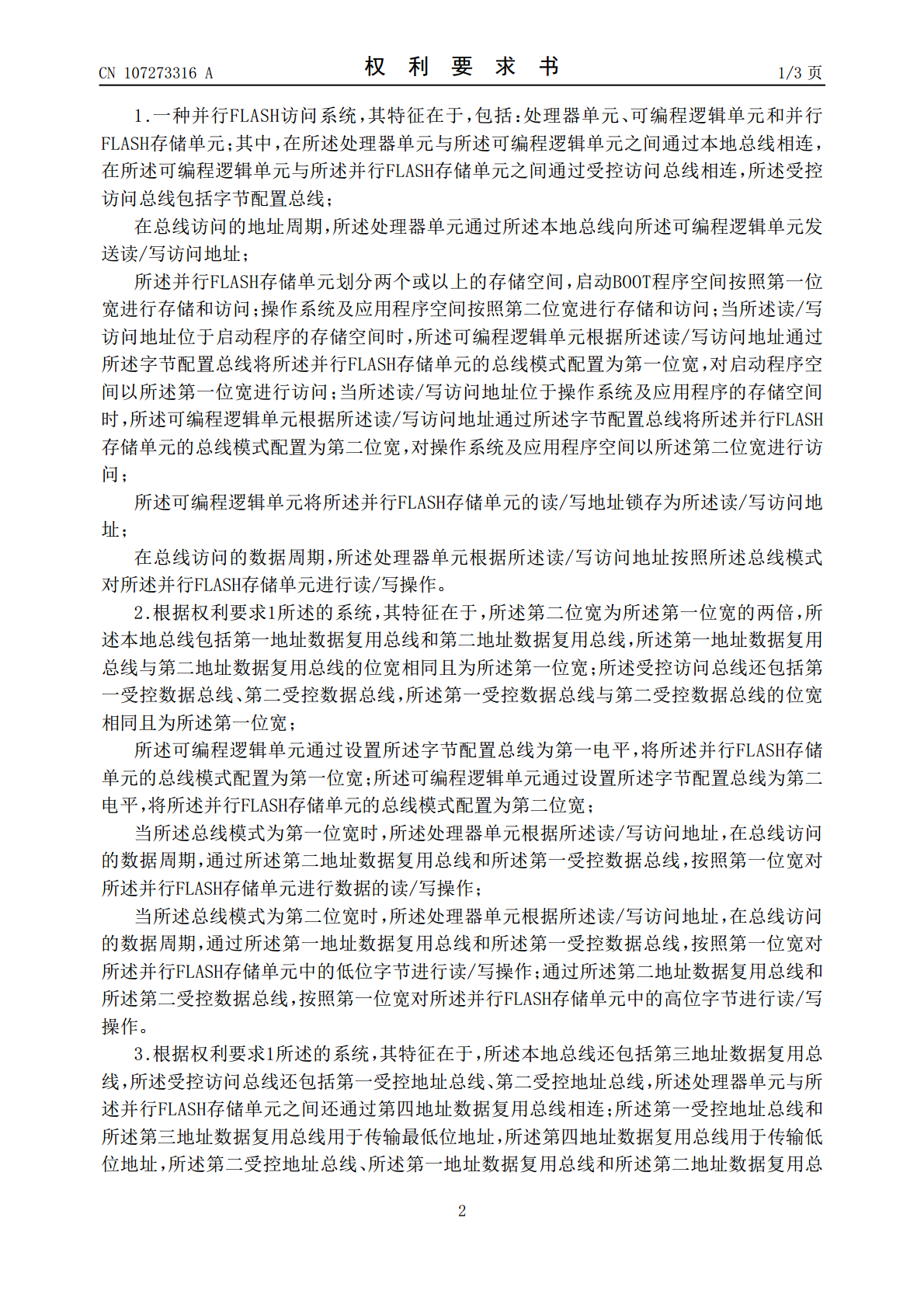

本申请公开了一种并行FLASH访问系统和方法,涉及数据通信领域,用于实现对并行FLASH采用不同位宽总线来访问和数据存储。并行FLASH访问系统,包括:处理器单元、可编程逻辑单元和并行FLASH存储单元;其中,在所述处理器单元与所述可编程逻辑单元之间通过本地总线相连,在所述可编程逻辑单元与所述并行FLASH存储单元之间通过受控访问总线相连。本申请实施例应用于并行FLASH访问和数据存储。

系统访问方法、系统访问装置和终端.pdf

本发明提出了一种系统访问方法、一种系统访问装置和一种终端,其中,所述方法包括:当运行在当前系统的所述终端与其他任一终端建立连接后,接收来自所述其他任一终端的第一标识信息;接收输入所述终端中的第二标识信息;判断所述第一标识信息与所述第二标识信息是否匹配,并在判断结果为是时,允许所述终端由所述当前系统切换至目标系统;否则,禁止所述终端由所述当前系统切换至所述目标系统;其中,所述目标系统为所述多个系统中安全等级高于所述当前系统的安全等级的系统。通过本发明的技术方案,在远程授权进入到终端的安全等级较高的系统的过程

DSP外挂Flash在系统编程及并行引导装载方法.docx

DSP外挂Flash在系统编程及并行引导装载方法DSP外挂Flash在系统编程及并行引导装载方法摘要:详细介绍了TMS320VC5402外挂程序存储器的在系统编程技术和方法,结合实例给出了创建系统引导表的具体步骤,并在此基础上重点叙述了TMS320VC5402的并行16位引导装载方法。设计的系统具有较大的灵活性和良好的可扩展性。关键词:DSPTMS320VC5402FLASHSST39VF400A在系统编程引导装载TMS320VC5402(以下简称C5402)是TI公司的一款性价比极好的16位定点DSP芯

DSP外挂Flash在系统编程及并行引导装载方法.docx

DSP外挂Flash在系统编程及并行引导装载方法DSP外挂Flash在系统编程及并行引导装载方法摘要:详细介绍了TMS320VC5402外挂程序存储器的在系统编程技术和方法,结合实例给出了创建系统引导表的具体步骤,并在此基础上重点叙述了TMS320VC5402的并行16位引导装载方法。设计的系统具有较大的灵活性和良好的可扩展性。关键词:DSPTMS320VC5402FLASHSST39VF400A在系统编程引导装载TMS320VC5402(以下简称C5402)是TI公司的一款性价比极好的16位定点DSP芯

并行并发测试系统和方法.pdf

提供了一种并行并发测试(PCT)系统,该系统用于进行半导体器件的并行并发测试。该PCT系统包括取放(PnP)处理机,该拾放处理机用于接合所述半导体器件并沿着测试平面输送所述半导体器件,该PnP处理机包括至少一个操纵器。该PCT系统还包括被测器件接口板(DIB)和测试机,该DIB包括:用于所述半导体器件的宽边(BS)测试的宽边测试插槽,所述宽边测试使用半导体器件引脚总数的至少一半的引脚;和用于可测试性设计(DFT)测试的多个DFT测试插槽,该DFT测试使用少于所述半导体器件引脚总数的一半的引脚,该测试机与所