并行并发测试系统和方法.pdf

Ch****91

亲,该文档总共69页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

并行并发测试系统和方法.pdf

提供了一种并行并发测试(PCT)系统,该系统用于进行半导体器件的并行并发测试。该PCT系统包括取放(PnP)处理机,该拾放处理机用于接合所述半导体器件并沿着测试平面输送所述半导体器件,该PnP处理机包括至少一个操纵器。该PCT系统还包括被测器件接口板(DIB)和测试机,该DIB包括:用于所述半导体器件的宽边(BS)测试的宽边测试插槽,所述宽边测试使用半导体器件引脚总数的至少一半的引脚;和用于可测试性设计(DFT)测试的多个DFT测试插槽,该DFT测试使用少于所述半导体器件引脚总数的一半的引脚,该测试机与所

并发系统的并行计算及性能分析.docx

并发系统的并行计算及性能分析并发系统的并行计算及性能分析摘要:随着计算机技术的不断发展,多核处理器已经成为并发计算中的重要组成部分。并行计算可以充分发挥多核处理器的性能以提高系统的吞吐量和响应时间。本文就并发系统的并行计算及其性能分析进行了研究和探讨,分析了并行计算的优势和挑战,并介绍了一些常用的性能分析方法和工具,以指导并行计算的设计和优化。关键词:并发系统、并行计算、多核处理器、性能分析1.引言并行计算作为一种利用多个处理器同时工作的计算方式,已经被广泛应用于各个领域。与传统的串行计算相比,它可以显著

并行FLASH访问系统和方法.pdf

本申请公开了一种并行FLASH访问系统和方法,涉及数据通信领域,用于实现对并行FLASH采用不同位宽总线来访问和数据存储。并行FLASH访问系统,包括:处理器单元、可编程逻辑单元和并行FLASH存储单元;其中,在所述处理器单元与所述可编程逻辑单元之间通过本地总线相连,在所述可编程逻辑单元与所述并行FLASH存储单元之间通过受控访问总线相连。本申请实施例应用于并行FLASH访问和数据存储。

数据驱动的并行排序系统和方法.pdf

本发明涉及数据驱动的并行排序系统和方法。提供了一种数据驱动的并行排序方法,包括:循环地将输入的数据记录逐个地分配给n(n>1)个分区,每个分区对应于所述并行排序中并行的一个排序处理并且分配有一个用于存储所分配的数据记录的内存块,所述内存块能够存储m(m>0)个数据记录;在各个分区中并行地对各自的内存块中的当前数据记录进行排序;响应于分配了轮的数据记录,循环地控制所述n个分区中的一个分区,将该分区的内存块中的已排序数据记录写入大容量存储器作为有序数据块,并清空该内存块;以及响应于所有数据记录完成

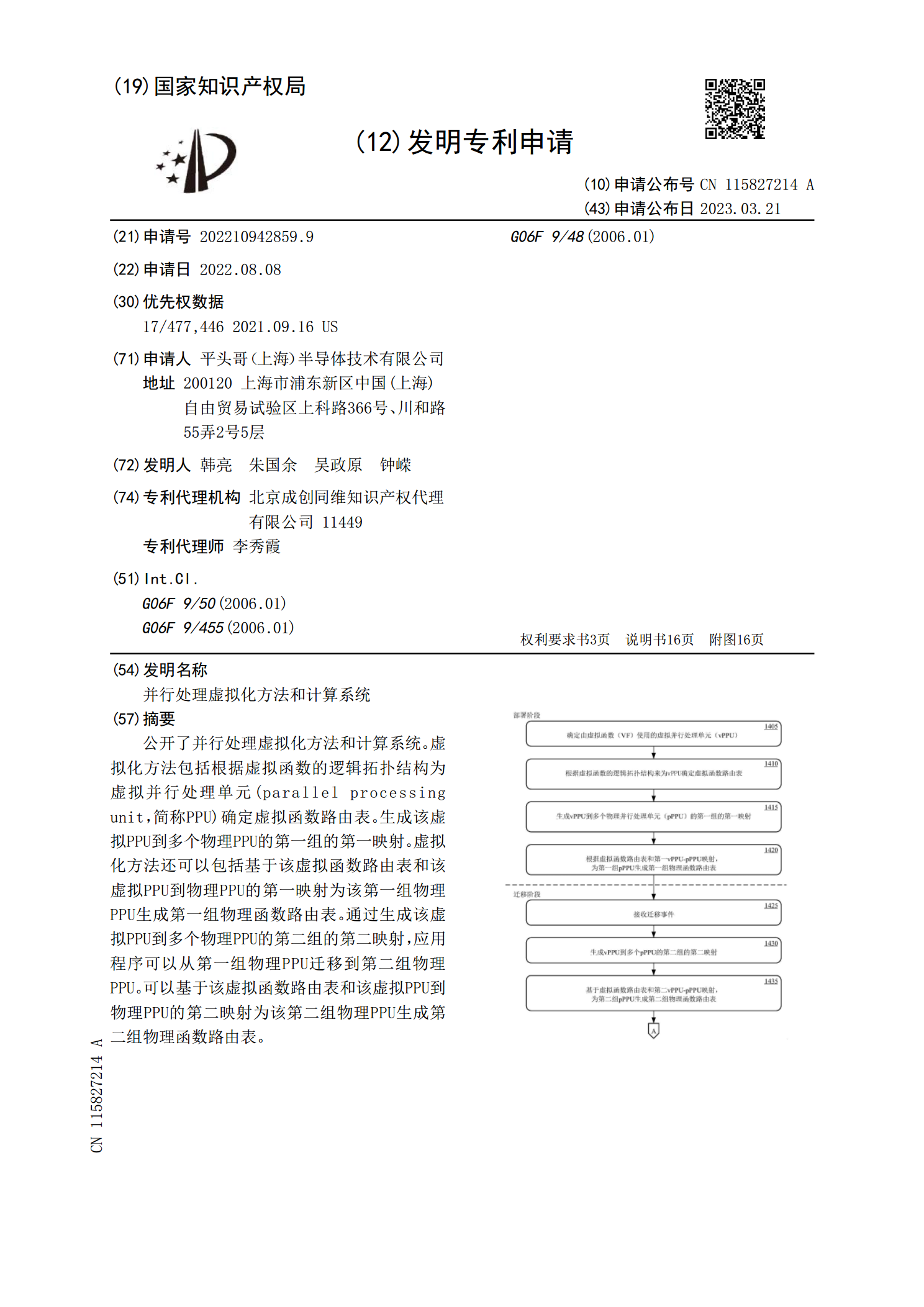

并行处理虚拟化方法和计算系统.pdf

公开了并行处理虚拟化方法和计算系统。虚拟化方法包括根据虚拟函数的逻辑拓扑结构为虚拟并行处理单元(parallelprocessingunit,简称PPU)确定虚拟函数路由表。生成该虚拟PPU到多个物理PPU的第一组的第一映射。虚拟化方法还可以包括基于该虚拟函数路由表和该虚拟PPU到物理PPU的第一映射为该第一组物理PPU生成第一组物理函数路由表。通过生成该虚拟PPU到多个物理PPU的第二组的第二映射,应用程序可以从第一组物理PPU迁移到第二组物理PPU。可以基于该虚拟函数路由表和该虚拟PPU到物理PP