FMCW回波信号接收处理系统及激光雷达信号处理装置.pdf

睿德****找我

亲,该文档总共15页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

FMCW回波信号接收处理系统及激光雷达信号处理装置.pdf

本发明公开了一种FMCW回波信号接收处理系统及激光雷达信号处理装置,所述回波信号接收处理系统包括信号采集和存储模块、信号捕获模块、信号跟踪模块和采样信号实时输出模块,信号采集和存储模块包括多个ADC模块、多个输入串行器ISERDES模块、多个复数化处理程序模块、并行线性补偿程序模块、补0和并/串转换模块和FIFO+DMA写模块等。本发明实现了多档可调调频连续波信号调节,通过参数调整,可实现不同距离测距,满足了不同条件激光雷达测距的要求。

回波信号处理装置、雷达装置、回波信号处理方法及程序.pdf

本发明提供一种回波信号处理装置、雷达装置、回波信号处理方法及程序,消除起因于发射脉冲的条件的模糊,能清晰地显示物标。进行强调在测定数据中样本间的值的变化度比例相对大的样本的测定数据的边缘强调处理,利用边缘强调处理后的测定数据进行扫描相关处理。在物标的轮廓中,离自船近的地方是样本间的值的变化度相对大的地方(是回波电平急剧上升处)。该上升部分的测定数据是即使脉冲宽度等的发射脉冲条件变化也不会有大变动的信息。因此,由于进行边缘强调处理之后实施扫描相关处理,消除起因于发射脉冲的条件的模糊等,能清晰地显示物标的轮廓

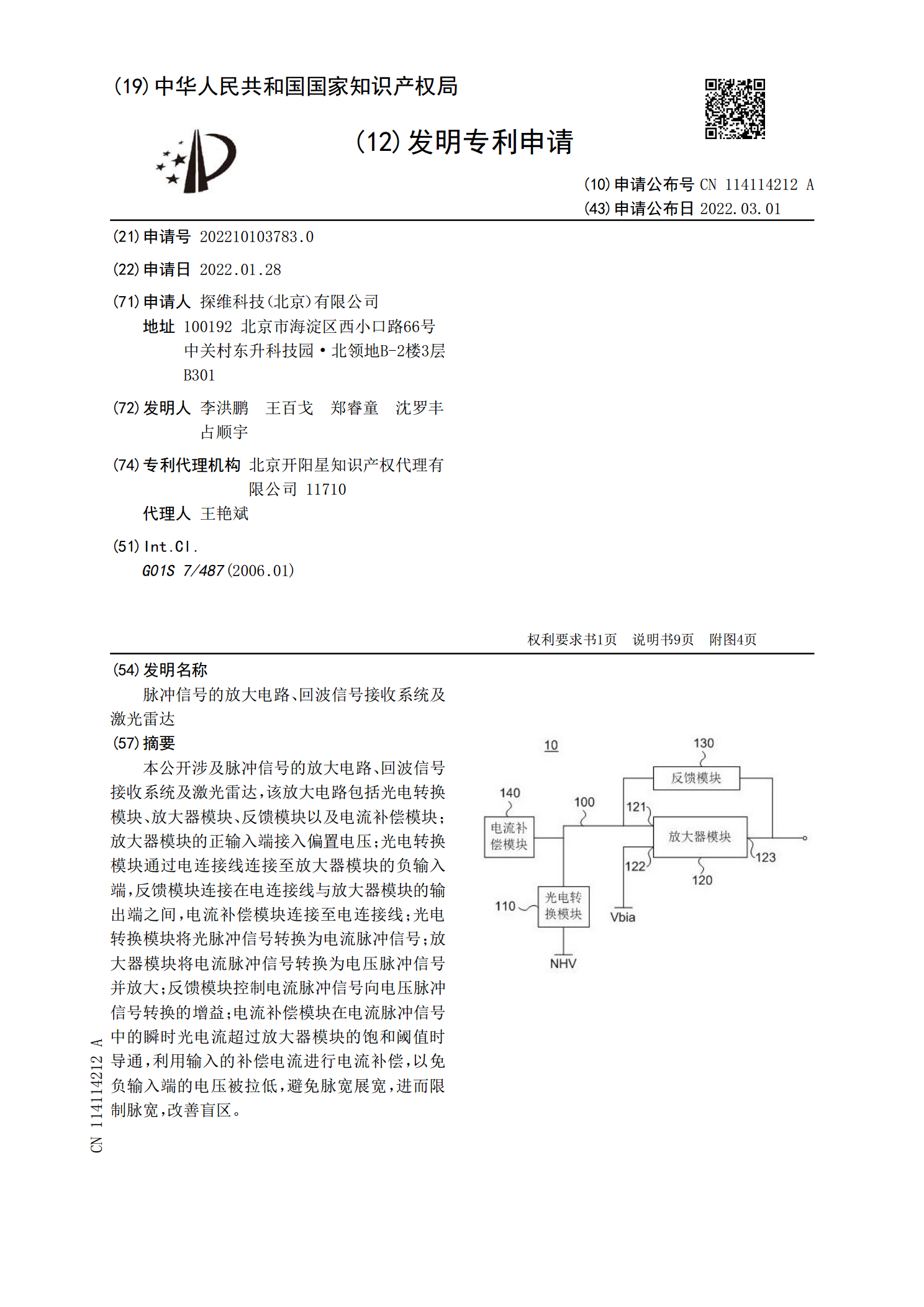

脉冲信号的放大电路、回波信号接收系统及激光雷达.pdf

本公开涉及脉冲信号的放大电路、回波信号接收系统及激光雷达,该放大电路包括光电转换模块、放大器模块、反馈模块以及电流补偿模块;放大器模块的正输入端接入偏置电压;光电转换模块通过电连接线连接至放大器模块的负输入端,反馈模块连接在电连接线与放大器模块的输出端之间,电流补偿模块连接至电连接线;光电转换模块将光脉冲信号转换为电流脉冲信号;放大器模块将电流脉冲信号转换为电压脉冲信号并放大;反馈模块控制电流脉冲信号向电压脉冲信号转换的增益;电流补偿模块在电流脉冲信号中的瞬时光电流超过放大器模块的饱和阈值时导通,利用输入

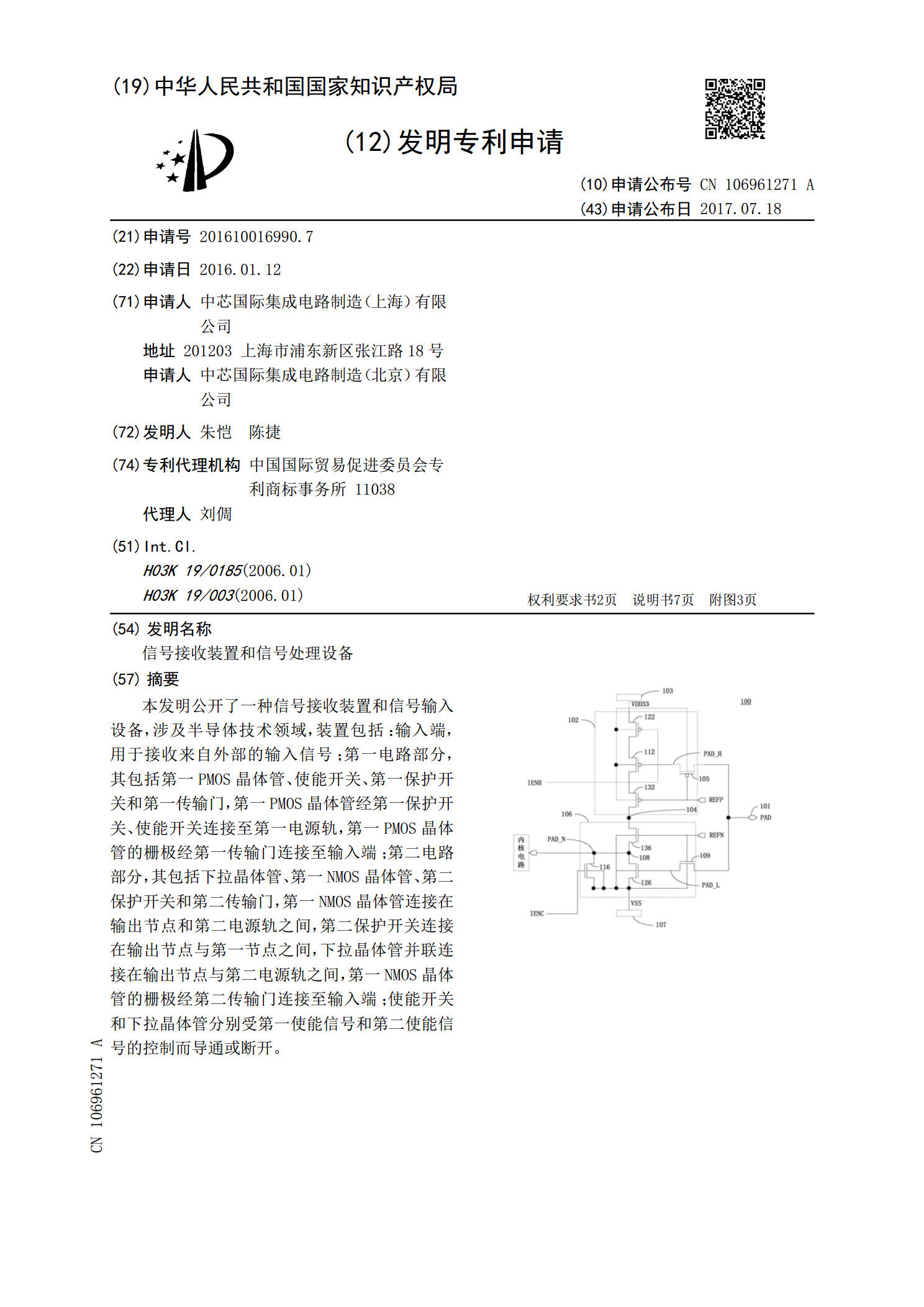

信号接收装置和信号处理设备.pdf

本发明公开了一种信号接收装置和信号输入设备,涉及半导体技术领域,装置包括:输入端,用于接收来自外部的输入信号;第一电路部分,其包括第一PMOS晶体管、使能开关、第一保护开关和第一传输门,第一PMOS晶体管经第一保护开关、使能开关连接至第一电源轨,第一PMOS晶体管的栅极经第一传输门连接至输入端;第二电路部分,其包括下拉晶体管、第一NMOS晶体管、第二保护开关和第二传输门,第一NMOS晶体管连接在输出节点和第二电源轨之间,第二保护开关连接在输出节点与第一节点之间,下拉晶体管并联连接在输出节点与第二电源轨之间

FMCW雷达信号处理系统设计方案研究.docx

FMCW雷达信号处理系统设计方案研究标题:FMCW雷达信号处理系统设计方案研究摘要:本论文旨在研究频率调制连续波(FMCW)雷达信号处理系统的设计方案。FMCW雷达是一种常用的无源探测技术,可以实现高精度、高分辨率的目标检测和距离测量。本文首先介绍了FMCW雷达的基本原理和工作原理,然后探讨了FMCW雷达信号处理系统的关键技术和设计方案,包括信号发生器、混频器、解调器和距离测量算法等。最后,本文通过实验验证了所提出方案的有效性,并提出了未来的研究方向。1.引言FMCW雷达是一种基于连续波原理的无源探测技术