7存储器、复杂可编程逻辑器和现场可编程门阵列.pptx

慧娇****文章

亲,该文档总共66页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

7存储器、复杂可编程逻辑器和现场可编程门阵列.pptx

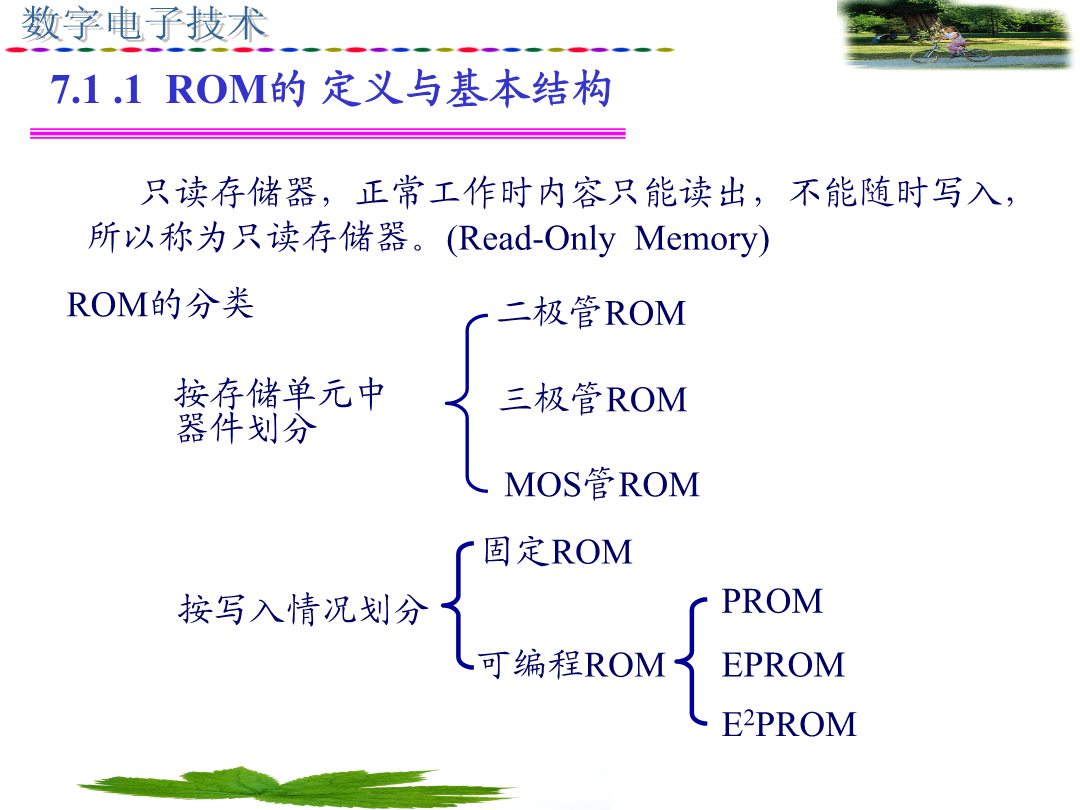

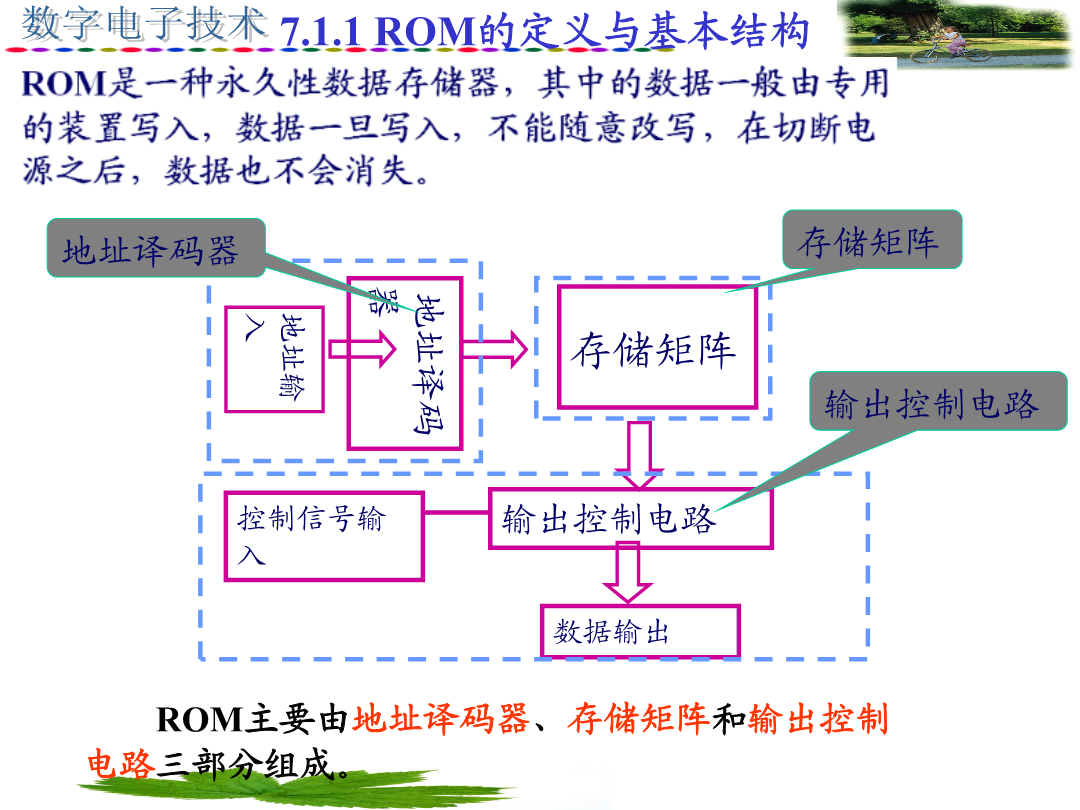

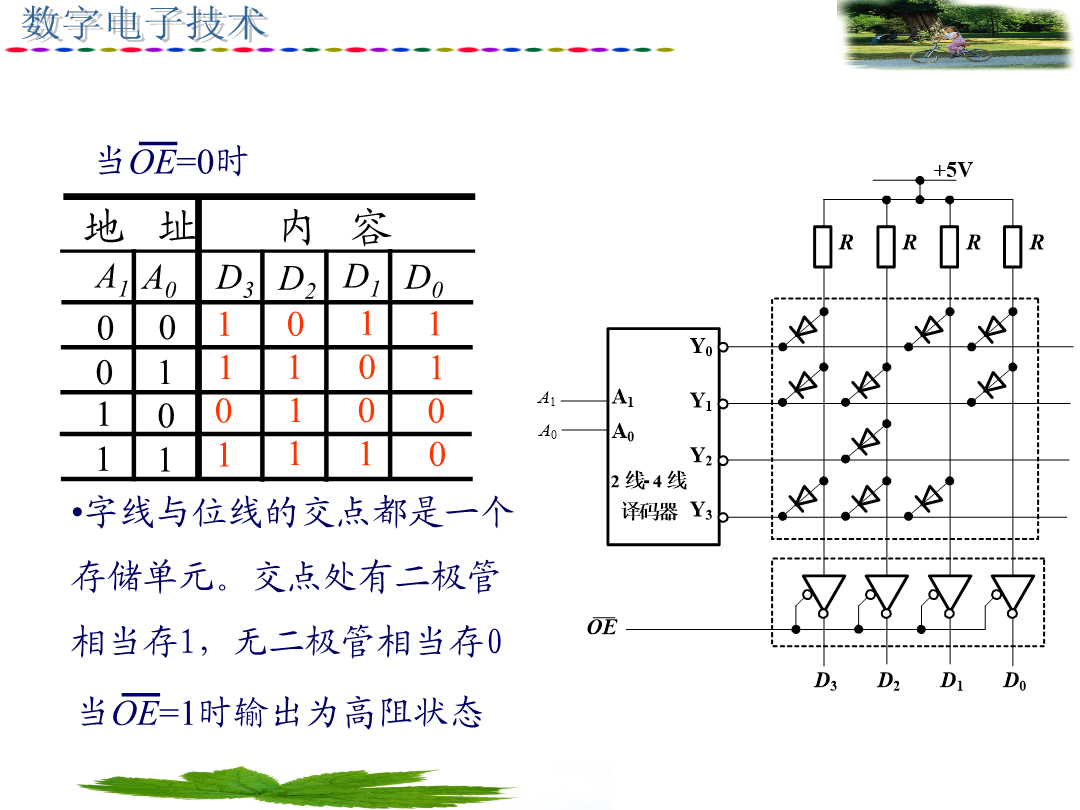

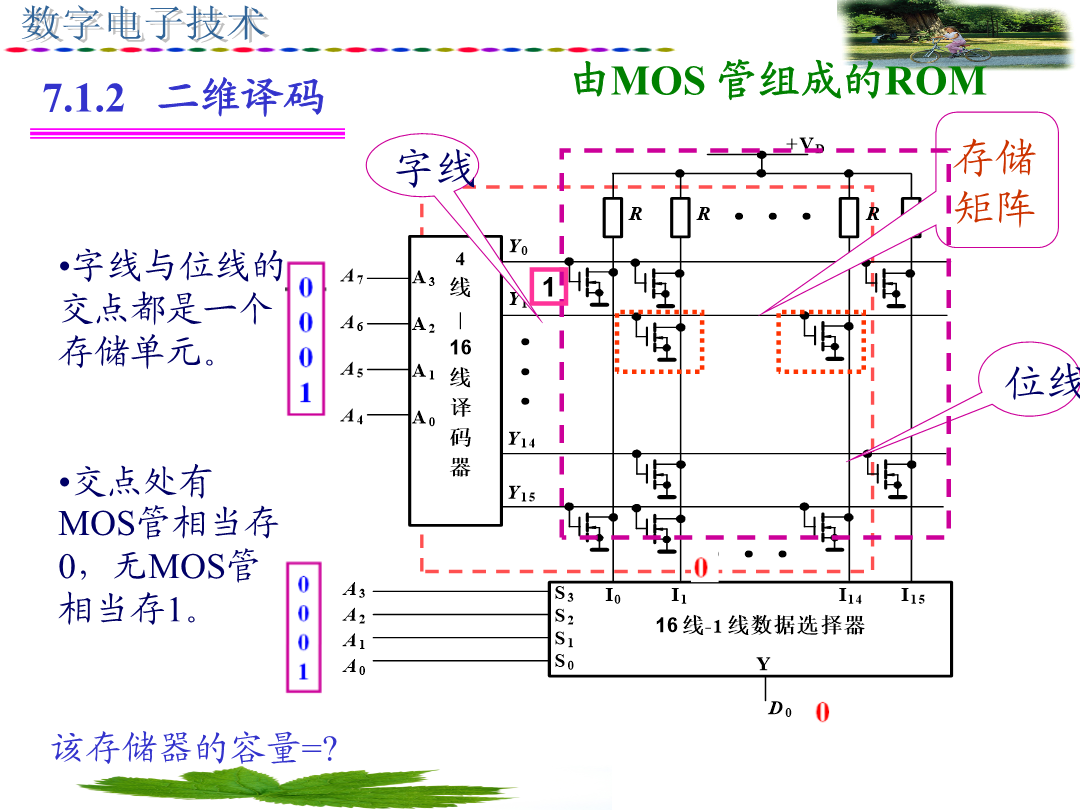

掌握半导体存储器字、位、存储容量、地址、等基本概念。掌握RAM、ROM的工作原理及典型应用。了解存储器的存储单元的组成及工作原理。了解CPLD、FPGA的结构及实现逻辑功能的编程原理。存储器的定义存储器7.1只读存储器只读存储器正常工作时内容只能读出不能随时写入所以称为只读存储器。(Read-OnlyMemory)存储矩阵1)ROM结构示意图字线与位线的交点都是一个存储单元。交点处有二极管相当存1无二极管相当存07.1.3可编程ROME2PROM:由隧道MOS管组成的可用电擦出

7存储器、复杂可编程逻辑器和现场可编程门阵列.ppt

掌握半导体存储器字、位、存储容量、地址、等基本概念。掌握RAM、ROM的工作原理及典型应用。了解存储器的存储单元的组成及工作原理。了解CPLD、FPGA的结构及实现逻辑功能的编程原理。存储器的定义存储器7.1只读存储器只读存储器正常工作时内容只能读出不能随时写入所以称为只读存储器。(Read-OnlyMemory)存储矩阵1)ROM结构示意图字线与位线的交点都是一个存储单元。交点处有二极管相当存1无二极管相当存07.1.3可编程ROME2PROM:由隧道MOS管组成的可用电擦出

7存储器、复杂可编程逻辑器和现场可编程门阵列.pptx

掌握半导体存储器字、位、存储容量、地址、等基本概念。掌握RAM、ROM的工作原理及典型应用。了解存储器的存储单元的组成及工作原理。了解CPLD、FPGA的结构及实现逻辑功能的编程原理。存储器的定义存储器7.1只读存储器只读存储器正常工作时内容只能读出不能随时写入所以称为只读存储器。(Read-OnlyMemory)存储矩阵1)ROM结构示意图字线与位线的交点都是一个存储单元。交点处有二极管相当存1无二极管相当存07.1.3可编程ROME2PROM:由隧道MOS管组成的可用电擦出

7存储器、复杂可编程逻辑器和现场可编程门阵列.ppt

掌握半导体存储器字、位、存储容量、地址、等基本概念。掌握RAM、ROM的工作原理及典型应用。了解存储器的存储单元的组成及工作原理。了解CPLD、FPGA的结构及实现逻辑功能的编程原理。存储器的定义存储器7.1只读存储器只读存储器正常工作时内容只能读出不能随时写入所以称为只读存储器。(Read-OnlyMemory)存储矩阵1)ROM结构示意图字线与位线的交点都是一个存储单元。交点处有二极管相当存1无二极管相当存07.1.3可编程ROME2PROM:由隧道MOS管组成的可用电擦出

第7章存储器、复杂可编程逻辑器和现场可编程门阵列.ppt

存储器、复杂可编程逻辑器和现场可编程门阵列教学基本要求:概述7.1只读存储器存储器几个基本概念:只读存储器,工作时内容只能读出,不能随时写入,所以称为只读存储器。(Read-OnlyMemory)存储矩阵1)ROM(二极管PROM)结构示意图字线与位线的交点都是一个存储单元。交点处有二极管相当存1,无二极管相当存0字线有一种可编程序的ROM,在出厂时全部存储“1”,用户可根据需要将某些单元改写为“0”,但是,只能改写一次,称为PROM。三、可擦除可编程ROM(EPROM)7.1.3可编程ROM(256X1