BICMOS器件介绍.doc

甲申****66

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

BICMOS器件介绍.doc

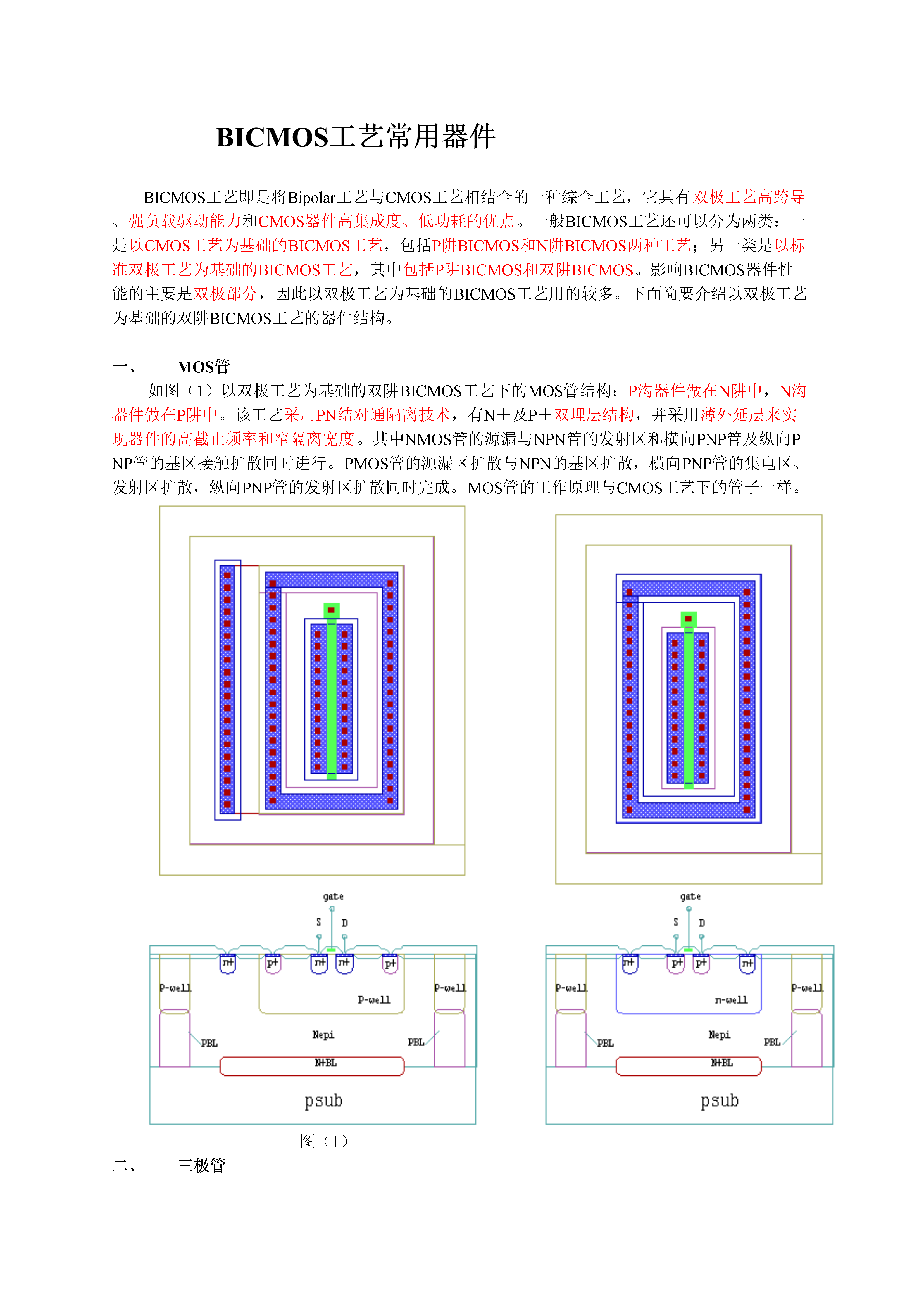

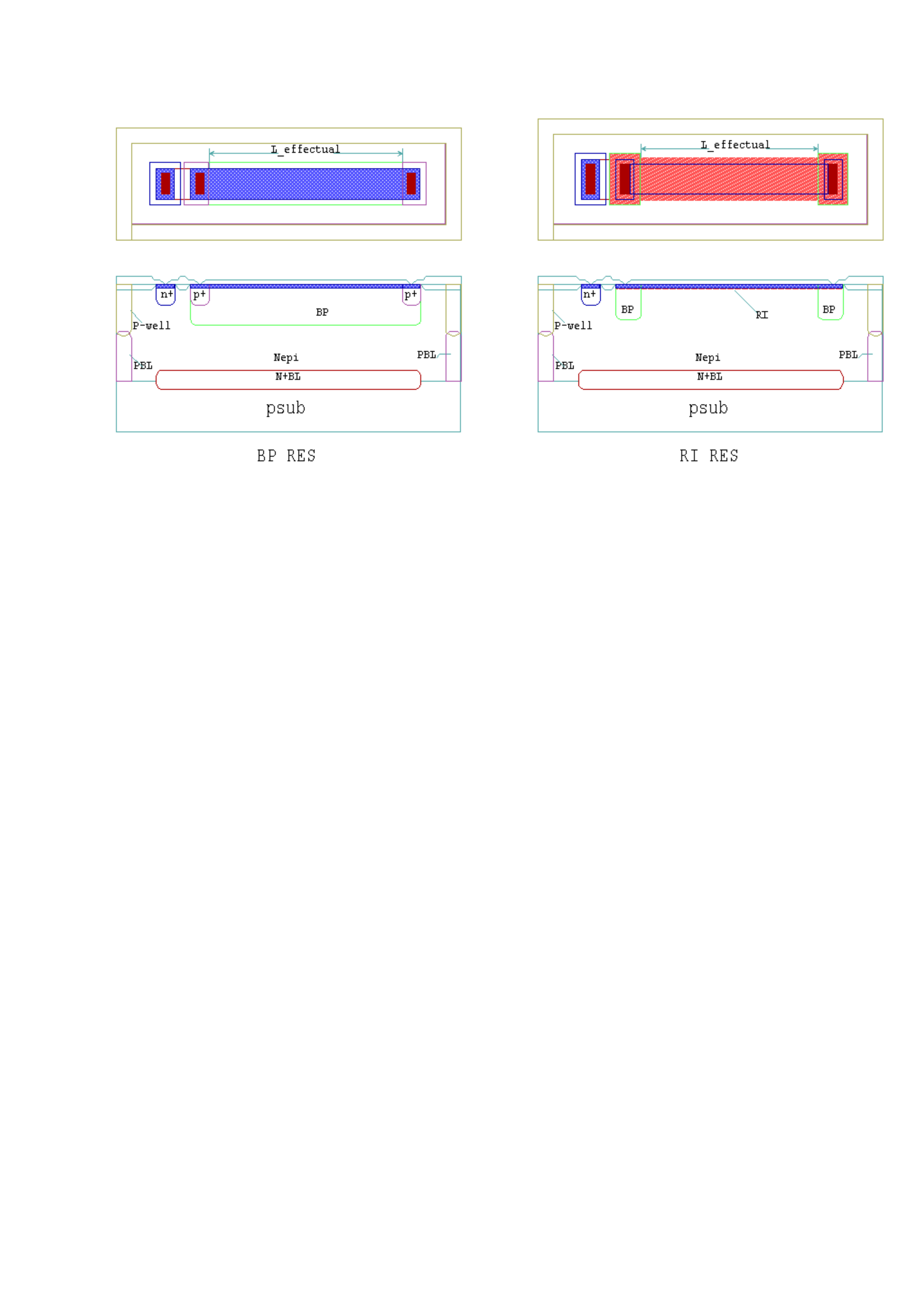

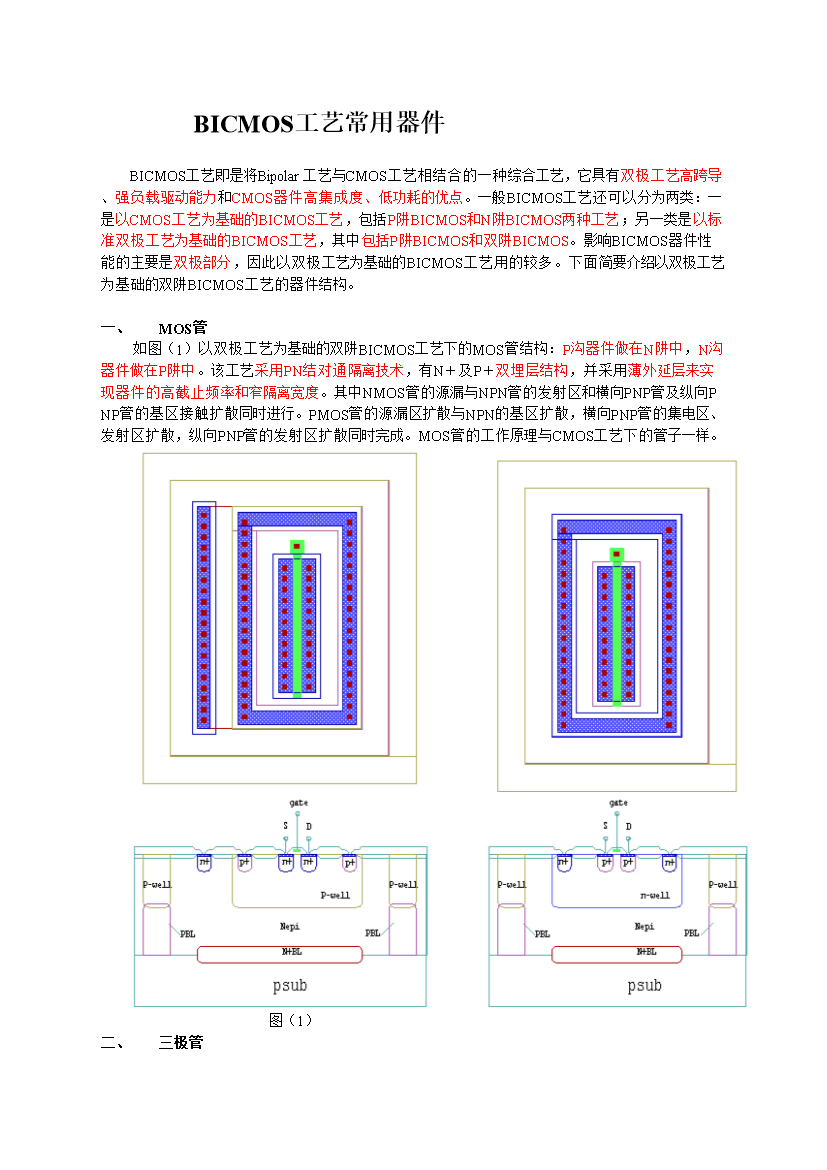

BICMOS工艺常用器件BICMOS工艺即是将Bipolar工艺与CMOS工艺相结合的一种综合工艺它具有双极工艺高跨导、强负载驱动能力和CMOS器件高集成度、低功耗的优点。一般BICMOS工艺还可以分为两类:一是以CMOS工艺为基础的BICMOS工艺包括P阱BICMOS和N阱BICMOS两种工艺;另一类是以标准双极工艺为基础的BICMOS工艺其中包括P阱BICMOS和双阱BICMOS。影响BICMOS器件性能的主要是双极部分因此以双极工艺为基础的BICMOS

BICMOS器件介绍.doc

BICMOS工艺常用器件BICMOS工艺即是将Bipolar工艺与CMOS工艺相结合的一种综合工艺它具有双极工艺高跨导、强负载驱动能力和CMOS器件高集成度、低功耗的优点。一般BICMOS工艺还可以分为两类:一是以CMOS工艺为基础的BICMOS工艺包括P阱BICMOS和N阱BICMOS两种工艺;另一类是以标准双极工艺为基础的BICMOS工艺其中包括P阱BICMOS和双阱BICMOS。影响BICMOS器件性能的主要是双极部分因此以双极工艺为基础的BICMOS

BICMOS器件介绍.doc

BICMOS工艺常用器件BICMOS工艺即是将Bipolar工艺与CMOS工艺相结合的一种综合工艺它具有双极工艺高跨导、强负载驱动能力和CMOS器件高集成度、低功耗的优点。一般BICMOS工艺还可以分为两类:一是以CMOS工艺为基础的BICMOS工艺包括P阱BICMOS和N阱BICMOS两种工艺;另一类是以标准双极工艺为基础的BICMOS工艺其中包括P阱BICMOS和双阱BICMOS。影响BICMOS器件性能的主要是双极部分因此以双极工艺为基础的BICMOS

0.35μm BiCMOS工艺的器件建模.docx

0.35μmBiCMOS工艺的器件建模1.IntroductionBiCMOS(BipolarComplementaryMetal-Oxide-Semiconductor)technologyisacombinationofbipolardevicesandCMOS(ComplementaryMetal-Oxide-Semiconductor)devices.BiCMOStechnologyiswidelyusedinthedesignofhigh-performanceanalogcircuits.In

应变BiCMOS器件及应力分布研究的任务书.docx

应变BiCMOS器件及应力分布研究的任务书任务书一、研究背景BiCMOS(Bipolar-CMOS)器件是一种在同一芯片上集成了CMOS和双极性晶体管(BJT)的混合集成电路技术,它具有高速、低功耗和高可靠性等特性,已经被广泛应用于数字和模拟信号处理系统中。随着集成电路技术的不断发展和应用领域的不断拓展,BiCMOS器件也不断面临新的挑战和需求,如更高的频率、更低的功耗、更小的尺寸和更高的可靠性。在BiCMOS器件设计和制造过程中,应力分布是一个非常重要的问题。应力分布会对器件的性能、可靠性和寿命等方面产