膜上芯片和包括膜上芯片的显示装置.pdf

努力****承悦

亲,该文档总共17页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

膜上芯片和包括膜上芯片的显示装置.pdf

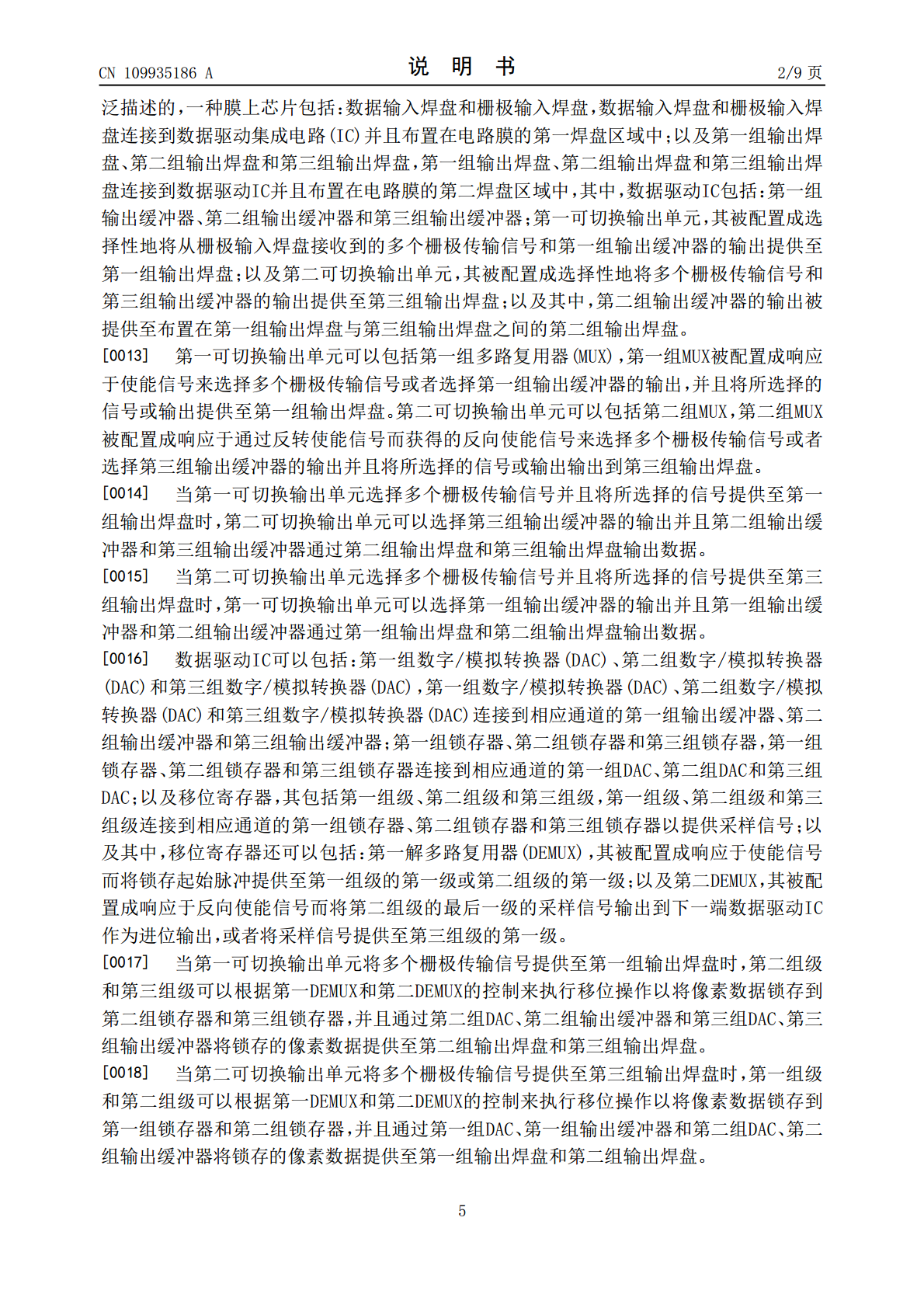

公开了一种膜上芯片和包括膜上芯片的显示装置,该膜上芯片用于选择性地输出栅极传输信号和数据输出以减少数据驱动IC中的输出焊盘的数目。COF包括第一组至第三组数据输入焊盘、栅极输入焊盘和输出焊盘。数据驱动IC包括:第一组至第三组输出缓冲器;第一可切换输出单元,其被配置成选择性地将栅极传输信号和第一组输出缓冲器的输出提供至第一组输出焊盘;以及第二可切换输出单元,其被配置成选择性地将栅极传输信号和第三组输出缓冲器的输出提供至第三组输出焊盘。第二组输出缓冲器的输出被提供至第一组输出焊盘与第三组输出焊盘之间的第二组输

膜上芯片和包括该膜上芯片的显示装置.pdf

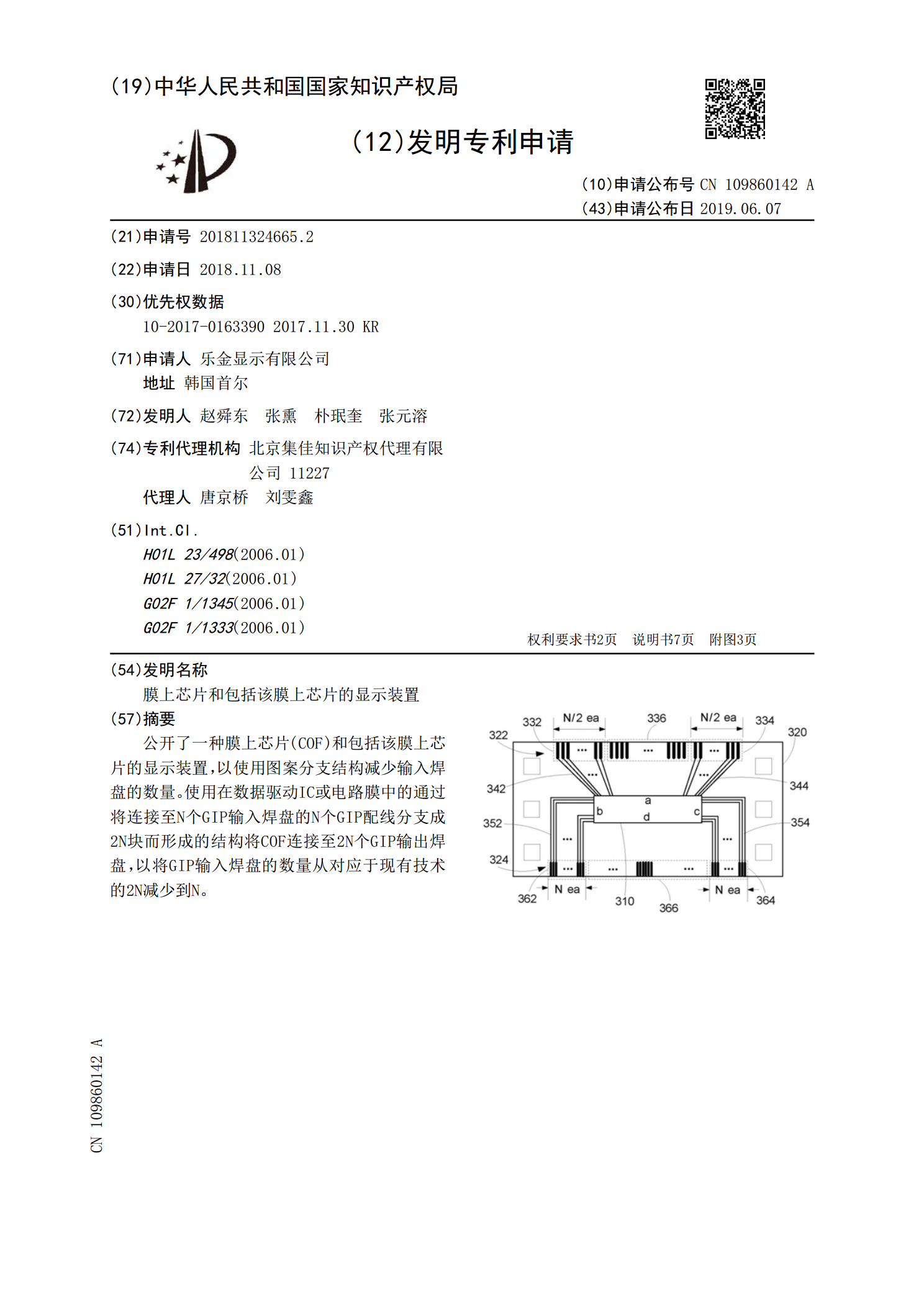

公开了一种膜上芯片(COF)和包括该膜上芯片的显示装置,以使用图案分支结构减少输入焊盘的数量。使用在数据驱动IC或电路膜中的通过将连接至N个GIP输入焊盘的N个GIP配线分支成2N块而形成的结构将COF连接至2N个GIP输出焊盘,以将GIP输入焊盘的数量从对应于现有技术的2N减少到N。

膜上芯片以及包括该膜上芯片的显示装置.pdf

公开了膜上芯片以及包括该膜上芯片的显示装置。该膜上芯片包括:第一基膜;第二基膜,所述第二基膜位于所述第一基膜上;膜焊盘部,所述膜焊盘部位于所述第二基膜的至少一侧并暴露于所述第一基膜的外侧;以及涂层,所述涂层位于所述第一基膜的一个表面上。

驱动芯片、电路膜、膜上芯片型驱动电路及显示装置.pdf

公开一种驱动芯片、电路膜、膜上芯片型驱动电路及显示装置。所述膜上芯片型驱动电路以组合方式执行数据驱动和触摸驱动,并且包括:通过多个数据通道输出图像数据电压的源极驱动电路;通过多个触摸通道输出触摸驱动信号的至少一个触摸驱动电路;和集成电路膜,所述源极驱动电路和所述至少一个触摸驱动电路安装在所述集成电路膜上,其中在所述集成电路膜上设置有多条数据通道线、多条触摸通道线、以及噪声避免线,所述多条数据通道线电连接至所述源极驱动电路的多个数据通道,所述多条触摸通道线电连接至所述触摸驱动电路的多个触摸通道,并且所述噪声

光学膜和包括该光学膜的显示装置.pdf

光学膜和包括该光学膜的显示装置。一种用于显示装置的光学膜,所述光学膜包括:第一网状图案层,在所述第一网状图案层中布置有各自包括第一内孔的多个第一网状图案;以及面对所述第一网状图案层的第二网状图案层,并且在所述第二网状图案层中布置有各自包括第二内孔的多个第二网状图案,其中,所述第一网状图案的中心和所述第二网状图案的中心布置为错位。