一种去除铜导线之间铜残留的方法.pdf

Jo****31

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种去除铜导线之间铜残留的方法.pdf

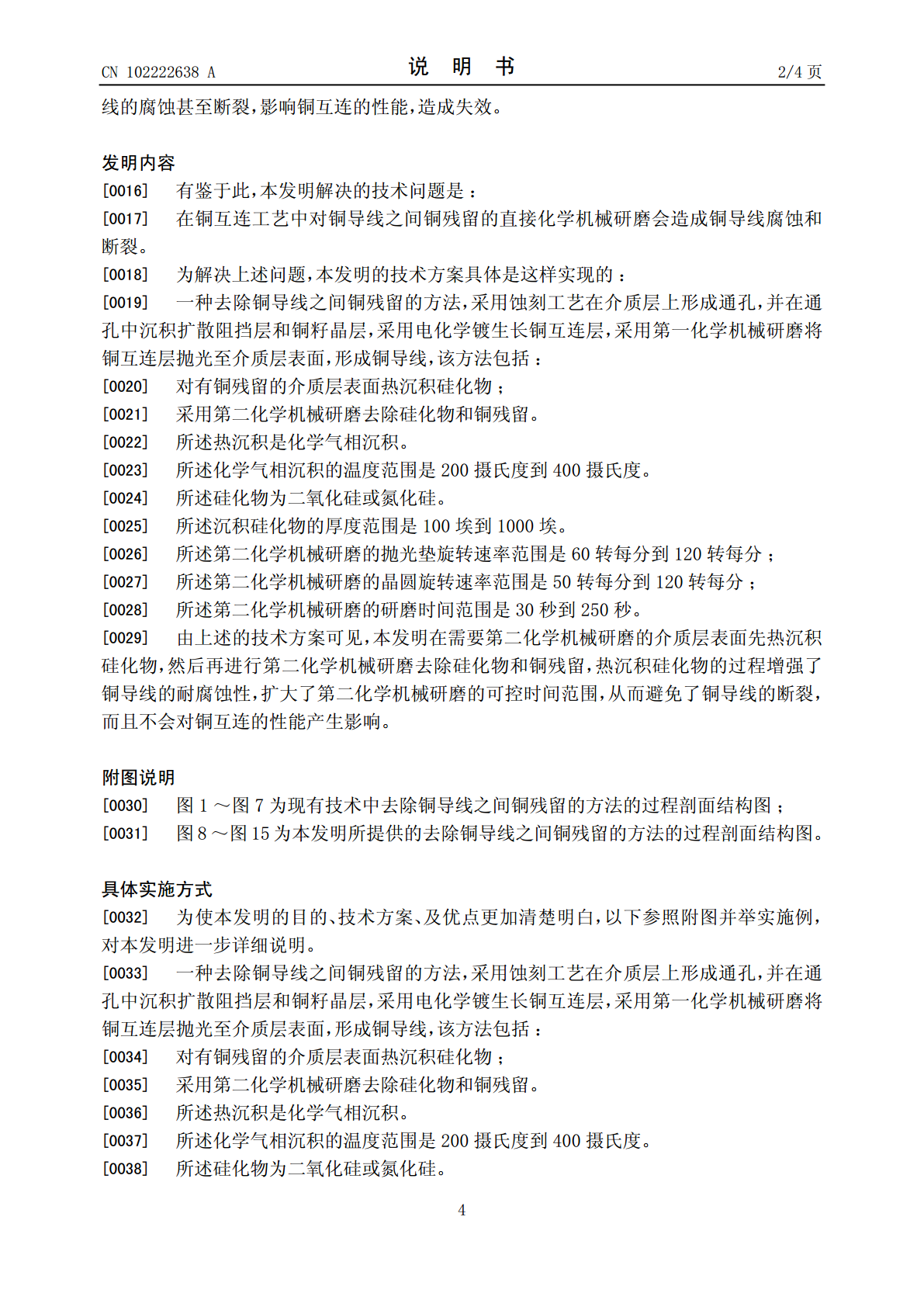

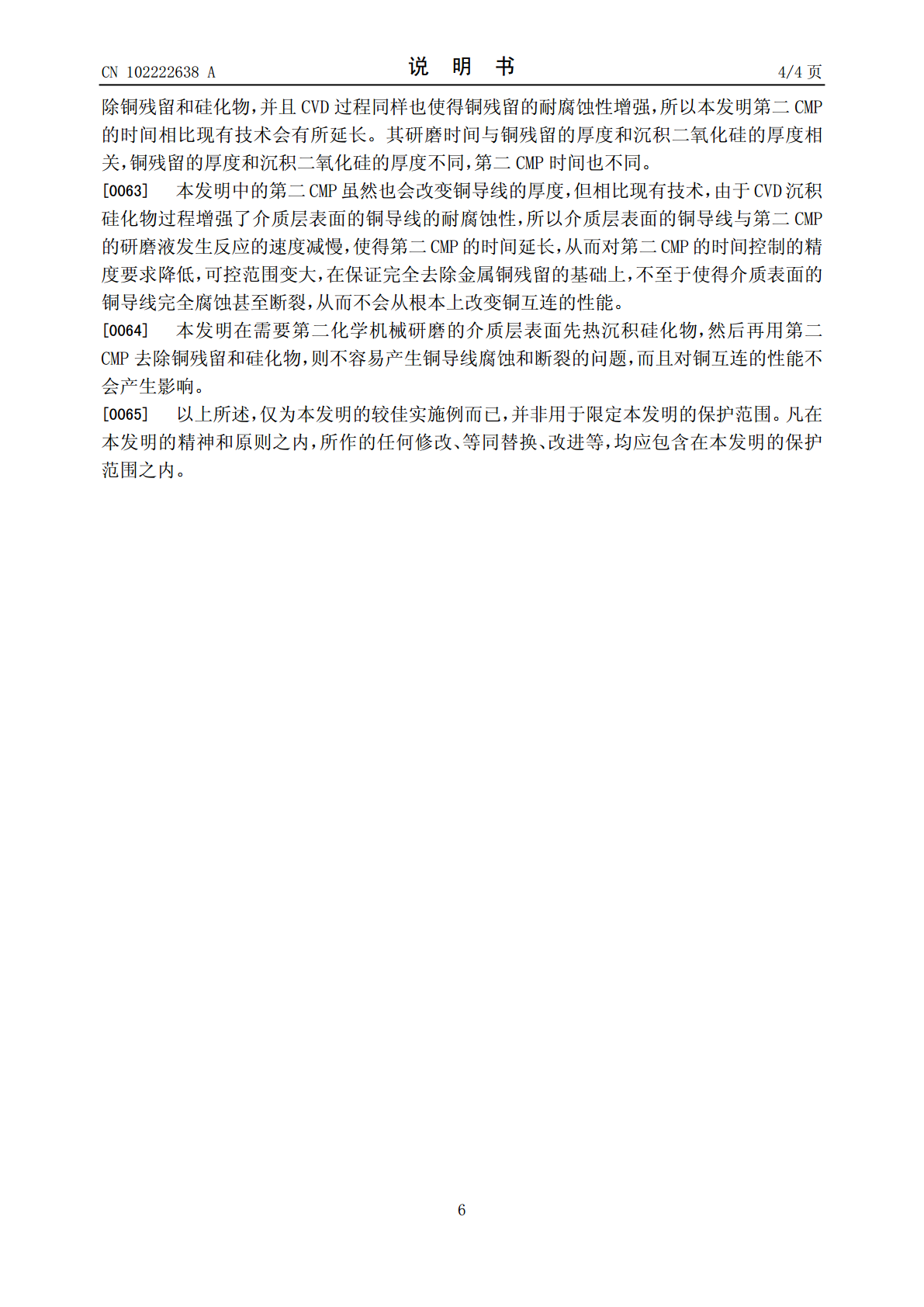

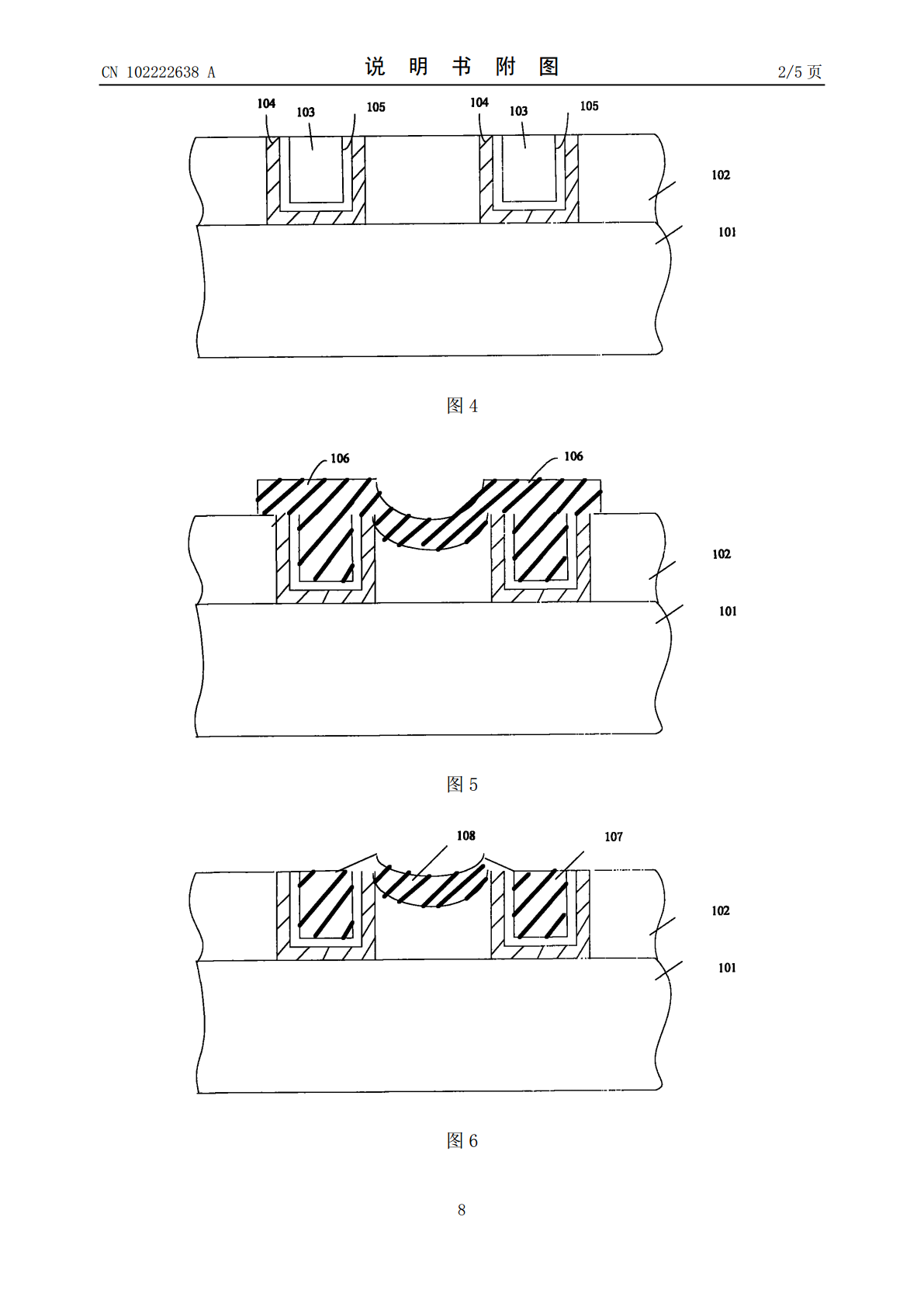

本发明公开了一种去除铜导线之间铜残留的方法,采用蚀刻工艺在介质层上形成通孔,并在通孔中沉积扩散阻挡层和铜籽晶层,采用电化学镀ECP生长铜互连层,采用第一化学机械研磨(CMP)将铜互连层抛光至介质层表面,形成铜导线,该方法包括:在有铜残留的介质层表面热沉积硅化物;采用第二CMP去除硅化物和铜残留。采用该方法增强了铜导线的耐腐蚀性,减缓了第二CMP过程中铜导线与研磨液的反应程度,使第二CMP可控时间范围扩大,从而在完全去除铜残留的基础上,保证铜导线不至于断裂,影响铜互连的性能。

一种去除大豆分离蛋白中残留砷、铅、铜的工艺方法.pdf

本发明公开了一种去除大豆分离蛋白中残留砷、铅、铜的工艺方法,是用1%(w/v)壳聚糖溶液作为吸附剂,对以低温低变性豆粕为原料经碱提、酸沉后获得的蛋白沉淀物加水调节成浓度为10~15%(w/w)的大豆分离蛋白液进行均质;均质后的大豆分离蛋白液在温度为20~30℃,pH值为6.0~6.5的条件下去除砷,在pH值为6.5~7.0的条件下再进行两次吸附去除铅、铜。本发明方法对以低温低变性豆粕为原料并经碱提、酸沉、均质后获得的大豆分离蛋白吸附处理后,产品经原子荧光光度计分析其砷含量≤0.008mg/kg,砷的吸附率

铜导线拉丝方法.pdf

本发明公开了一种铜导线拉丝方法,将铜线从收卷轮上开始放卷,铜线的一端在牵引力的牵拉下向前输送,并经过矫直装置进行矫直处理;将经过矫直处理的铜线送入表面处理装置,由表面处理装置去除铜线表面的杂质并涂上润滑油;铜线送入拉拨装置后,经过拉拨模头后输出,拉拨装置的张力自动调节,完成第一次拉丝等。其具有合理的拉丝步骤,操作方便,能够将铜线拉丝成直径更加精细的铜导线,并实时进行检测,能够有效防止拉丝不均匀现象的产生,提高了铜导线的生产质量。

一种提高铜导线屈服强度的方法.pdf

本发明公开了一种提高铜导线屈服强度的方法,该方法包括如下工艺:用电炉熔炼铜材;用连铸连轧机将熔炼后的铜材热轧成型;将热轧成型后的铜导线冷却后,用挤压成型机挤压;将挤压成型后的铜导线再进行冷轧、拉伸处理;将拉伸处理后的铜导线通过退火炉进行退火处理;将退火处理后的铜导线再通过拉伸机进行拉伸处理。该加工工艺加工后,可有效地消除铜导线的内部应力,提高导线的屈服强度,在不改变材料成分的和冶炼工艺的前提下,可将导线的屈服强度由原来的200~230MPa提高到265MPa,同时还可降低导线的表面硬度,其中的退火工艺简单

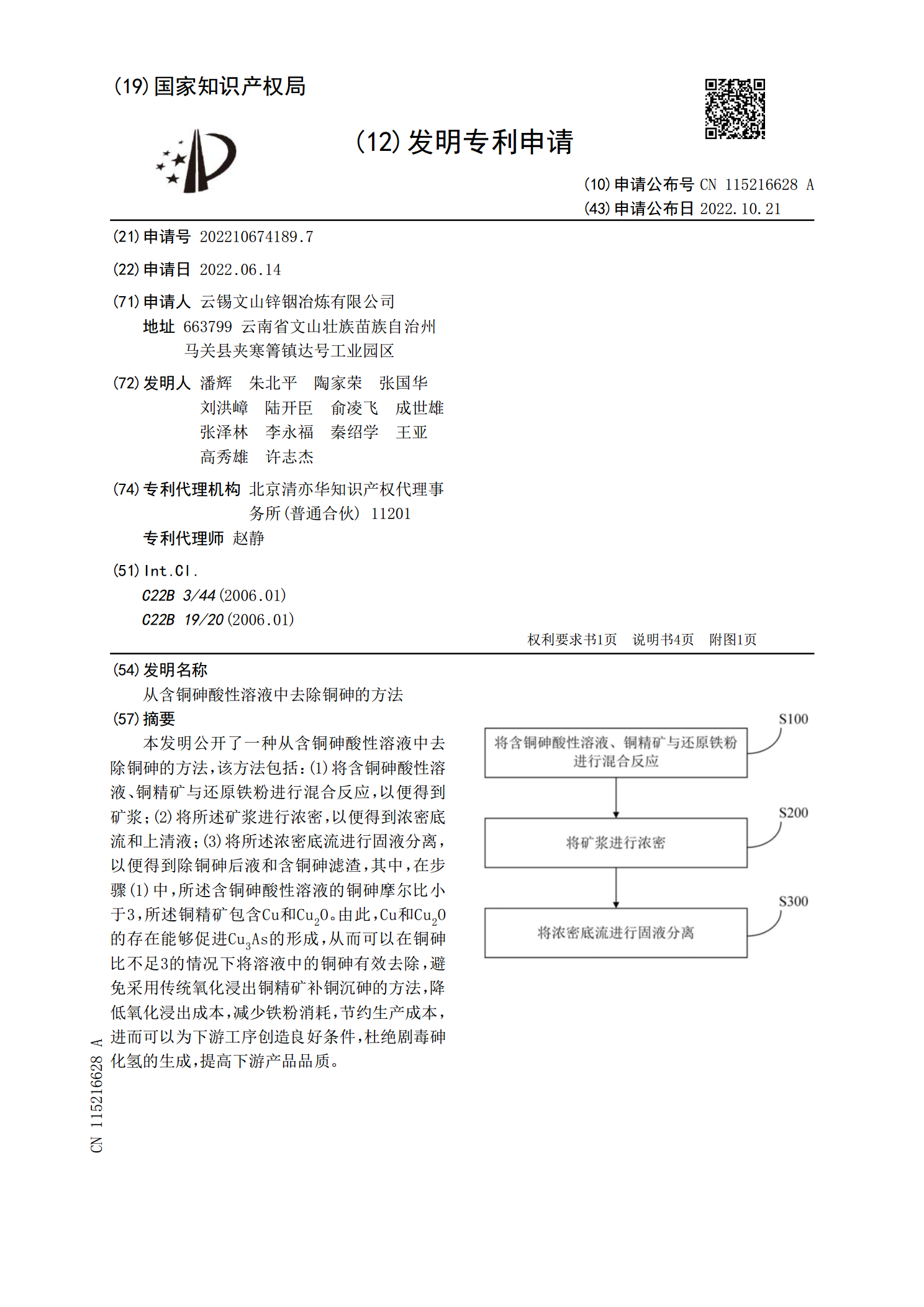

从含铜砷酸性溶液中去除铜砷的方法.pdf

本发明公开了一种从含铜砷酸性溶液中去除铜砷的方法,该方法包括:(1)将含铜砷酸性溶液、铜精矿与还原铁粉进行混合反应,以便得到矿浆;(2)将所述矿浆进行浓密,以便得到浓密底流和上清液;(3)将所述浓密底流进行固液分离,以便得到除铜砷后液和含铜砷滤渣,其中,在步骤(1)中,所述含铜砷酸性溶液的铜砷摩尔比小于3,所述铜精矿包含Cu和Cu<base:Sub>2</base:Sub>O。由此,Cu和Cu<base:Sub>2</base:Sub>O的存在能够促进Cu<base:Sub>3</base:Sub>As的