去除栅介质层的方法.pdf

一条****ee

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

去除栅介质层的方法.pdf

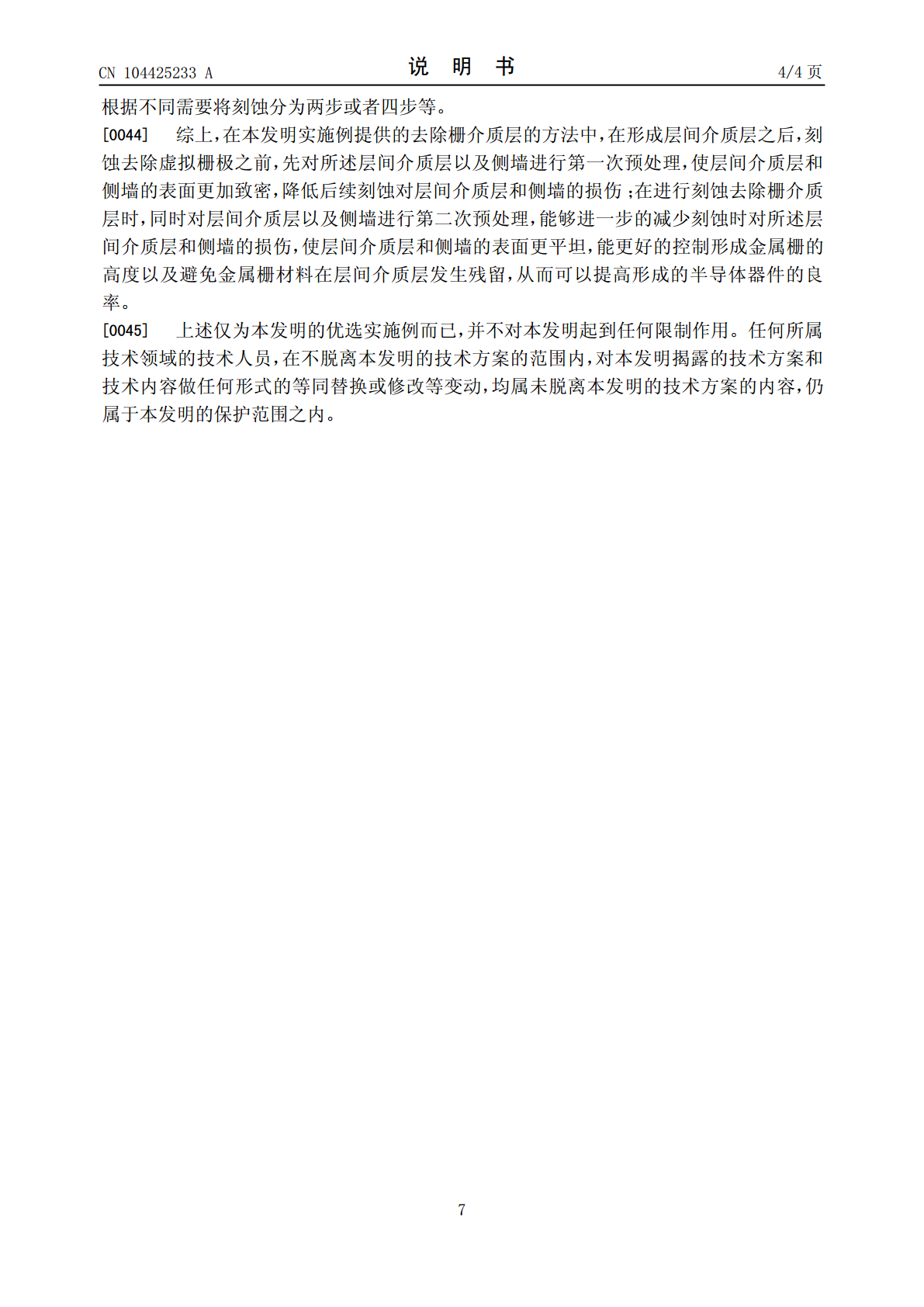

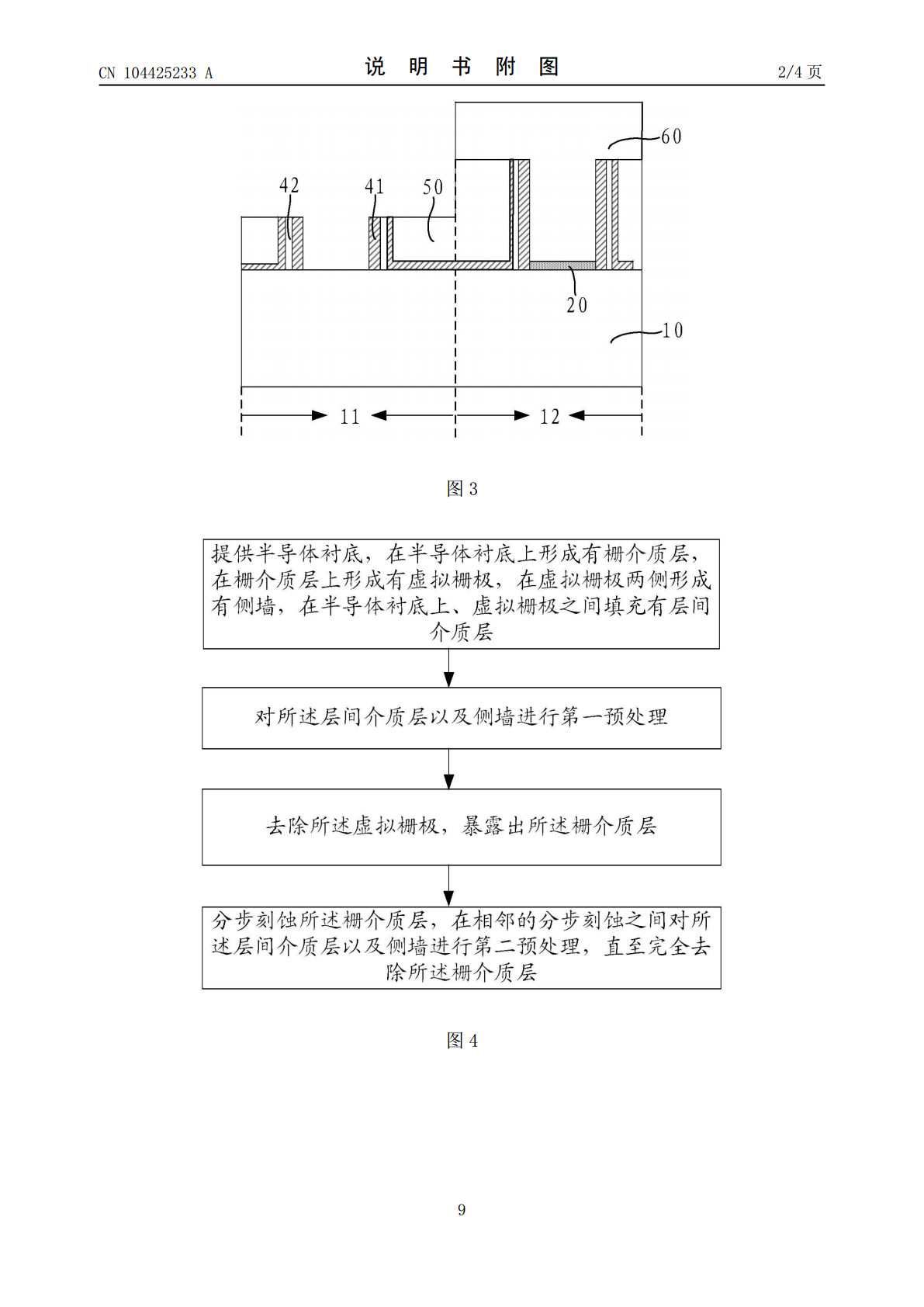

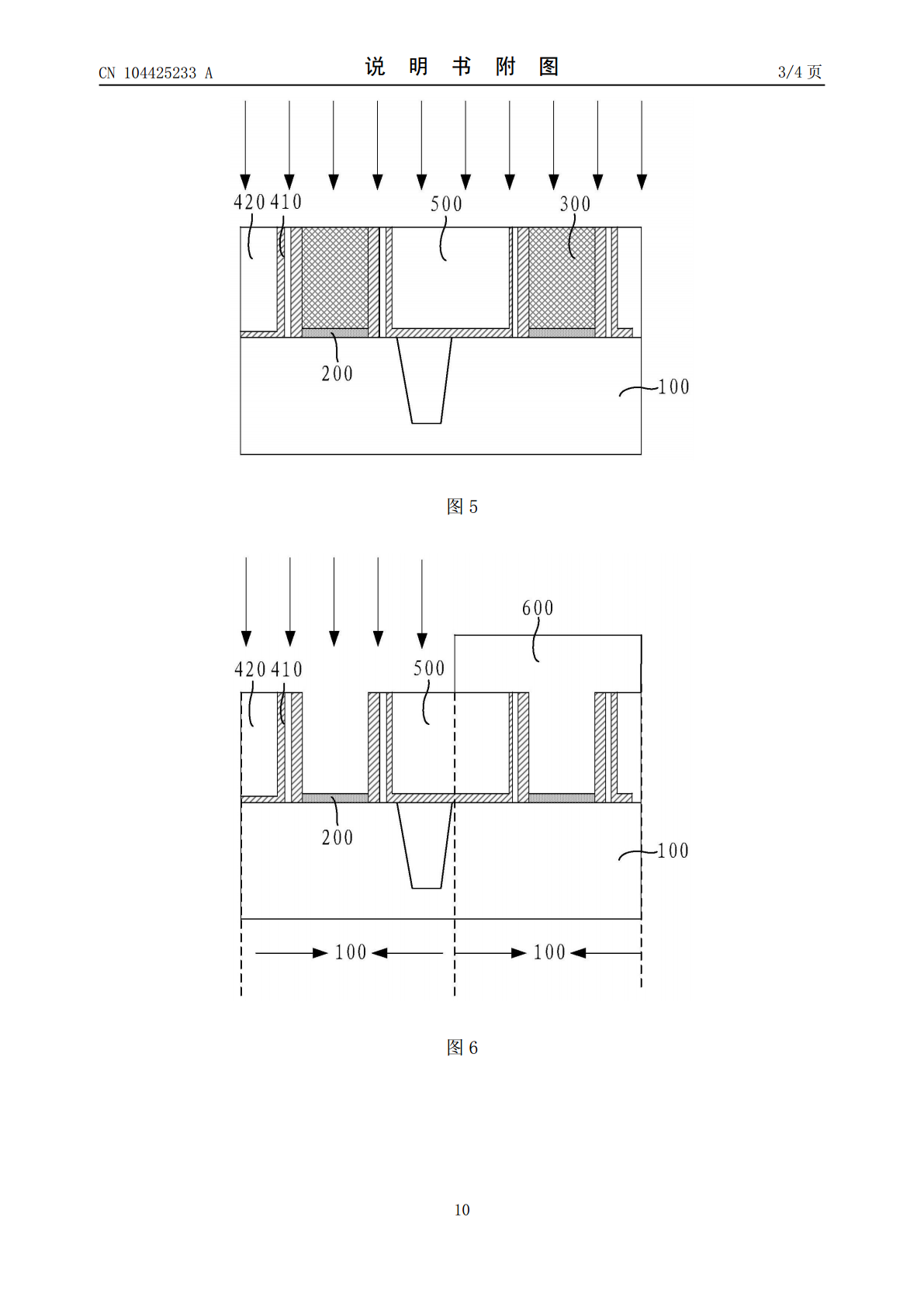

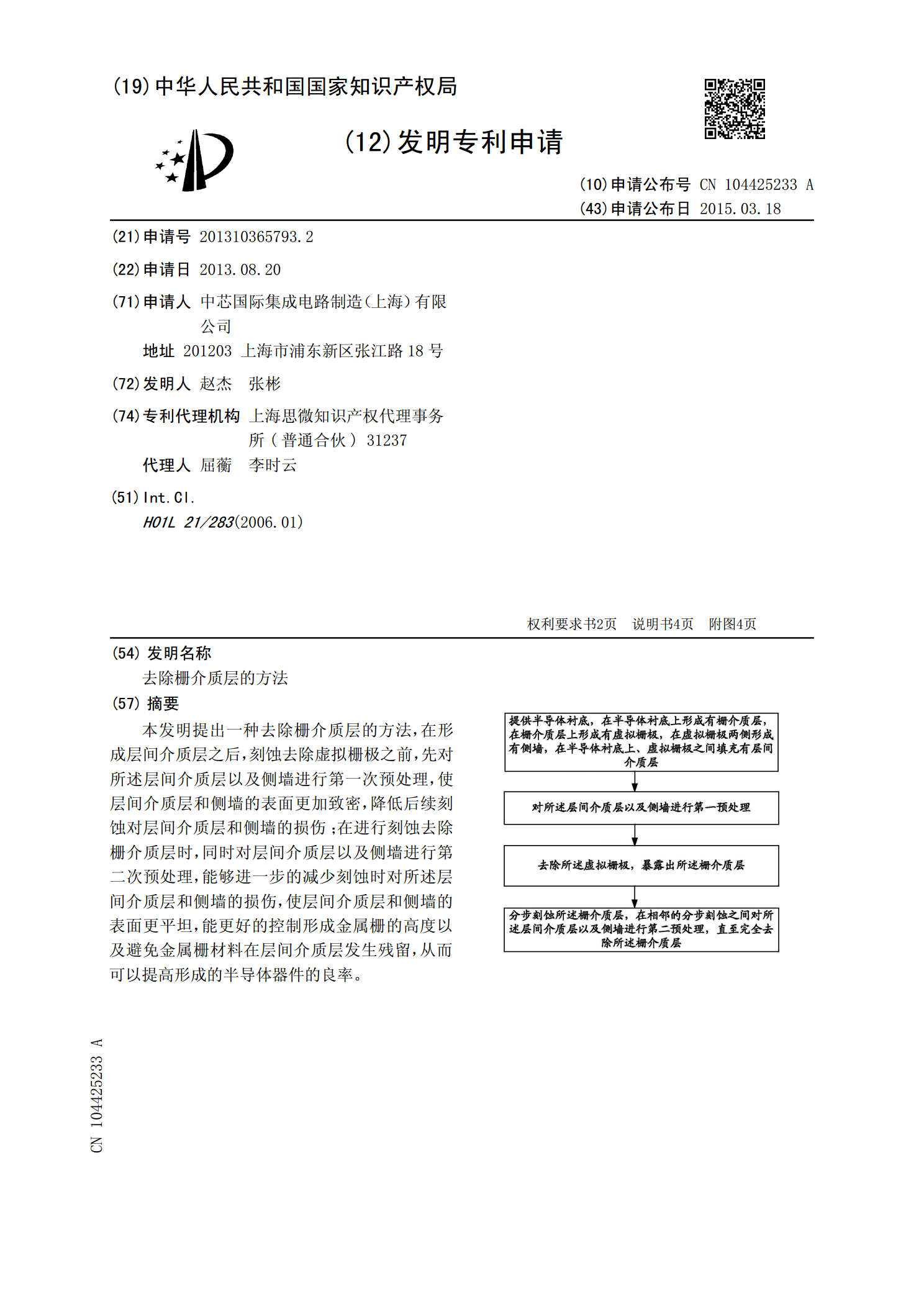

本发明提出一种去除栅介质层的方法,在形成层间介质层之后,刻蚀去除虚拟栅极之前,先对所述层间介质层以及侧墙进行第一次预处理,使层间介质层和侧墙的表面更加致密,降低后续刻蚀对层间介质层和侧墙的损伤;在进行刻蚀去除栅介质层时,同时对层间介质层以及侧墙进行第二次预处理,能够进一步的减少刻蚀时对所述层间介质层和侧墙的损伤,使层间介质层和侧墙的表面更平坦,能更好的控制形成金属栅的高度以及避免金属栅材料在层间介质层发生残留,从而可以提高形成的半导体器件的良率。

高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法.pdf

一种高K栅介质/金属栅叠层栅结构刻蚀后聚合物去除方法,主要步骤如下:1)在器件隔离形成后,在硅衬底上依次形成界面SiO2/高K栅介质/金属栅/多晶硅/硬掩膜叠层栅结构;2)光刻形成胶图形;3)刻蚀叠层栅结构;4)将步骤3的产品浸没于腐蚀溶液中去除聚合物,腐蚀溶液配比为氢氟酸0.2~1%,盐酸5~15%,其余为水。本发明采用氢氟酸(HF)/盐酸(HCl)混合的水溶液化学湿法腐蚀,在室温下就能去净叠栅两侧及硅衬底表面残留的聚合物,不仅保持陡直的叠栅刻蚀剖面,并对硅衬底不造成损伤,与CMOS工艺兼容性好,成本低

金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法.pdf

本发明涉及一种金属栅层/高K栅介质层的叠层结构刻蚀后的清洗方法,属于集成电路制造技术领域。在金属栅层/高K栅介质层叠层结构刻蚀后,采用含有氢氟酸的混合溶液进行清洗,不仅可以完全去除栅叠层结构上留下的含有金属的聚合物残余,而且对于高K材料在干法刻蚀过程中部分去除的刻蚀策略,可以在清洗的过程中完全去除高K材料,从而更有利于满足纳米级CMOS器件在形成栅极图形时对Si衬底损失的要求。另外,因该溶液对场区SiO2的腐蚀速率较低,能够满足器件集成的需要。

去除伪栅多晶硅表面硬质掩膜层的方法.pdf

本发明提供一种去除伪栅多晶硅表面硬质掩膜层的方法,提供衬底,衬底上形成有伪栅,伪栅包括由自下而上的伪栅多晶硅层、氮化层和氧化层以及依次形成于伪栅侧壁上的第一、二侧墙,伪栅的表面形成有第一刻蚀停止层;刻蚀去除第一刻蚀停止层和第二侧墙;在衬底上形成覆盖刻蚀后伪栅的第二刻蚀停止层;形成覆盖第二刻蚀停止层的第一层间介质层,之后研磨第一层间介质层至第二刻蚀停止层的上方;回刻第一层间介质层,使得氧化层去除;形成覆盖剩余的第一层间介质层、氮化层、第二刻蚀停止层、第一侧墙的第二层间介质层;研磨第二层间介质层至伪栅多晶硅层

栅氧化层的制造方法.pdf

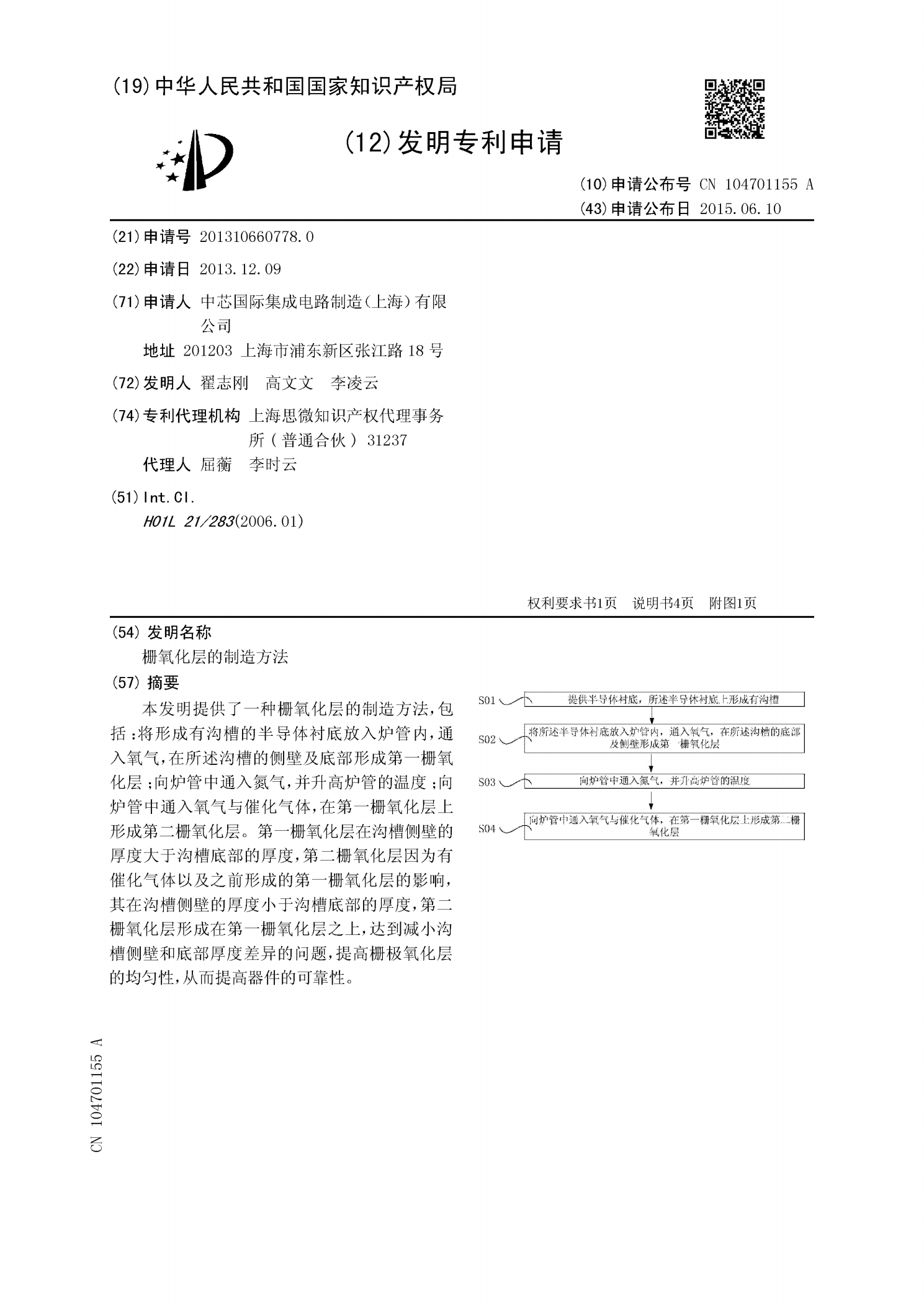

本发明提供了一种栅氧化层的制造方法,包括:将形成有沟槽的半导体衬底放入炉管内,通入氧气,在所述沟槽的侧壁及底部形成第一栅氧化层;向炉管中通入氮气,并升高炉管的温度;向炉管中通入氧气与催化气体,在第一栅氧化层上形成第二栅氧化层。第一栅氧化层在沟槽侧壁的厚度大于沟槽底部的厚度,第二栅氧化层因为有催化气体以及之前形成的第一栅氧化层的影响,其在沟槽侧壁的厚度小于沟槽底部的厚度,第二栅氧化层形成在第一栅氧化层之上,达到减小沟槽侧壁和底部厚度差异的问题,提高栅极氧化层的均匀性,从而提高器件的可靠性。