GOA复位电路及驱动方法、阵列基板、显示面板和装置.pdf

岚风****55

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

GOA复位电路及驱动方法、阵列基板、显示面板和装置.pdf

本发明提供了一种GOA复位电路及驱动方法、阵列基板、显示面板和装置。所述GOA复位电路,用于对GOA单元进行复位,所述GOA单元包括多个输入端,所述GOA复位电路包括:开关单元,接入复位信号,并分别与所述多个输入端连接,用于当所述复位信号有效时,控制所述多个输入端接入高电平信号。发明在GOA单元关机的时候,通过将GOA单元的多个输入端接入高电平信号而打开所有的通道,在节省成和提高散热功能的同时释放残留电荷,消除残影。

阵列基板、显示面板、显示装置和阵列基板的驱动方法.pdf

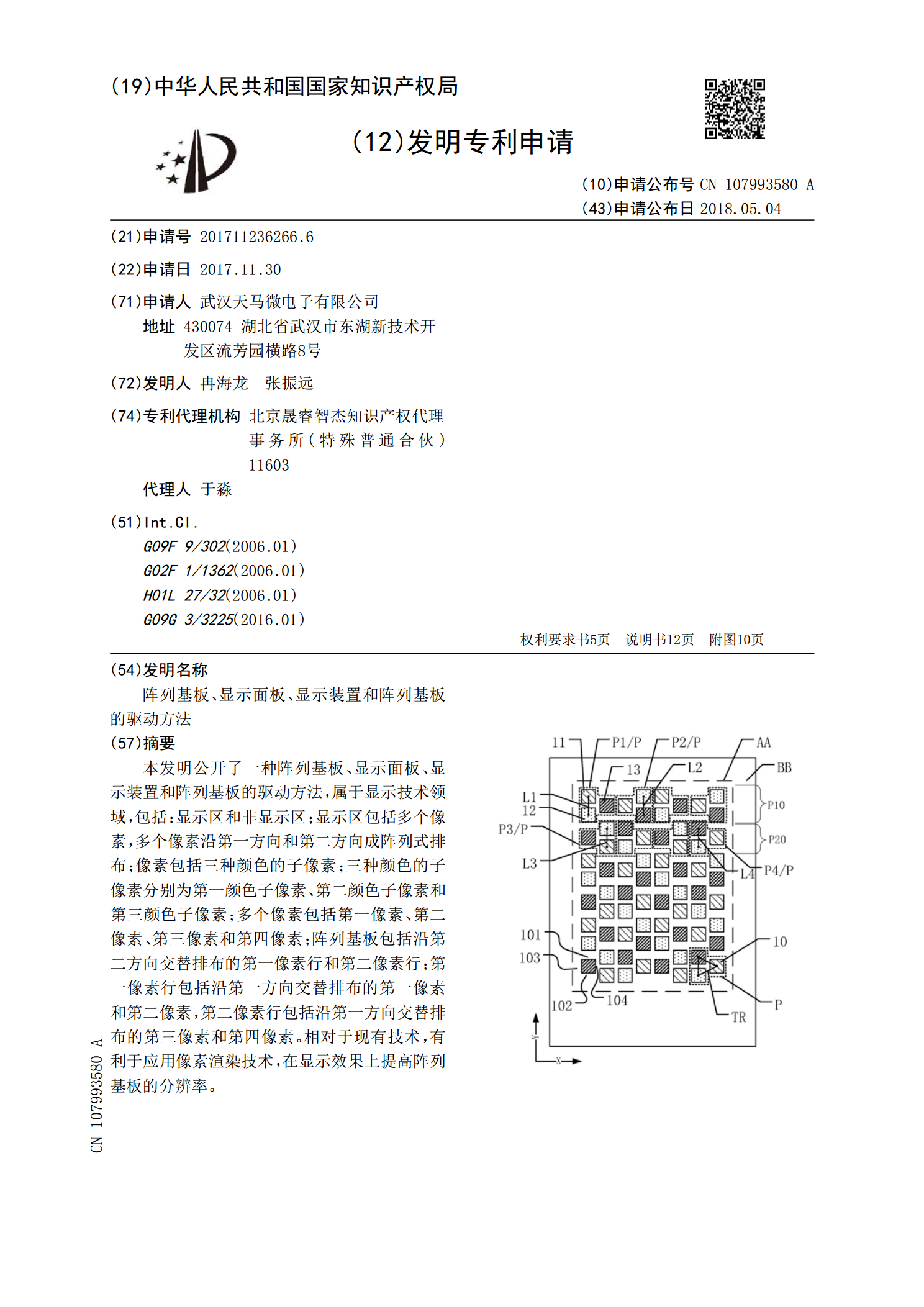

本发明公开了一种阵列基板、显示面板、显示装置和阵列基板的驱动方法,属于显示技术领域,包括:显示区和非显示区;显示区包括多个像素,多个像素沿第一方向和第二方向成阵列式排布;像素包括三种颜色的子像素;三种颜色的子像素分别为第一颜色子像素、第二颜色子像素和第三颜色子像素;多个像素包括第一像素、第二像素、第三像素和第四像素;阵列基板包括沿第二方向交替排布的第一像素行和第二像素行;第一像素行包括沿第一方向交替排布的第一像素和第二像素,第二像素行包括沿第一方向交替排布的第三像素和第四像素。相对于现有技术,有利于应用像

显示面板的驱动电路、阵列基板及其驱动方法.pdf

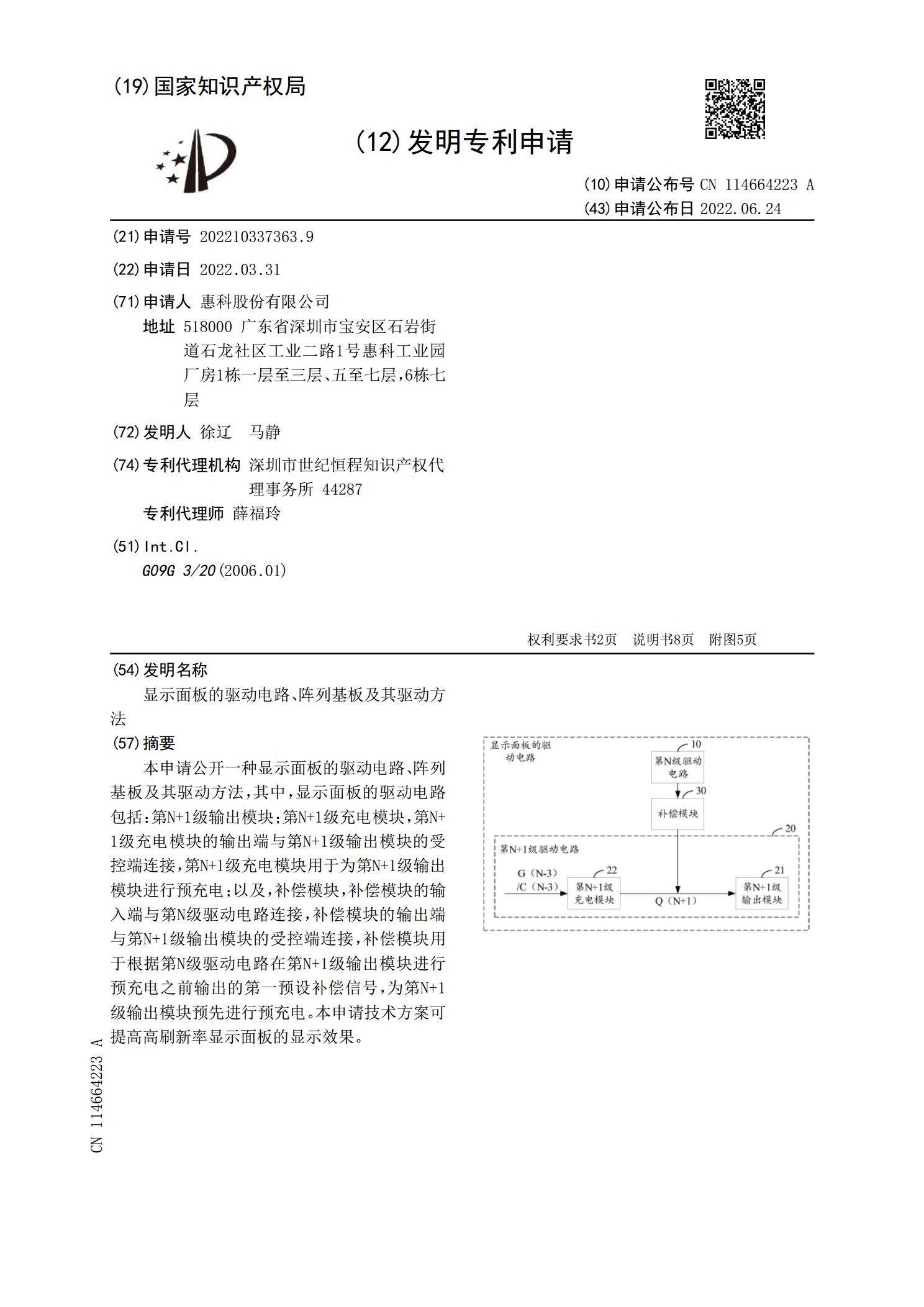

本申请公开一种显示面板的驱动电路、阵列基板及其驱动方法,其中,显示面板的驱动电路包括:第N+1级输出模块;第N+1级充电模块,第N+1级充电模块的输出端与第N+1级输出模块的受控端连接,第N+1级充电模块用于为第N+1级输出模块进行预充电;以及,补偿模块,补偿模块的输入端与第N级驱动电路连接,补偿模块的输出端与第N+1级输出模块的受控端连接,补偿模块用于根据第N级驱动电路在第N+1级输出模块进行预充电之前输出的第一预设补偿信号,为第N+1级输出模块预先进行预充电。本申请技术方案可提高高刷新率显示面板的显示

阵列基板、显示面板及其驱动方法.pdf

本发明公开了一种阵列基板、显示面板及其驱动方法,所述阵列基板包括多条栅线和多条数据线,多条所述栅线和多条所述数据线将该阵列基板划分为多个像素单元,每个所述像素单元内包括一个开关晶体管,每个所述像素单元内还包括一个放电模块,所述放电模块的控制端与该像素单元所在行的上一行栅线相连,所述放电模块用于在扫描上一行栅线时,将本行像素单元的像素电极与低电平信号端导通。本发明通过设置放电模块,能够在每个像素单元显示之前将其像素电极上残留的电荷充分释放掉,避免了极性翻转过程中残留电荷的积累,从而能够避免残像现象的发生,改

GOA电路、显示面板和显示装置.pdf

本申请提供一种驱动电路、显示面板和显示装置,该驱动电路包括多个级联的驱动单元,每个驱动单元具体包括上拉控制电路、下拉电路、下拉保持电路、自举电路、放电电路和重置电路,其中,放电电路包括第十四薄膜晶体管和第十二薄膜晶体管,通过设置第十四薄膜晶体管,可以防止在扫黑阶段由于第十二薄膜晶体管的栅极的自举电压反灌而导致的栅极电压降低,从而使第十二薄膜晶体管充分打开,提高输出电压,使放电电路充分放电,避免了由于扫黑阶段电荷残留而引起的异常显示的情况的发生,在无须限制放电电路中薄膜晶体管的大小的情况下保证了扫黑效果,大