GOA电路、显示面板和显示装置.pdf

小琛****82

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

GOA电路、显示面板和显示装置.pdf

本申请提供一种驱动电路、显示面板和显示装置,该驱动电路包括多个级联的驱动单元,每个驱动单元具体包括上拉控制电路、下拉电路、下拉保持电路、自举电路、放电电路和重置电路,其中,放电电路包括第十四薄膜晶体管和第十二薄膜晶体管,通过设置第十四薄膜晶体管,可以防止在扫黑阶段由于第十二薄膜晶体管的栅极的自举电压反灌而导致的栅极电压降低,从而使第十二薄膜晶体管充分打开,提高输出电压,使放电电路充分放电,避免了由于扫黑阶段电荷残留而引起的异常显示的情况的发生,在无须限制放电电路中薄膜晶体管的大小的情况下保证了扫黑效果,大

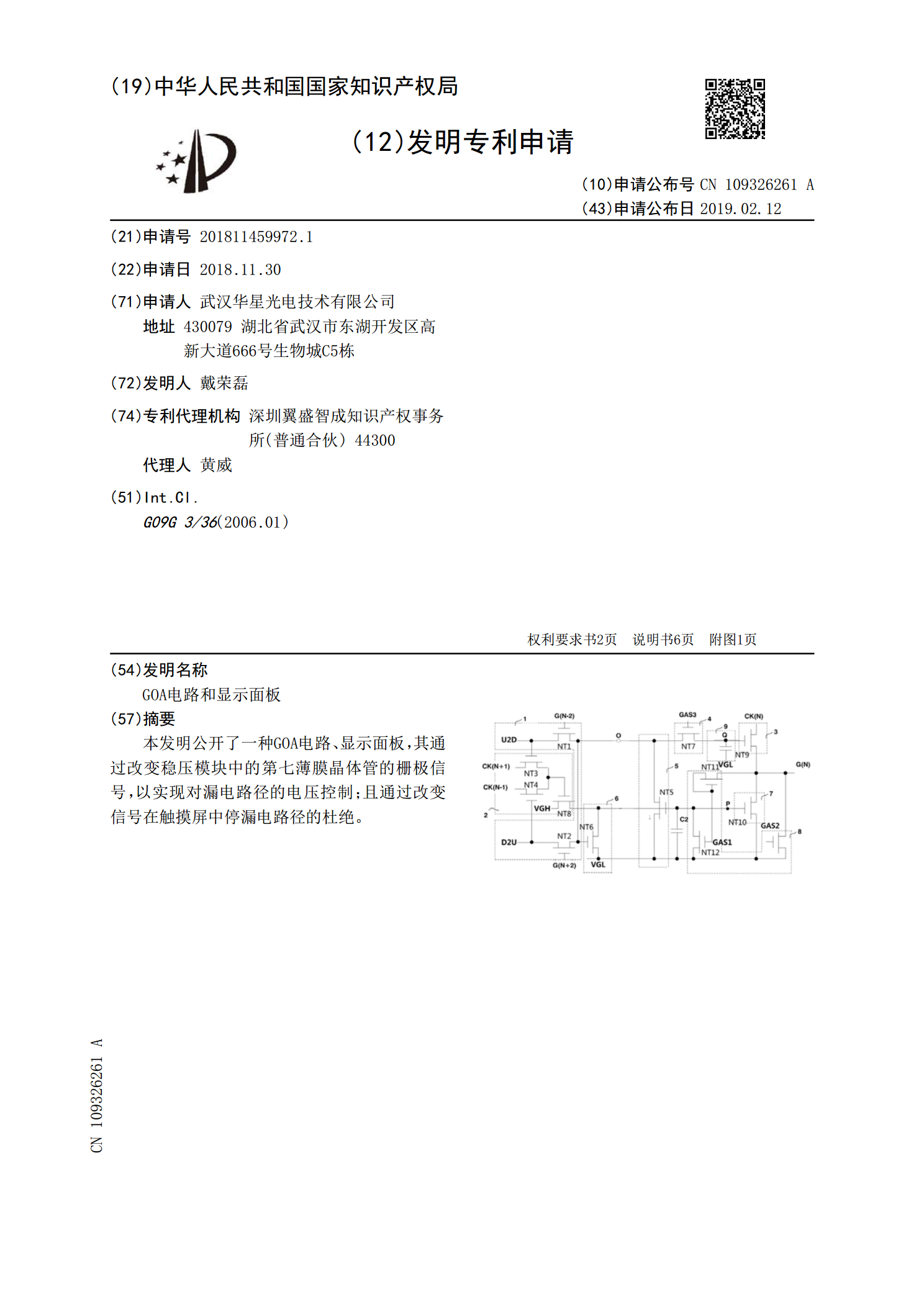

GOA电路和显示面板.pdf

本发明公开了一种GOA电路、显示面板,其通过改变稳压模块中的第七薄膜晶体管的栅极信号,以实现对漏电路径的电压控制;且通过改变信号在触摸屏中停漏电路径的杜绝。

显示面板GOA电路.pdf

本发明涉及一种显示面板GOA电路。该显示面板GOA电路包括级联的多个GOA单元,设n、m为自然数,第n级GOA单元的上拉控制电路包括:第一薄膜晶体管(T1),栅极连接第n+m级水平扫描信号,源极和漏极分别连接高电位和栅极信号点;第二薄膜晶体管(T2),栅极为悬空状态并且预留用于连接起始信号(STV)的焊接点位,源极和漏极分别连接高电位和栅极信号点;下拉控制电路包括:第三薄膜晶体管(T4),栅极连接第n-m级水平扫描信号,源极和漏极分别连接第n级水平扫描信号和低电位;第四薄膜晶体管(T5),栅极连接第n-m

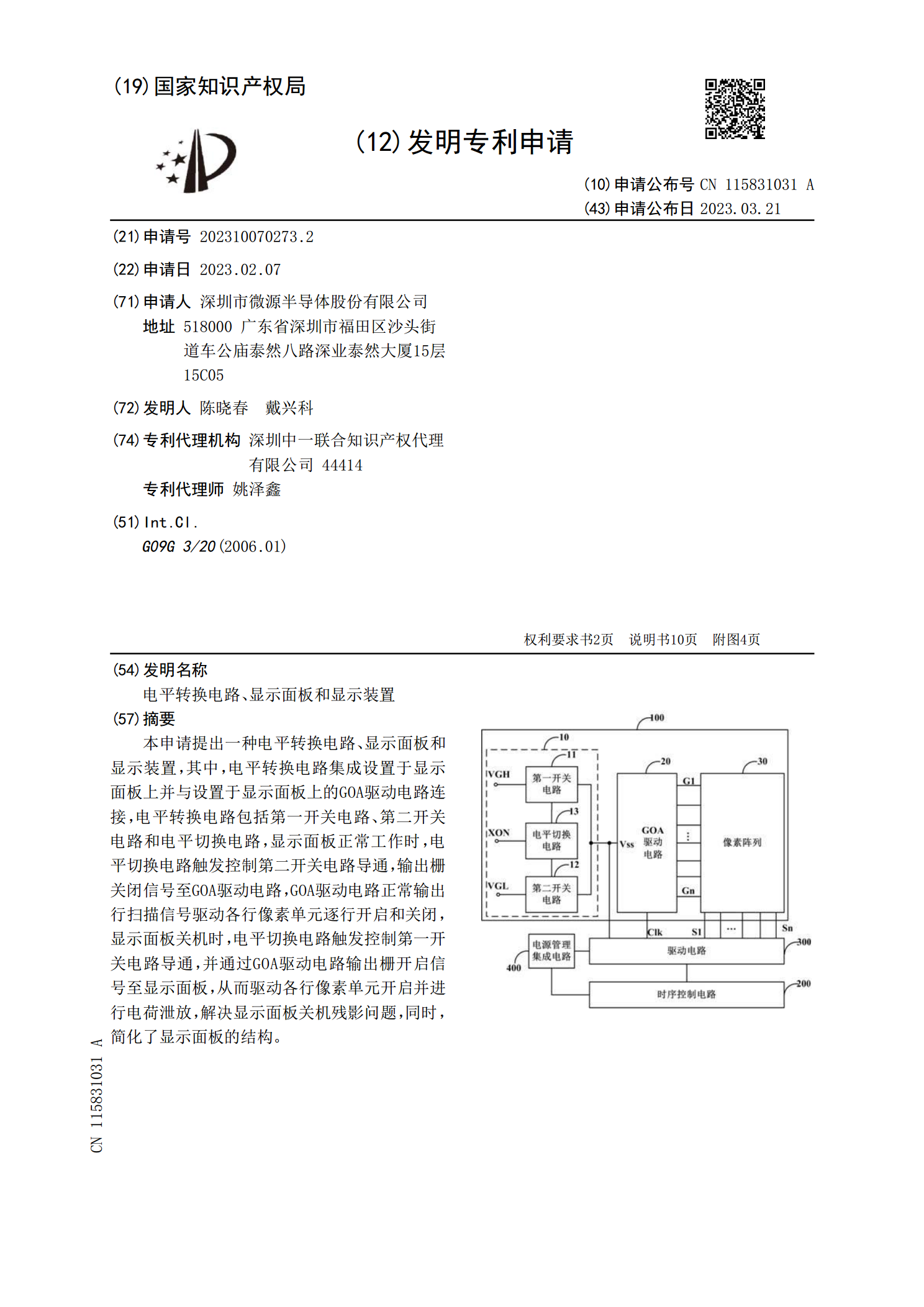

电平转换电路、显示面板和显示装置.pdf

本申请提出一种电平转换电路、显示面板和显示装置,其中,电平转换电路集成设置于显示面板上并与设置于显示面板上的GOA驱动电路连接,电平转换电路包括第一开关电路、第二开关电路和电平切换电路,显示面板正常工作时,电平切换电路触发控制第二开关电路导通,输出栅关闭信号至GOA驱动电路,GOA驱动电路正常输出行扫描信号驱动各行像素单元逐行开启和关闭,显示面板关机时,电平切换电路触发控制第一开关电路导通,并通过GOA驱动电路输出栅开启信号至显示面板,从而驱动各行像素单元开启并进行电荷泄放,解决显示面板关机残影问题,同时

数据驱动电路、显示面板和显示装置.pdf

本发明涉及数据驱动电路、显示面板和显示装置。根据本发明的实施方式,可以防止在低速驱动模式下识别出闪烁。显示面板包括:发光元件;用于驱动发光元件的驱动晶体管,包括电连接到驱动电压线的第一节点、作为栅极节点的第二节点、和电连接到发光元件的第三节点;以及扫描晶体管,电连接在第三节点和数据线之间,其中,在低速驱动模式下,在帧周期的第一区间中将数据电压施加到数据线,在帧周期的第二区间中至少一次将复位电压施加到数据线,其中,在将第一电平的驱动电压施加到驱动电压线时,施加到数据线的复位电压的第一电平与在将与第一电平的驱