一种键合晶圆结构及其制备方法.pdf

一只****呀盟

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

键合晶圆结构及其制备方法.pdf

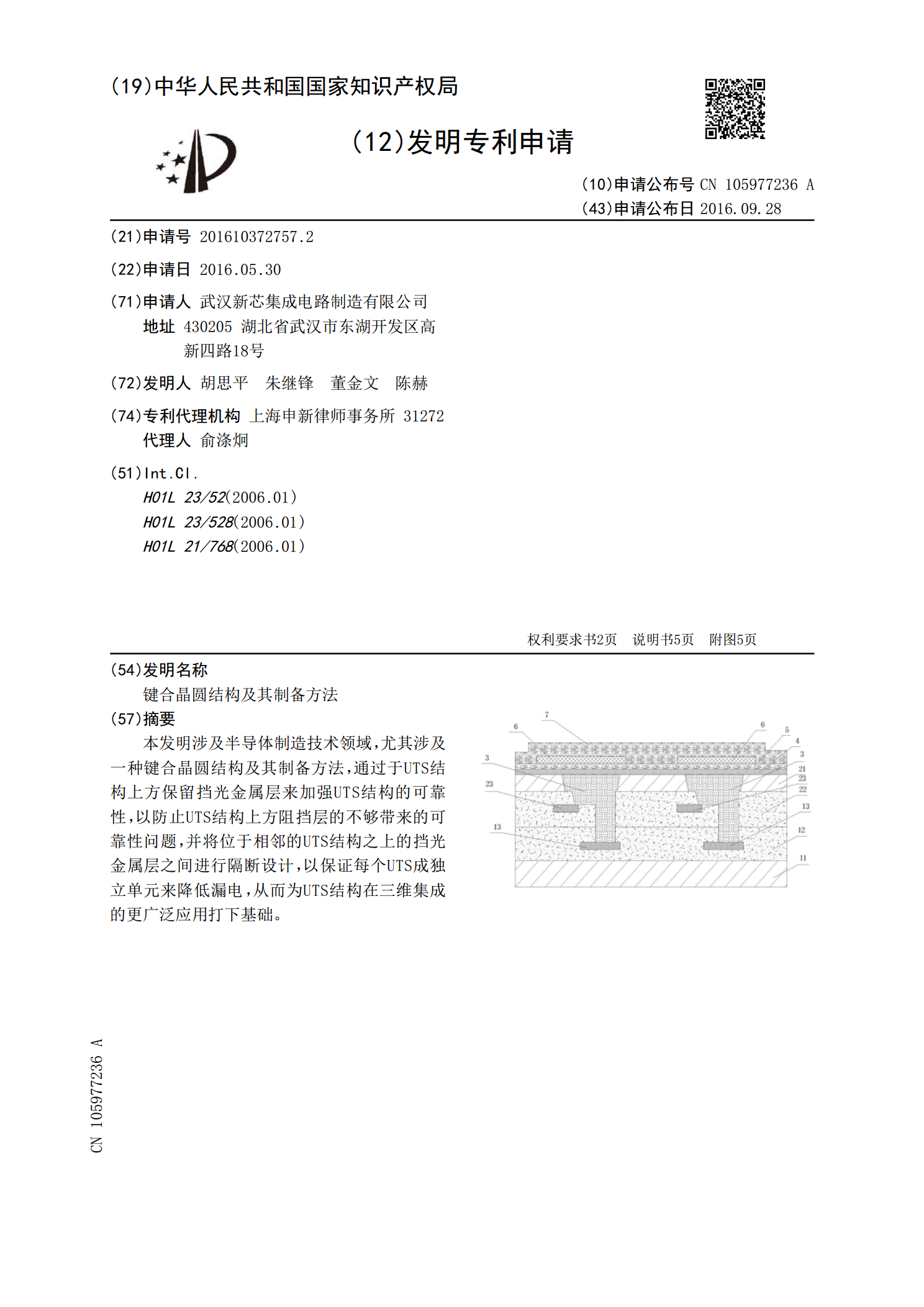

本发明涉及半导体制造技术领域,尤其涉及一种键合晶圆结构及其制备方法,通过于UTS结构上方保留挡光金属层来加强UTS结构的可靠性,以防止UTS结构上方阻挡层的不够带来的可靠性问题,并将位于相邻的UTS结构之上的挡光金属层之间进行隔断设计,以保证每个UTS成独立单元来降低漏电,从而为UTS结构在三维集成的更广泛应用打下基础。

一种键合晶圆结构及其制备方法.pdf

本发明涉及半导体制造技术领域,尤其涉及一种键合晶圆结构及其制备方法,通过于UTS结构上方保留挡光金属层来加强UTS结构的可靠性,以防止UTS结构上方阻挡层的不够带来的可靠性问题,无需增加额外的光罩即可实现,为UTS结构在三维集成的更广泛应用打下基础。

晶圆键合方法及晶圆键合结构.pdf

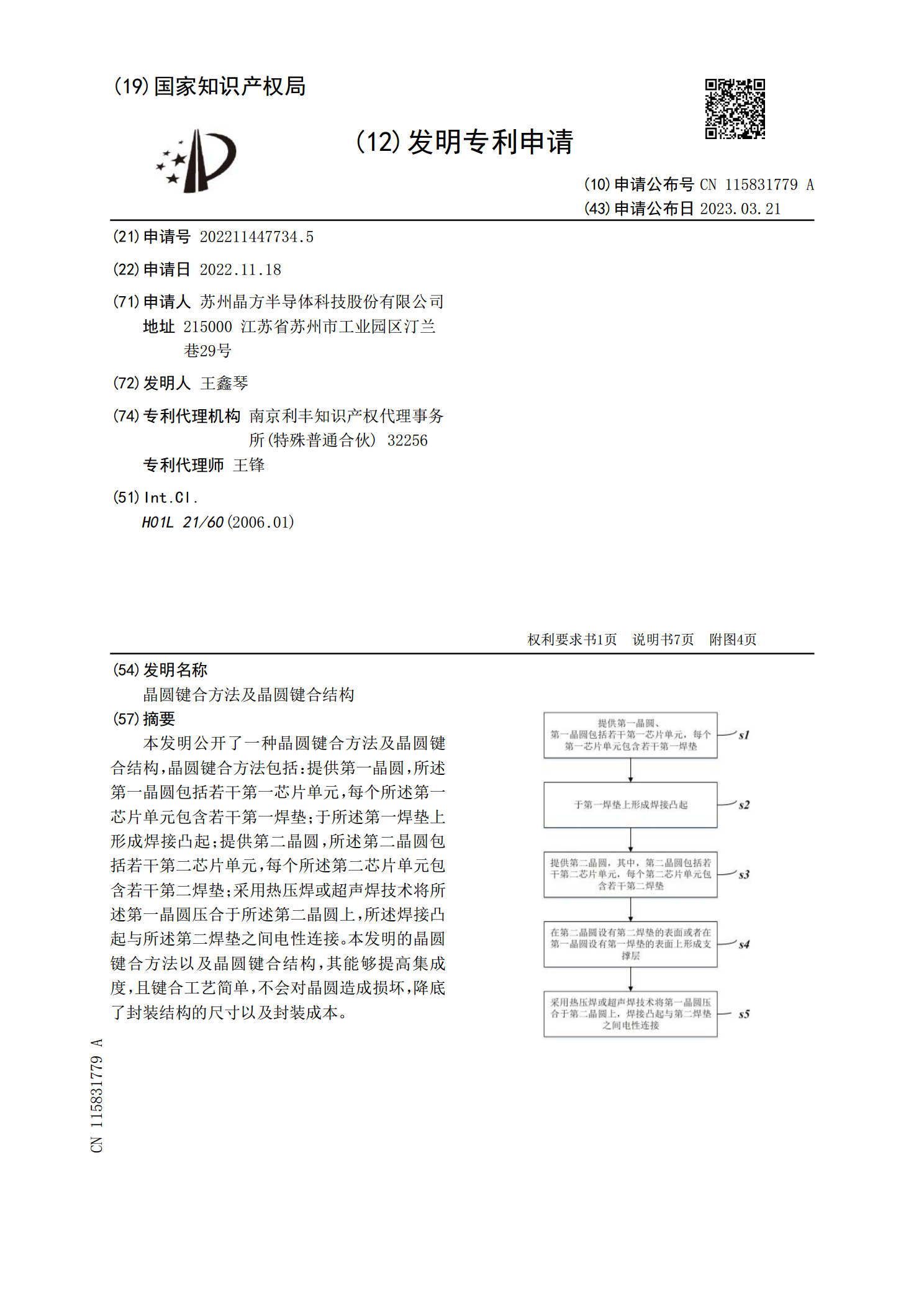

本发明公开了一种晶圆键合方法及晶圆键合结构,晶圆键合方法包括:提供第一晶圆,所述第一晶圆包括若干第一芯片单元,每个所述第一芯片单元包含若干第一焊垫;于所述第一焊垫上形成焊接凸起;提供第二晶圆,所述第二晶圆包括若干第二芯片单元,每个所述第二芯片单元包含若干第二焊垫;采用热压焊或超声焊技术将所述第一晶圆压合于所述第二晶圆上,所述焊接凸起与所述第二焊垫之间电性连接。本发明的晶圆键合方法以及晶圆键合结构,其能够提高集成度,且键合工艺简单,不会对晶圆造成损坏,降底了封装结构的尺寸以及封装成本。

一种晶圆键合方法及键合结构.pdf

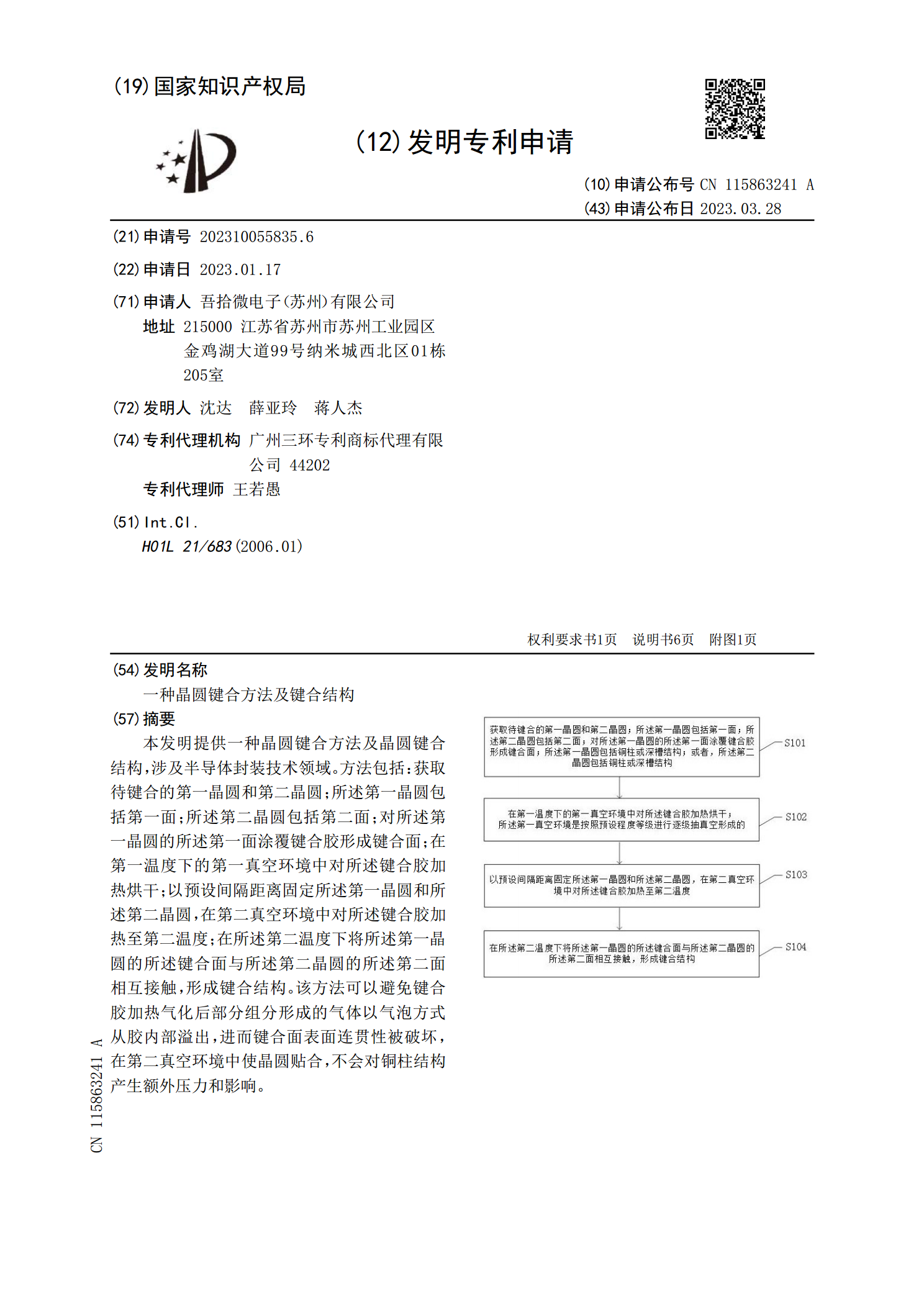

本发明提供一种晶圆键合方法及晶圆键合结构,涉及半导体封装技术领域。方法包括:获取待键合的第一晶圆和第二晶圆;所述第一晶圆包括第一面;所述第二晶圆包括第二面;对所述第一晶圆的所述第一面涂覆键合胶形成键合面;在第一温度下的第一真空环境中对所述键合胶加热烘干;以预设间隔距离固定所述第一晶圆和所述第二晶圆,在第二真空环境中对所述键合胶加热至第二温度;在所述第二温度下将所述第一晶圆的所述键合面与所述第二晶圆的所述第二面相互接触,形成键合结构。该方法可以避免键合胶加热气化后部分组分形成的气体以气泡方式从胶内部溢出,进

键合标记的制备方法、晶圆键合方法、键合标记及半导体器件.pdf

本发明提供了一种键合标记的制备方法,包括:步骤S1:在承载晶圆上通过刻蚀形成沟槽;步骤S2:在沟槽中填充金属;步骤S3:除去承载晶圆表面的金属,以保留所述沟槽中填充的金属,从而在所述承载晶圆上形成键合标记。所述键合标记的制备方法在蚀刻形成沟槽后,通过在沟槽中沉积金属改善标记表面的识别,并降低沟槽带来的键合空隙的风险,提高键合质量。进一步,本发明还提供了一种基于上述的方法制备得到的键合标记,所述键合标记具有清晰的分界线,易于识别,降低识别的失败率,能够减少晶圆报废率,提高产能。再进一步,本发明还提供了一种晶