薄膜晶体管及其制备方法、阵列基板.pdf

是你****元呀

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

薄膜晶体管阵列基板及其制备方法.pdf

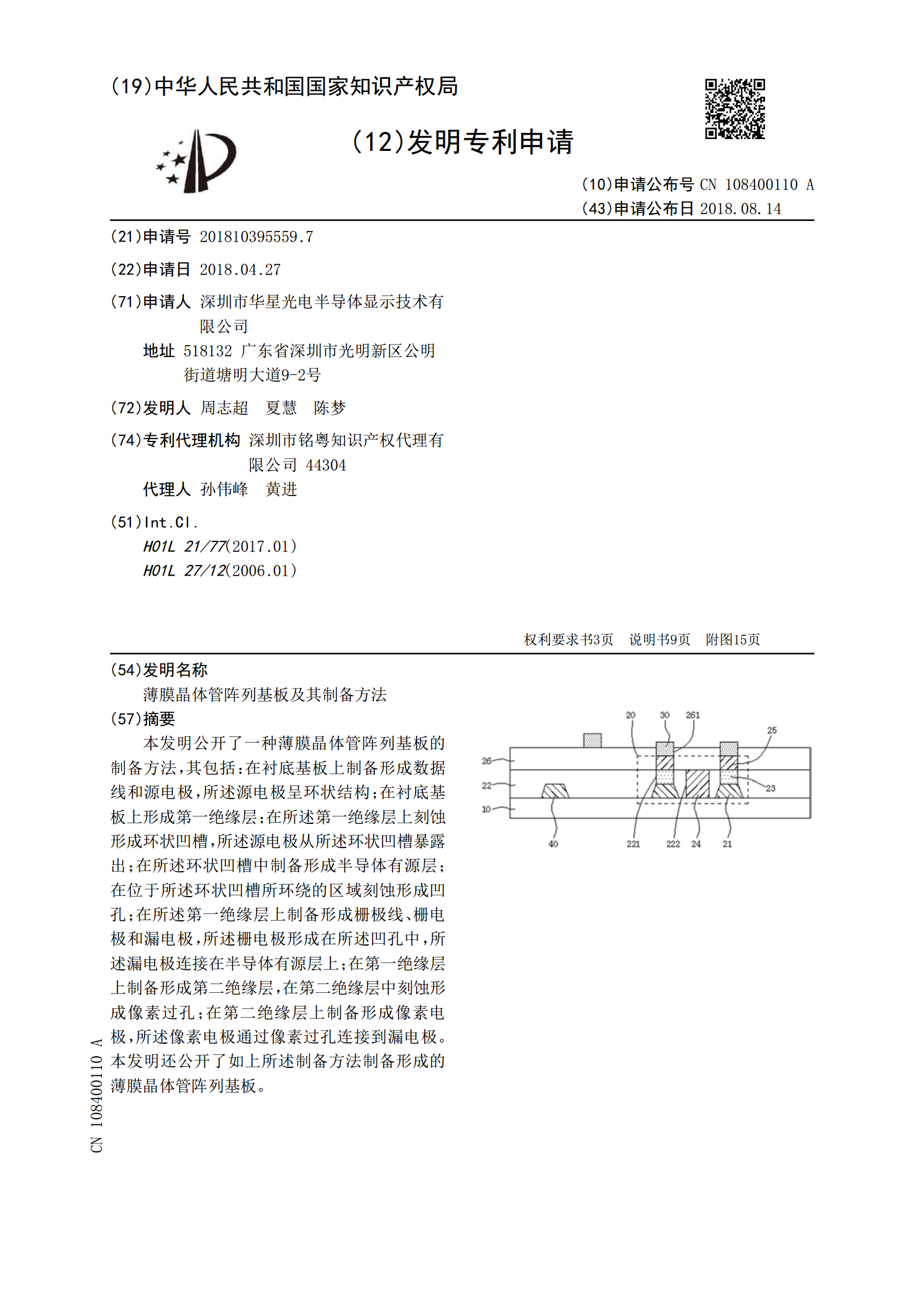

本发明公开了一种薄膜晶体管阵列基板的制备方法,其包括:在衬底基板上制备形成数据线和源电极,所述源电极呈环状结构;在衬底基板上形成第一绝缘层;在所述第一绝缘层上刻蚀形成环状凹槽,所述源电极从所述环状凹槽暴露出;在所述环状凹槽中制备形成半导体有源层;在位于所述环状凹槽所环绕的区域刻蚀形成凹孔;在所述第一绝缘层上制备形成栅极线、栅电极和漏电极,所述栅电极形成在所述凹孔中,所述漏电极连接在半导体有源层上;在第一绝缘层上制备形成第二绝缘层,在第二绝缘层中刻蚀形成像素过孔;在第二绝缘层上制备形成像素电极,所述像素电极

薄膜晶体管及其制备方法、阵列基板.pdf

本发明提供一种薄膜晶体管及其制备方法、阵列基板,属于薄膜晶体管制备技术领域,可解决至少部分现有薄膜晶体管制备工艺复杂或接触电阻大的问题。该薄膜晶体管制备方法包括:形成半导体层和光刻胶层;对光刻胶层进行阶梯曝光后显影,形成光刻胶层完全去除的第一区域,光刻胶层部分保留的第二区域,和光刻胶层完全保留的第三区域;除去第一区域的半导体层,形成包括有源区的图形;减薄光刻胶层,将第二区域的光刻胶层完全除去,而第三区域保留部分光刻胶层;使第二区域的有源区导体化,形成欧姆接触层;剥离第三区域的光刻胶层;通过构图工艺至少在第

薄膜晶体管阵列基板及其制备方法.pdf

本发明提供一种薄膜晶体管阵列基板及其制备方法,方法包括:提供衬底基板,在衬底基板上依次形成栅极、栅极绝缘层、有源层、欧姆接触层、源/漏极及绝缘层;在绝缘层上涂布光阻层;对光阻层进行曝光,使光阻层图案化,在欲形成像素电极的对应位置暴露绝缘层,并且形成分布在暴露的绝缘层周缘的第一光阻区域及分布在第一光阻区域外围的第二光阻区域,第一光阻区域光阻层的厚度小于第二光阻区域光阻层的厚度;通过蚀刻制程移除暴露的绝缘层,形成过孔,暴露出漏极,第一光阻区域对应过孔上方边缘;对光阻层进行灰化处理,去除第一光阻区域,暴露出过孔

薄膜晶体管及其制备方法、阵列基板.pdf

本发明提供一种薄膜晶体管及其制备方法、阵列基板,属于显示技术领域。本发明的薄膜晶体管包括栅极、源极、漏极和多个绝缘层,其中至少一个绝缘层包括ⅤB族金属的氧化物。采用ⅤB族金属的氧化物形成绝缘层,由于ⅤB族金属的氧化物的介电常数较高,从而可降低绝缘层的厚度,有利于薄膜晶体管的小型化。

薄膜晶体管及其制备方法和阵列基板.pdf

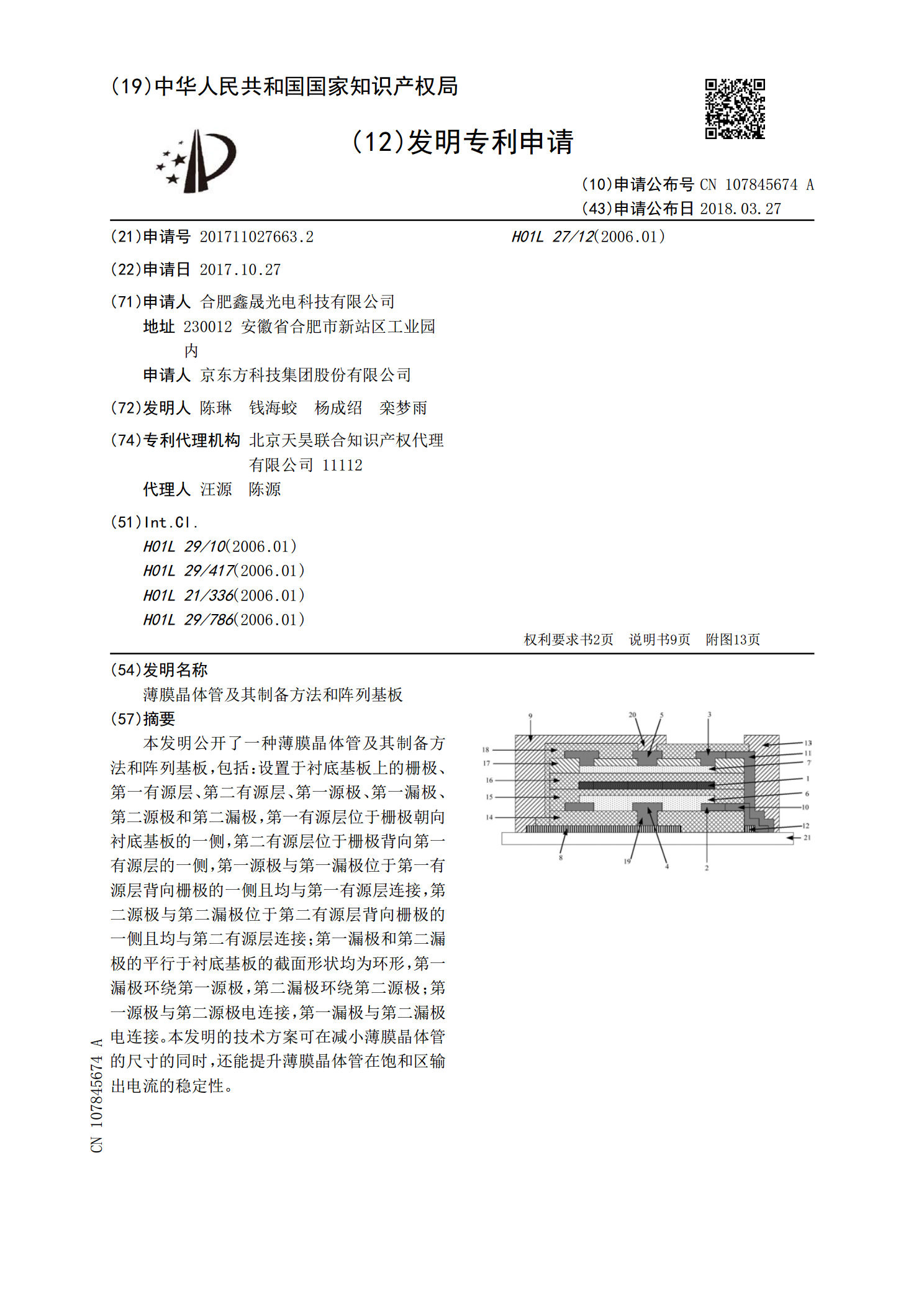

本发明公开了一种薄膜晶体管及其制备方法和阵列基板,包括:设置于衬底基板上的栅极、第一有源层、第二有源层、第一源极、第一漏极、第二源极和第二漏极,第一有源层位于栅极朝向衬底基板的一侧,第二有源层位于栅极背向第一有源层的一侧,第一源极与第一漏极位于第一有源层背向栅极的一侧且均与第一有源层连接,第二源极与第二漏极位于第二有源层背向栅极的一侧且均与第二有源层连接;第一漏极和第二漏极的平行于衬底基板的截面形状均为环形,第一漏极环绕第一源极,第二漏极环绕第二源极;第一源极与第二源极电连接,第一漏极与第二漏极电连接。本