一种放大器输入失调电压的自动校正电路及校正方法.pdf

宁馨****找我

亲,该文档总共32页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种放大器输入失调电压的自动校正电路及校正方法.pdf

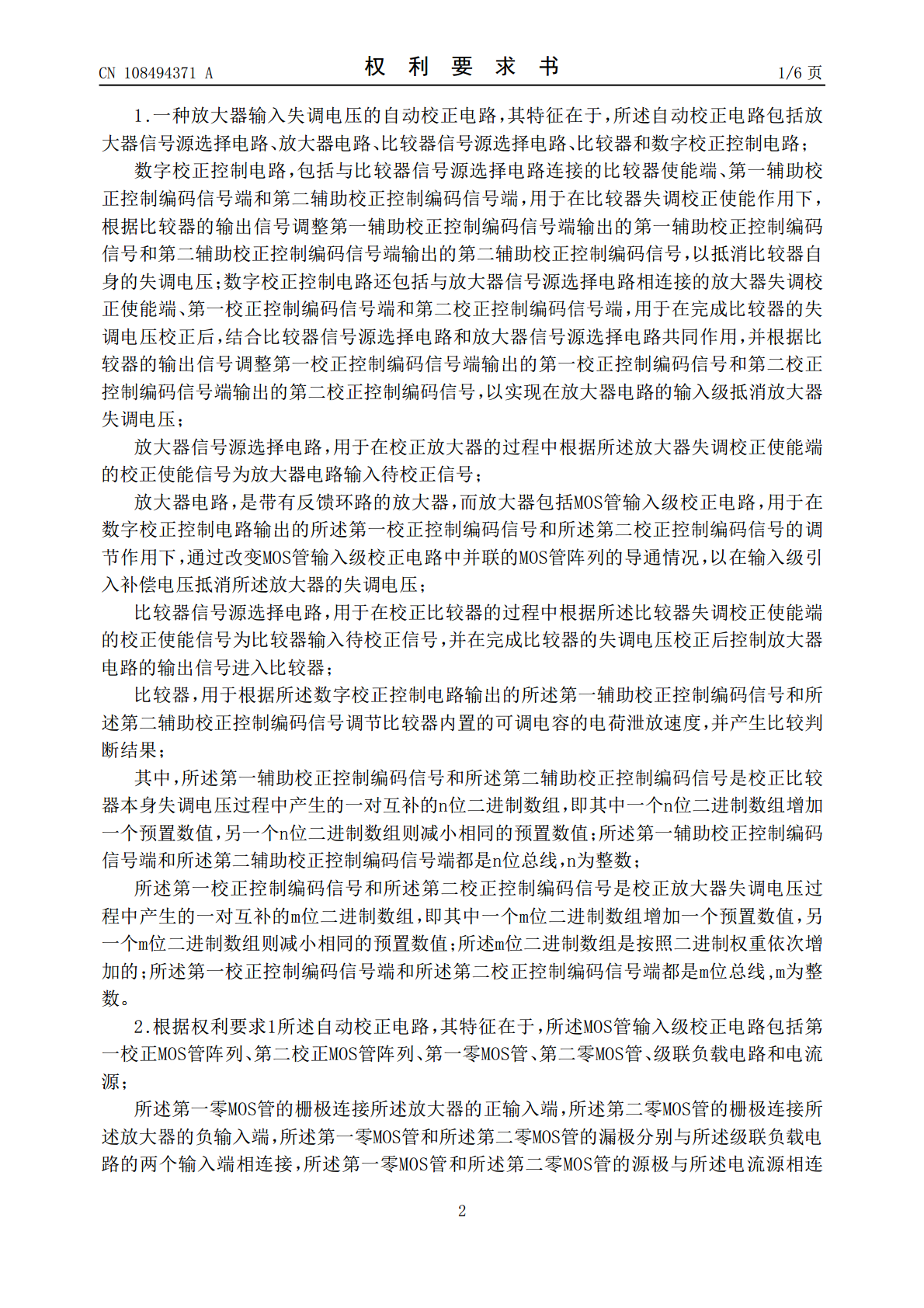

本发明公开一种放大器输入失调电压的自动校正电路及其校正方法,所述自动校正电路先通过比较器自身失调电压校正来完成辅助校正,再对放大器内部的MOS管输入级校正电路中MOS管的宽长比进行调整,从而实现整个放大器的输入失调电压的校正,相对于现有技术,本发明对放大器的差分输入级进行修改,使得输入差分MOS管对的等效宽长比可以由数字控制码值所控制,而不是通过补偿放大器的输出电压数值方式来纠正放大器的输入级的失调电压,也不需要一个不断调整的模拟电压就完成对全差分放大器失调电压的校正,当校正结束后可保留所获得的相应数字控

一种安检机自动校正体模及其校正方法.pdf

本发明公开了安检机自动校正体模及其校正方法,安检机自动校正体模包括:体模本体;定位件,定位件至少为两个,且两个定位件分别设置于体模本体对角的两个转角处;定向件,定向件包括本体部以及延伸部;定位件与定向件均采用重金属制成。校正方法包括:扫描得到像素值低于预设阈值的图像标记,并通过依次分别与第一标准模板、第二标准模板匹配确定自动校正体模的四个转角位置以及方向并触发安检机进行自动校正。本发明的安检机自动校正体模可被安检机扫描识别,并确定其四个转角方位与方向后自动触发安检机的校正程序,实现安检机的自动校正,无经验

误差校正自动校正.docx

误差校正---自动校正自动校正适用于控制点较多,误差校正精度要求较高的图形。自动误差校正的基本原理为:通过系统自动采集实际控制点和理论控制点的坐标值,在实际值和理论值之间建立一种对应关系,并计算出每个实际控制点的误差系数,从而可根据所得到的误差系数来校正每个实际控制点周围的点、线、面数据,最终达到校正整个点、线、面文件的目的。具体方法和操作步骤:1.实际控制点文件:在数据录入的开始,就采集这个文件。采集该文件可通过两种方法:A.将扫描光栅文件上所有格网线的交点用输入“十”字子图的方法保存为点文件(也可取名

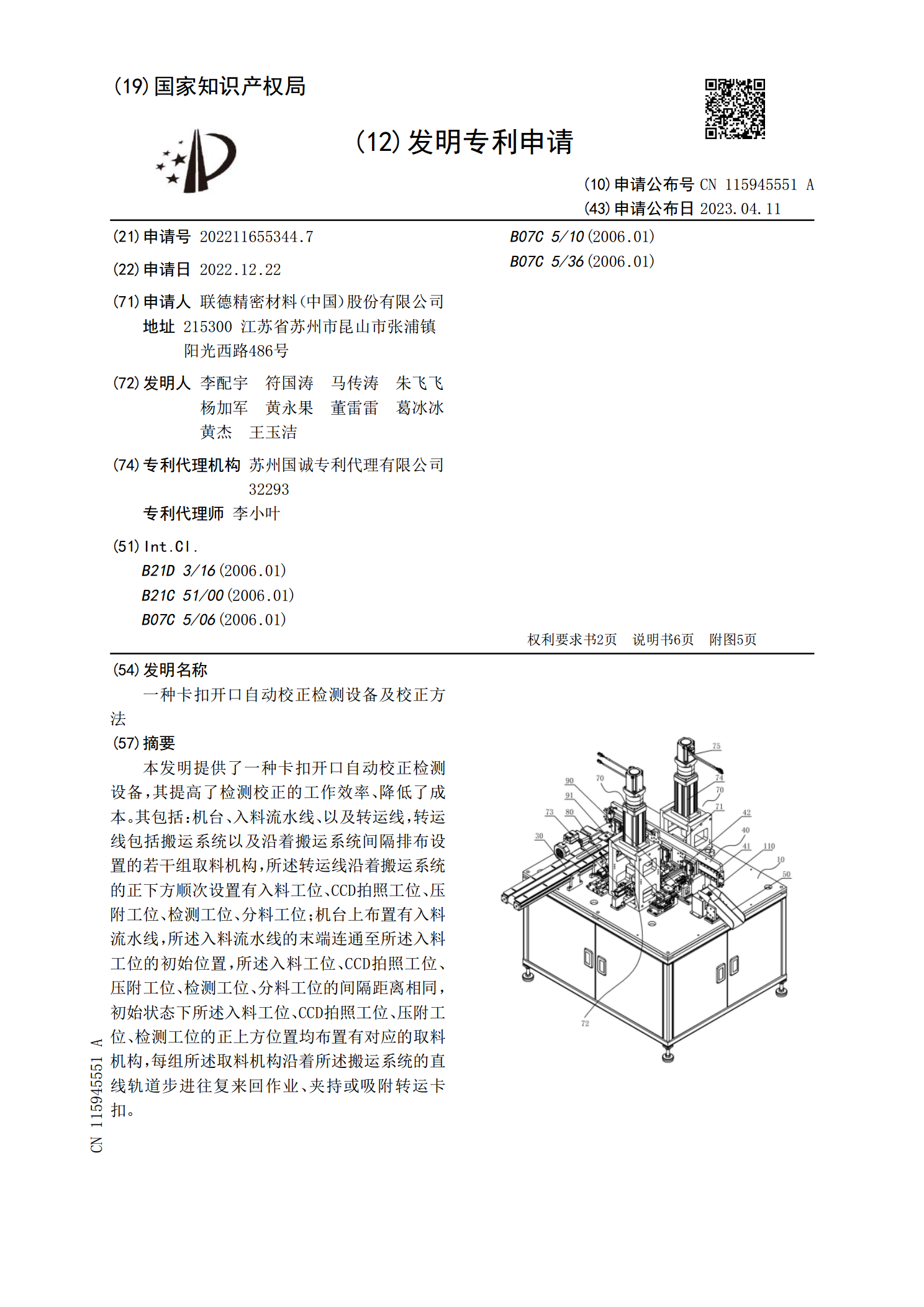

一种卡扣开口自动校正检测设备及校正方法.pdf

本发明提供了一种卡扣开口自动校正检测设备,其提高了检测校正的工作效率、降低了成本。其包括:机台、入料流水线、以及转运线,转运线包括搬运系统以及沿着搬运系统间隔排布设置的若干组取料机构,所述转运线沿着搬运系统的正下方顺次设置有入料工位、CCD拍照工位、压附工位、检测工位、分料工位;机台上布置有入料流水线,所述入料流水线的末端连通至所述入料工位的初始位置,所述入料工位、CCD拍照工位、压附工位、检测工位、分料工位的间隔距离相同,初始状态下所述入料工位、CCD拍照工位、压附工位、检测工位的正上方位置均布置有对应

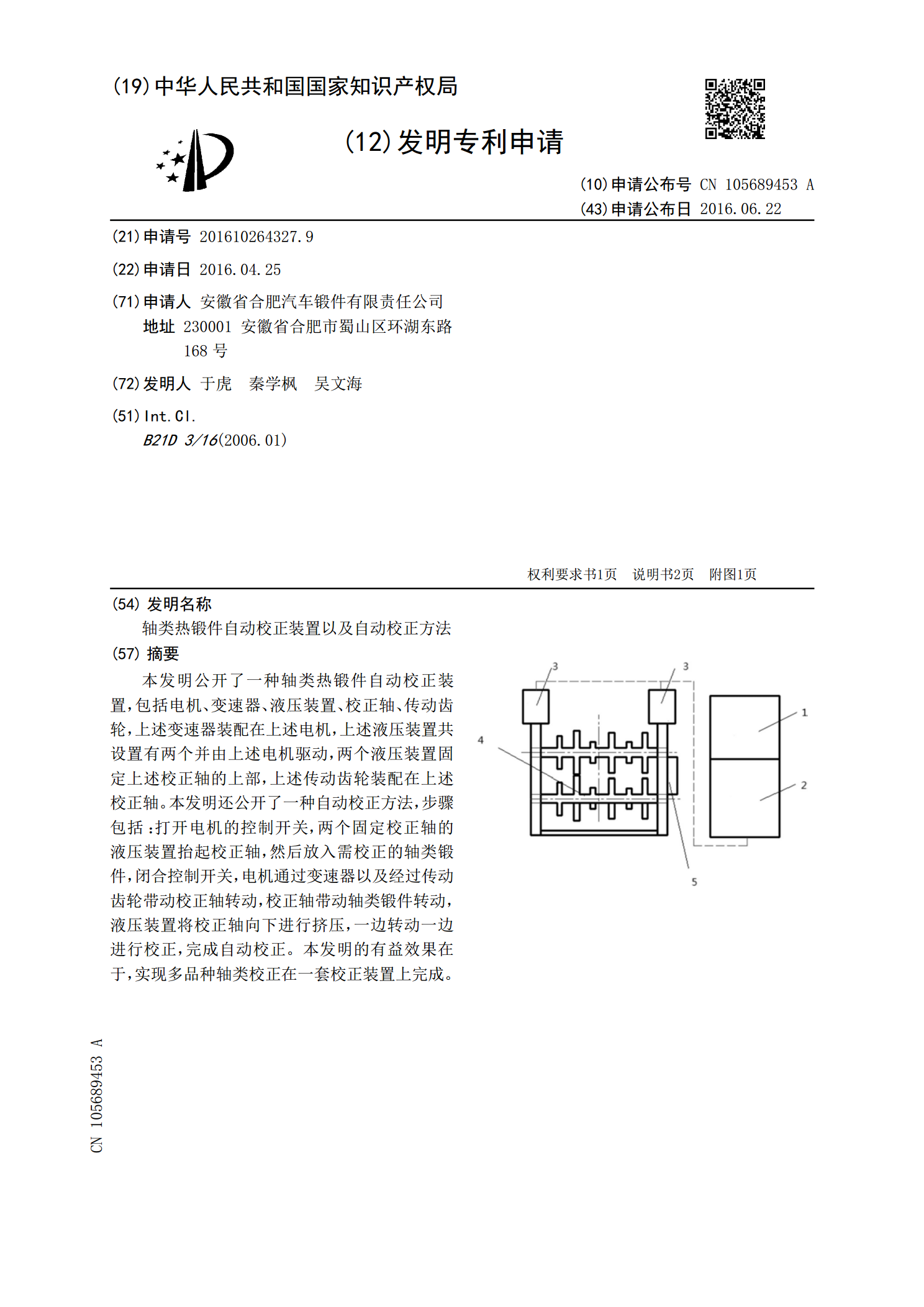

轴类热锻件自动校正装置以及自动校正方法.pdf

本发明公开了一种轴类热锻件自动校正装置,包括电机、变速器、液压装置、校正轴、传动齿轮,上述变速器装配在上述电机,上述液压装置共设置有两个并由上述电机驱动,两个液压装置固定上述校正轴的上部,上述传动齿轮装配在上述校正轴。本发明还公开了一种自动校正方法,步骤包括:打开电机的控制开关,两个固定校正轴的液压装置抬起校正轴,然后放入需校正的轴类锻件,闭合控制开关,电机通过变速器以及经过传动齿轮带动校正轴转动,校正轴带动轴类锻件转动,液压装置将校正轴向下进行挤压,一边转动一边进行校正,完成自动校正。本发明的有益效果在