3D NAND存储器件的制造方法及3D NAND存储器件.pdf

猫巷****熙柔

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

3D NAND存储器件的制造方法及3D NAND存储器件.pdf

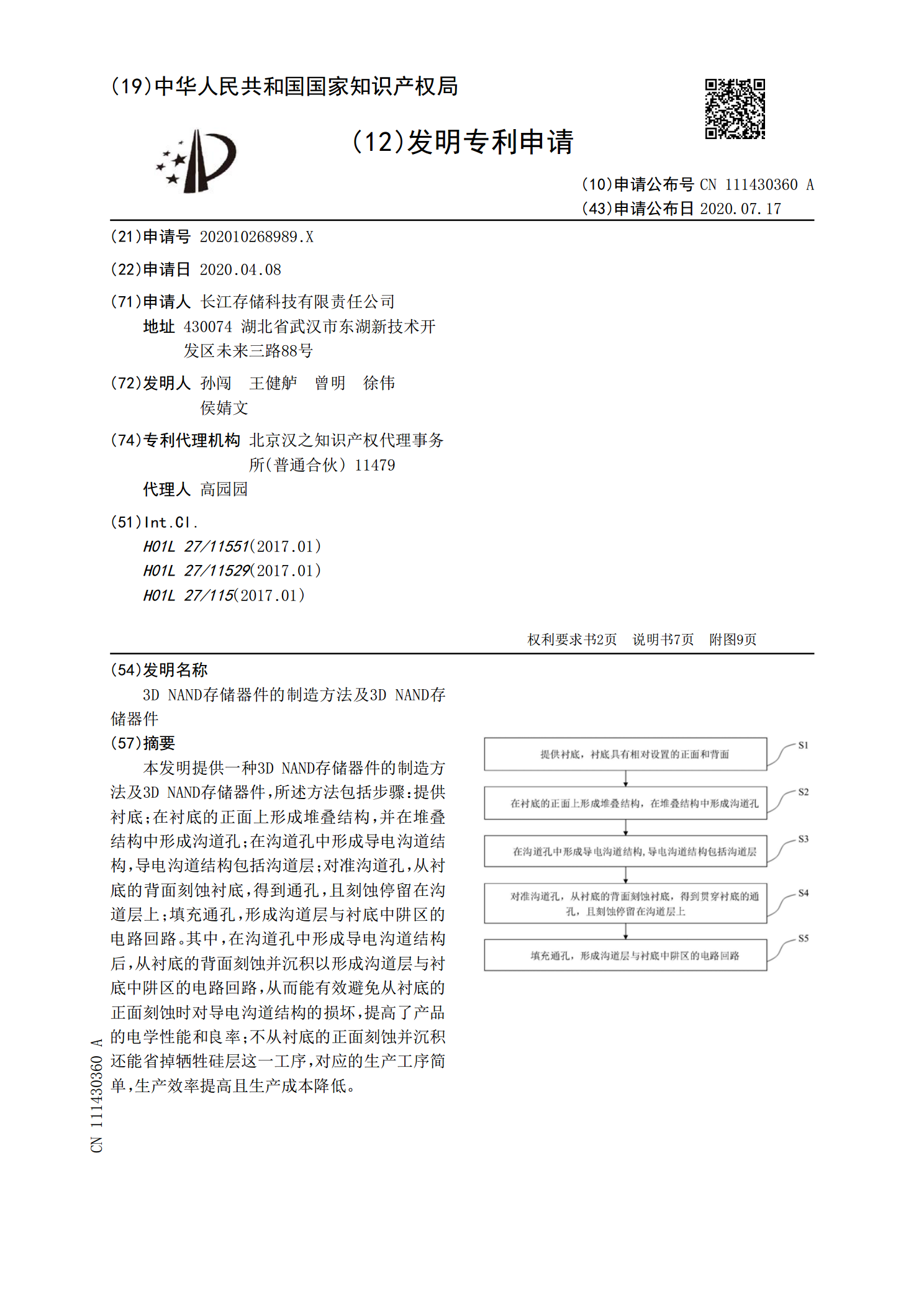

本发明提供一种3DNAND存储器件的制造方法及3DNAND存储器件,所述方法包括步骤:提供衬底;在衬底的正面上形成堆叠结构,并在堆叠结构中形成沟道孔;在沟道孔中形成导电沟道结构,导电沟道结构包括沟道层;对准沟道孔,从衬底的背面刻蚀衬底,得到通孔,且刻蚀停留在沟道层上;填充通孔,形成沟道层与衬底中阱区的电路回路。其中,在沟道孔中形成导电沟道结构后,从衬底的背面刻蚀并沉积以形成沟道层与衬底中阱区的电路回路,从而能有效避免从衬底的正面刻蚀时对导电沟道结构的损坏,提高了产品的电学性能和良率;不从衬底的正面刻蚀

一种3D NAND存储器件的制造方法.pdf

本发明提供一种3DNAND存储器件的制造方法,在堆叠层中形成存储单元串之后,在台阶区的介质层之上形成介质材料的隔离层,之后,利用贯通堆叠层的栅线缝隙,进行堆叠层中牺牲层的替换,在将牺牲层替换为栅极层后,进行栅线缝隙的填充以及平坦化工艺,在栅线缝隙中形成共源接触,且平坦化工艺以核心存储区的介质层为停止层。这样,在台阶区上额外形成介质材料的隔离层,隔离层将台阶区的介质层抬高,在形成共源接触时,即使在台阶区会存在导电材料的残留,在平坦化时,会将残留的接触材料一并去除,从而,避免台阶区导电材料的残留,提高器件良

存储单元及其制造方法、3D NAND存储器及其制造方法.pdf

本发明提供一种存储单元及其制造方法、3DNAND存储器及其制造方法,在堆叠结构中形成栅线缝隙,通过该栅线缝隙去除堆叠结构中的部分牺牲层,保留在第一方向上具有一定宽度的牺牲层,由这些保留的牺牲层及其对应的堆叠的绝缘层形成存储区块之间的隔离结构。保留的底部牺牲层,增加了对堆叠结构的支撑,增加了结构的稳定性,提高了后续产品的良率。本发明存储单元的存储块能够做得更小,增加了单位面积的存储容量。整个制程中,热过程减少,减少了衬底的翘曲,提高了成膜质量。基于上述存储单元形成3DNAND存储器时,存储单元衬底中阱区

一种3D存储器件的制造方法及3D存储器件.pdf

本申请公开了一种3D存储器件的制造方法及3D存储器件。该3D存储器件的制造方法包括:提供第一半导体结构,第一半导体结构包括衬底和叠层结构;在台阶区的表层设置引导层;对台阶区进行填补,使台阶区的表面与存储区平齐,并形成隔离沟槽;通过隔离沟槽对台阶区进行刻蚀,将引导层、牺牲层的边缘以及牺牲层中被引导层覆盖的区域去除;对刻蚀区域填充金属层,形成栅极导体层;设置导电通道,将各栅极导体层引出至叠层结构的表面;其中,引导层的刻蚀速率大于牺牲层的刻蚀速率。通过在牺牲层的台阶面上设置引导层,使得部分牺牲层得以作为支撑进行

3D存储器件及其制造方法.pdf

本申请公开了一种3D存储器件及其制造方法。该3D存储器件的制造方法包括:衬底;位于衬底上的栅叠层结构,栅叠层结构包括交替堆叠的多个栅极导体和多个层间绝缘层;贯穿栅叠层结构的多个沟道柱;以及贯穿栅叠层结构的多个假沟道柱,其中,假沟道柱的材料为介质材料。该3D存储器件采用介质材料形成假沟道柱,避免了假沟道柱底部漏电问题,提高了3D存储器件的良率和可靠性。