3D存储器件及其制造方法.pdf

书生****写意

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

3D存储器件及其制造方法.pdf

本申请公开了一种3D存储器件及其制造方法。该3D存储器件的制造方法包括:衬底;位于衬底上的栅叠层结构,栅叠层结构包括交替堆叠的多个栅极导体和多个层间绝缘层;贯穿栅叠层结构的多个沟道柱;以及贯穿栅叠层结构的多个假沟道柱,其中,假沟道柱的材料为介质材料。该3D存储器件采用介质材料形成假沟道柱,避免了假沟道柱底部漏电问题,提高了3D存储器件的良率和可靠性。

3D存储器件及其制造方法.pdf

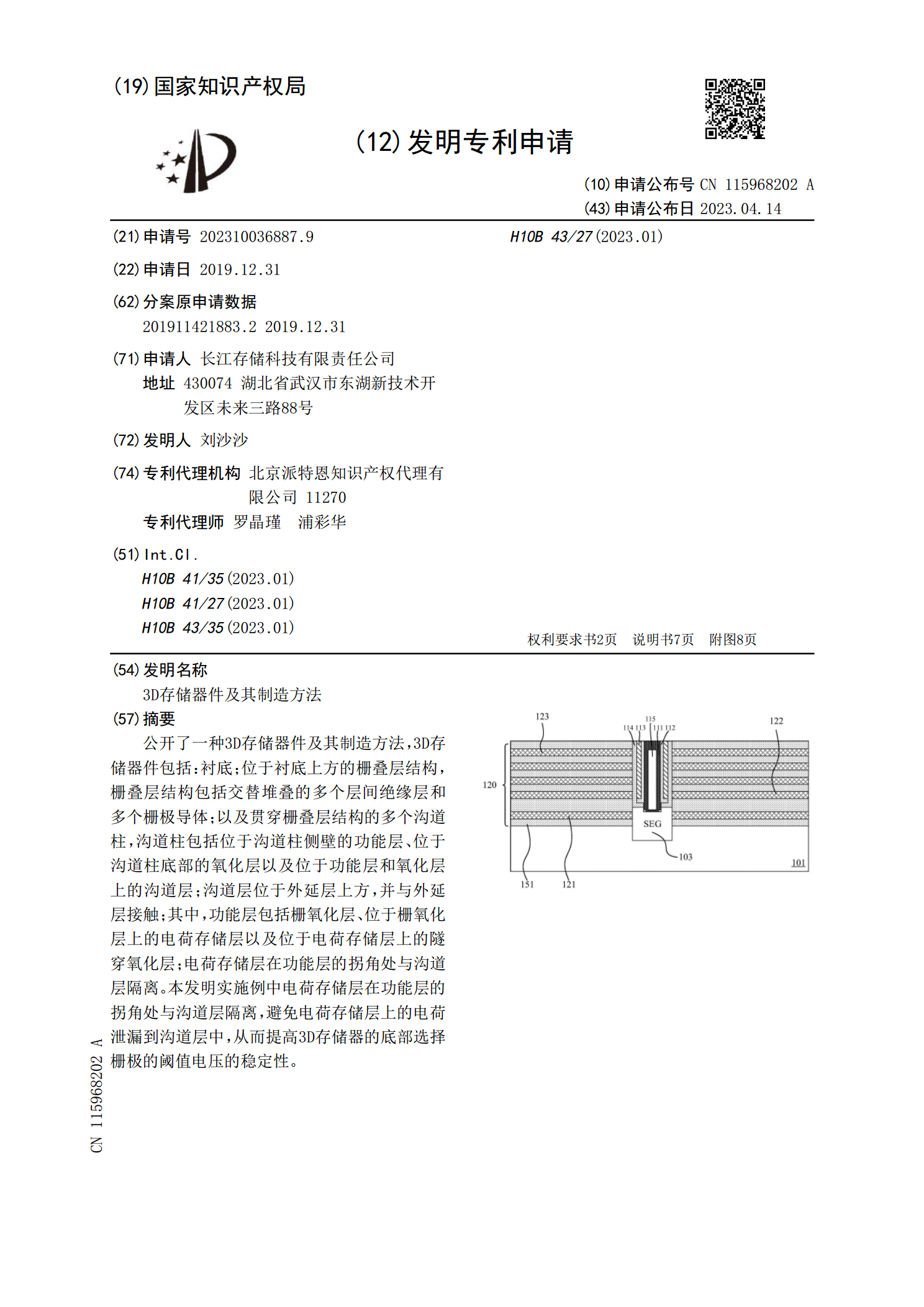

公开了一种3D存储器件及其制造方法,3D存储器件包括:衬底;位于衬底上方的栅叠层结构,栅叠层结构包括交替堆叠的多个层间绝缘层和多个栅极导体;以及贯穿栅叠层结构的多个沟道柱,沟道柱包括位于沟道柱侧壁的功能层、位于沟道柱底部的氧化层以及位于功能层和氧化层上的沟道层;沟道层位于外延层上方,并与外延层接触;其中,功能层包括栅氧化层、位于栅氧化层上的电荷存储层以及位于电荷存储层上的隧穿氧化层;电荷存储层在功能层的拐角处与沟道层隔离。本发明实施例中电荷存储层在功能层的拐角处与沟道层隔离,避免电荷存储层上的电荷泄漏到沟

3D存储器件及其制造方法.pdf

公开了一种3D存储器件,包括:衬底;位于所述衬底上的叠层结构,所述叠层结构包括交替堆叠的多个导体层和多个绝缘层;多个存储串,贯穿所述叠层结构;多个导电通道,贯穿所述叠层结构;其中,所述多个存储串呈蜂窝结构,每个所述导电通道位于所述蜂窝结构的中心并且用于通过所述衬底向其周围的所述多个存储串供电。本发明还提供一种本发明提供的3D存储器件的制造方法,利用共源极孔作为沉积通道以将叠层结构中的牺牲层替换成导体层,以及利用共源极孔形成共源极导电通道,避免栅叠层结构中的导体层与共源极导电通道之间形成空隙。

3D存储器件及其制造方法.pdf

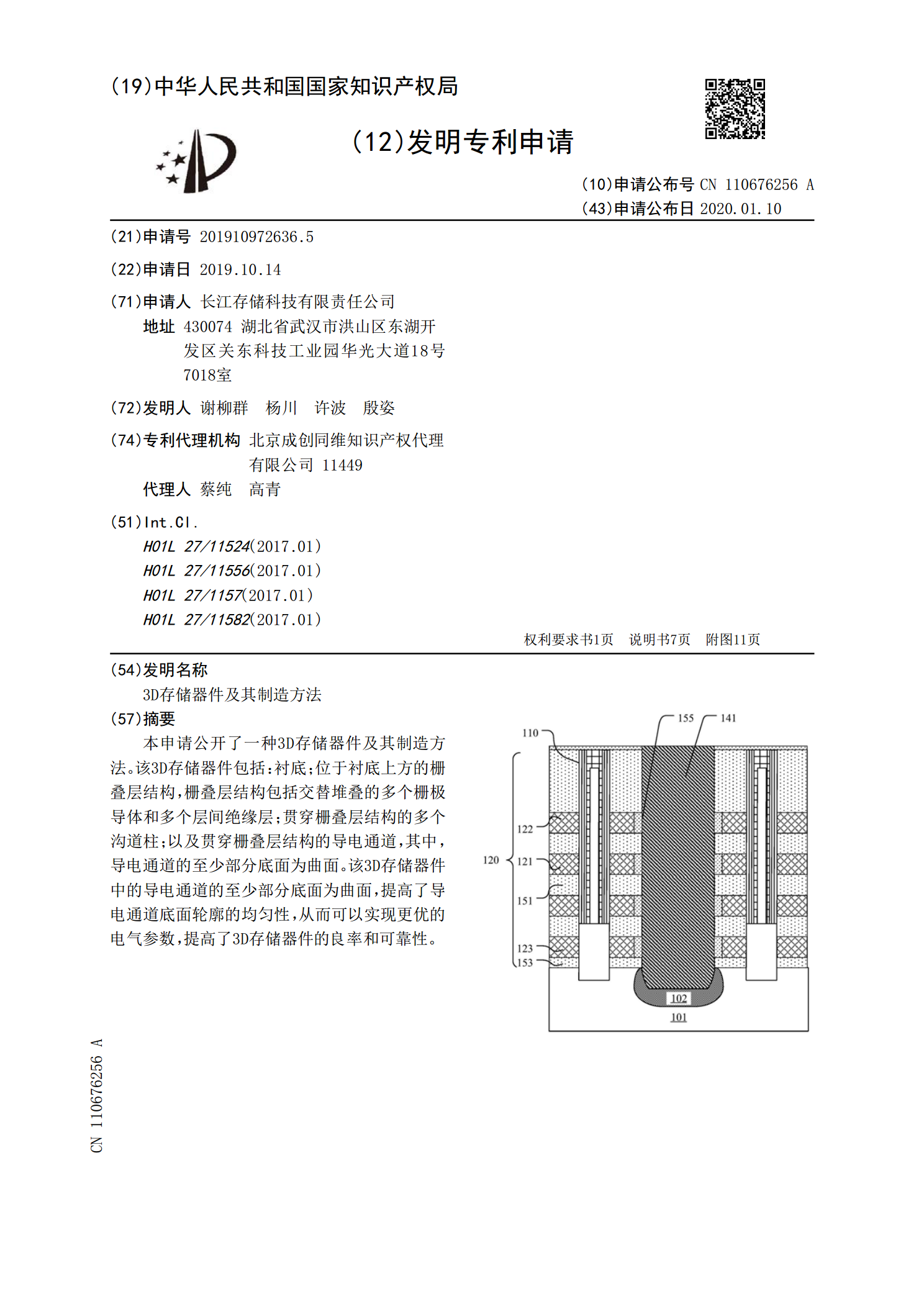

本申请公开了一种3D存储器件及其制造方法。该3D存储器件包括:衬底;位于衬底上方的栅叠层结构,栅叠层结构包括交替堆叠的多个栅极导体和多个层间绝缘层;贯穿栅叠层结构的多个沟道柱;以及贯穿栅叠层结构的导电通道,其中,导电通道的至少部分底面为曲面。该3D存储器件中的导电通道的至少部分底面为曲面,提高了导电通道底面轮廓的均匀性,从而可以实现更优的电气参数,提高了3D存储器件的良率和可靠性。

3D存储器件及其制造方法.pdf

本申请公开了一种3D存储器件及其制造方法。该3D存储器件包括:半导体衬底;栅叠层结构,位于半导体衬底上,包括交替堆叠的多个栅极导体层与多个层间绝缘层;多个沟道柱,贯穿栅叠层结构,并与半导体衬底接触;导电通道,贯穿栅叠层结构,并与半导体衬底接触;绝缘层,围绕导电通道,并将导电通道与多个栅极导体层彼此隔开;以及阻挡层,阻挡层位于栅极导体层与绝缘层之间,以将栅极导体层与绝缘层隔离。该3D存储器件采用阻挡层封闭栅极导体层的端部,从而可以避免残留的前驱气体破坏绝缘层导致栅极导体与导电通道短接。