一种降低封装芯片IO接口损伤的方法.pdf

王秋****哥哥

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种降低封装芯片IO接口损伤的方法.pdf

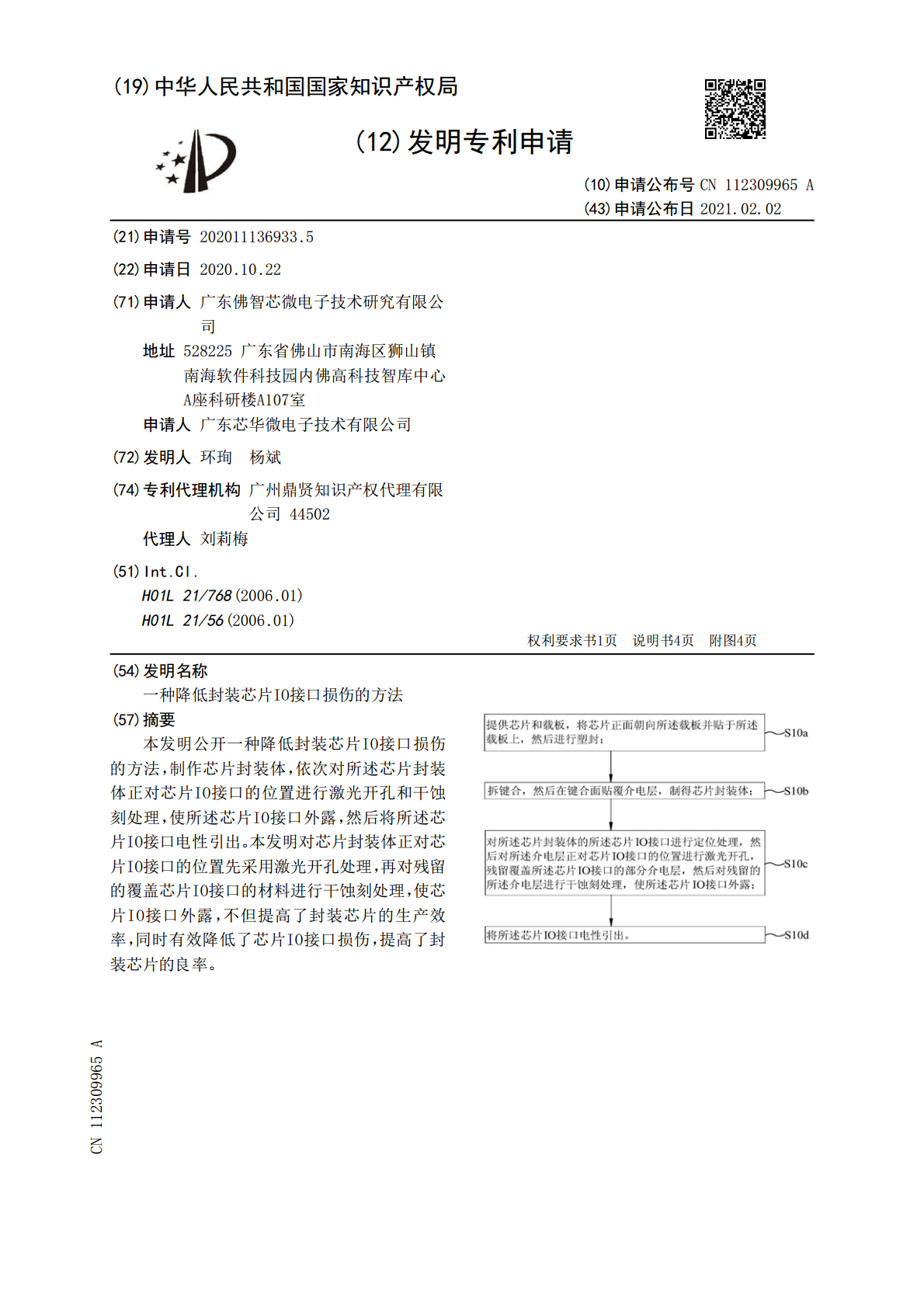

本发明公开一种降低封装芯片IO接口损伤的方法,制作芯片封装体,依次对所述芯片封装体正对芯片IO接口的位置进行激光开孔和干蚀刻处理,使所述芯片IO接口外露,然后将所述芯片IO接口电性引出。本发明对芯片封装体正对芯片IO接口的位置先采用激光开孔处理,再对残留的覆盖芯片IO接口的材料进行干蚀刻处理,使芯片IO接口外露,不但提高了封装芯片的生产效率,同时有效降低了芯片IO接口损伤,提高了封装芯片的良率。

常用IO接口芯片.pptx

第八章常用I/O接口芯片并行/O接口芯片82551、并行通信技术基础知识并行接口与并行通信并行接口旳特点并行接口电路8255A8255A旳内部构造和引脚1.外设数据端口2.与处理器接口1.写入方式控制字:控制字格式1.写入方式控制字:示例2.读写数据端口2.读写数据端口:示例端口C旳位控制字D7⑶有关控制字旳几点阐明按位置位/复位命令代码只能写入命令口。PA口、PB口也能够按位输出高/低电平,但是,这与前面旳按位置位/复位命令有本质旳区别,而且实现旳措施也不同。PC口按位输出是以命令旳形式送到控制寄存器存

一种芯片封装结构及芯片封装方法.pdf

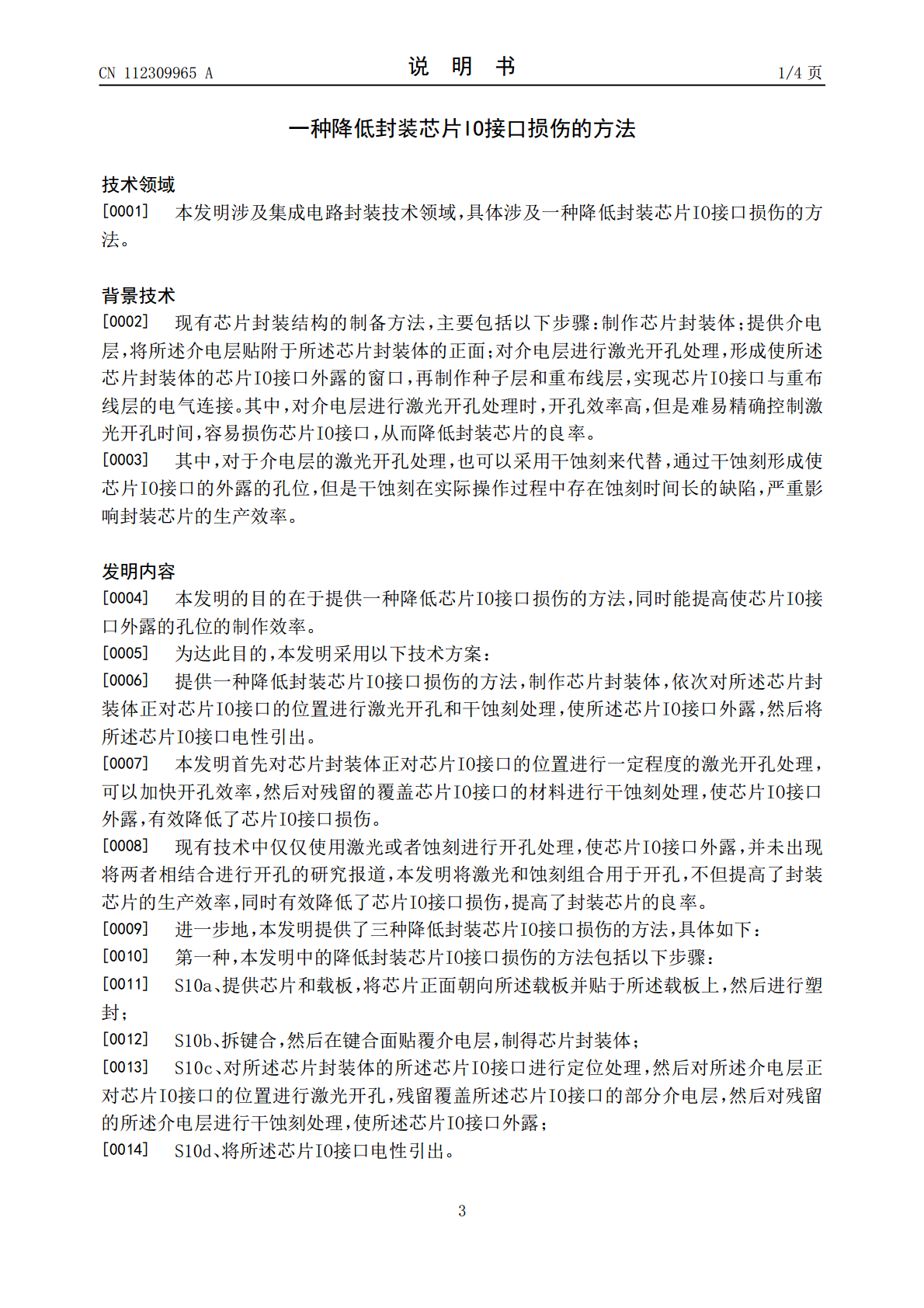

本发明提供一种芯片封装结构及芯片封装方法,芯片封装结构包括:芯片,芯片包括基板以及位于基板的一侧表面的第一管脚;电连接层,电连接层位于第一管脚的侧壁表面和底部表面;印刷线路板,印刷线路板包括层叠且间隔设置的第一电源层至第N电源层以及贯穿印刷线路板部分厚度的凹槽,N为大于1的整数,第一管脚适于延伸至凹槽中,电连接层与第p电源层至第q电源层连接,电源与第p电源层至第q电源层电学连接,p和q均为大于等于1且小于N的整数,且q大于或等于p。芯片封装结构能够适用于较高功率的芯片的封装,具有较高的结构稳定性,并具有优

一种芯片封装结构及芯片封装方法.pdf

本申请公开了一种芯片封装结构及芯片封装方法,该封装结构包括:至少两个焊盘组件,焊盘组件包括焊盘以及金属凸起;芯片,设置在其中一个焊盘组件的第一侧;金属增高层,设置在剩余焊盘组件的第一侧;第一封装层,至少包覆芯片以及金属增高层;导电组件,与芯片以及金属增高层连接。本申请中的封装结构一方面采用金属增高层增厚单侧焊盘的方式,可以降低盲孔内无金属的风险,提高钻孔后镀铜效果,可以提高产品的可靠性,另一方面通过设置包括焊盘和金属凸起的焊盘组件,可以降低蚀刻过度而露出芯片的风险,也可以提高产品的可靠性。

一种新型芯片封装方法及芯片封装结构.pdf

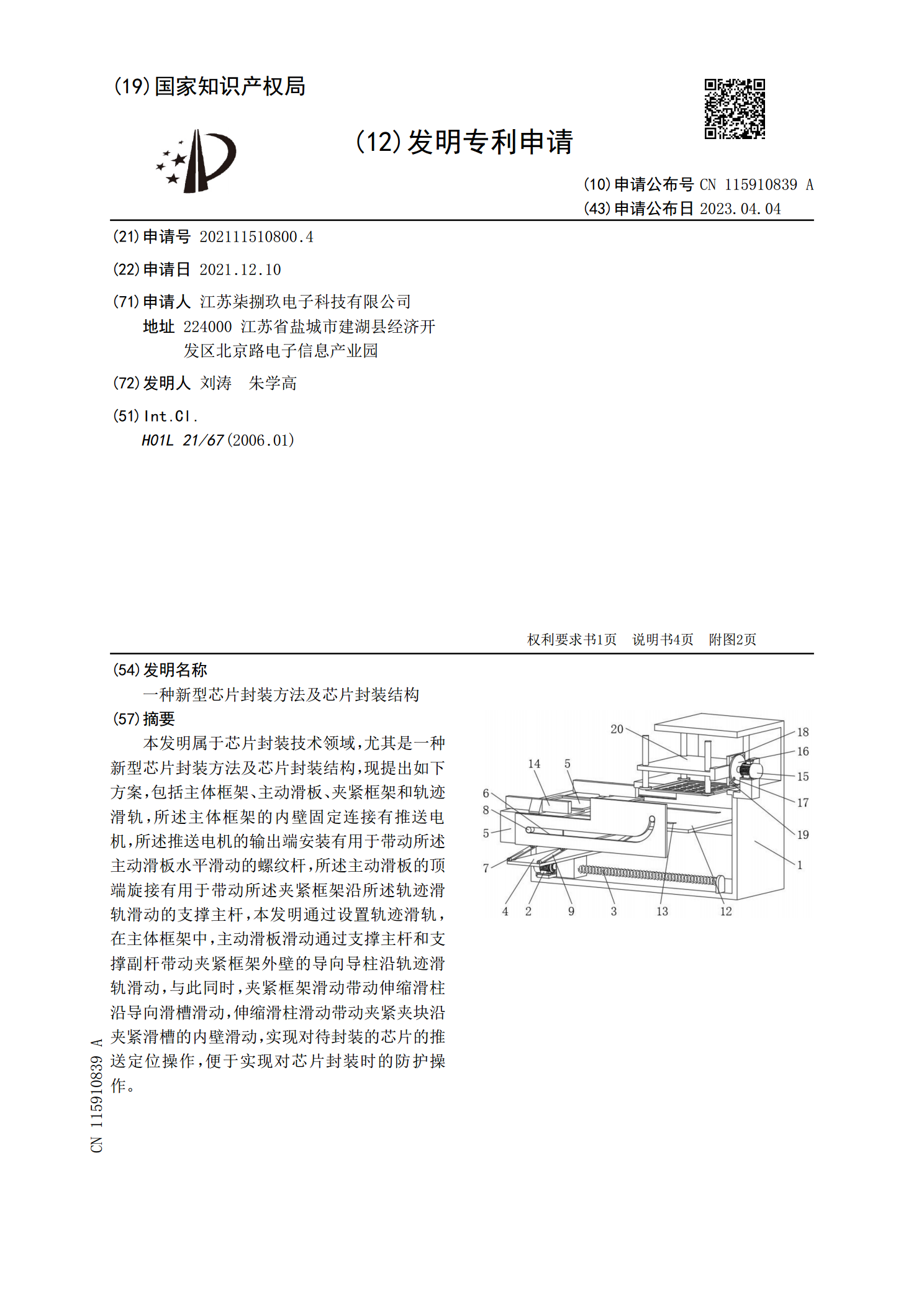

本发明属于芯片封装技术领域,尤其是一种新型芯片封装方法及芯片封装结构,现提出如下方案,包括主体框架、主动滑板、夹紧框架和轨迹滑轨,所述主体框架的内壁固定连接有推送电机,所述推送电机的输出端安装有用于带动所述主动滑板水平滑动的螺纹杆,所述主动滑板的顶端旋接有用于带动所述夹紧框架沿所述轨迹滑轨滑动的支撑主杆,本发明通过设置轨迹滑轨,在主体框架中,主动滑板滑动通过支撑主杆和支撑副杆带动夹紧框架外壁的导向导柱沿轨迹滑轨滑动,与此同时,夹紧框架滑动带动伸缩滑柱沿导向滑槽滑动,伸缩滑柱滑动带动夹紧夹块沿夹紧滑槽的内壁