功率半导体器件及其制作工艺.pdf

是你****松呀

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

功率半导体器件及其制作工艺.pdf

本申请涉及功率半导体器件技术领域,具体而言,涉及一种功率半导体器件及其制作工艺。功率半导体器件的制作工艺包括以下步骤:在衬底的正面沉积一层外延层并完成功率半导体器件正面结构的制作;对所述衬底的背面进行刻蚀,刻蚀穿整个衬底,直至外延层,形成引线孔;在所述引线孔里填充金属并在所述衬底背面垫积形成背面金属层,并退火合金,将所述外延层通过金属引线到背面金属层。本工艺不需对衬底进行减薄,而是采用引线孔技术,将背面电极引出。在不影响焊接工艺和功率半导体器件电性的基础上,取缔了减薄工艺,保留了衬底作为支撑,避免了减薄过

半导体功率器件的超结结构及其制作方法.pdf

一种半导体功率器件的超结结构包括N型衬底、形成于N型衬底上的N型外延、形成于N型外延表面的第一沟槽与第二沟槽、位于N型外延中的第一沟槽下方的第三沟槽、位于N型外延中的第四沟槽、位于第三沟槽与第四沟槽表面的P型掺杂区、位于第三、第四沟槽中且P型掺杂区表面及第一及第二沟槽侧壁的多晶硅、形成于N型外延上及第一及第二沟槽中的P型外延、形成于第一与第二沟槽之间的N型外延表面的N型外延层、形成于P型外延表面且邻近N型外延层两侧的第一、第二N型注入区、形成于N型外延层上的氧化硅与多晶硅层、形成于P型外延层、N型注入区与

半导体器件及其制作方法.pdf

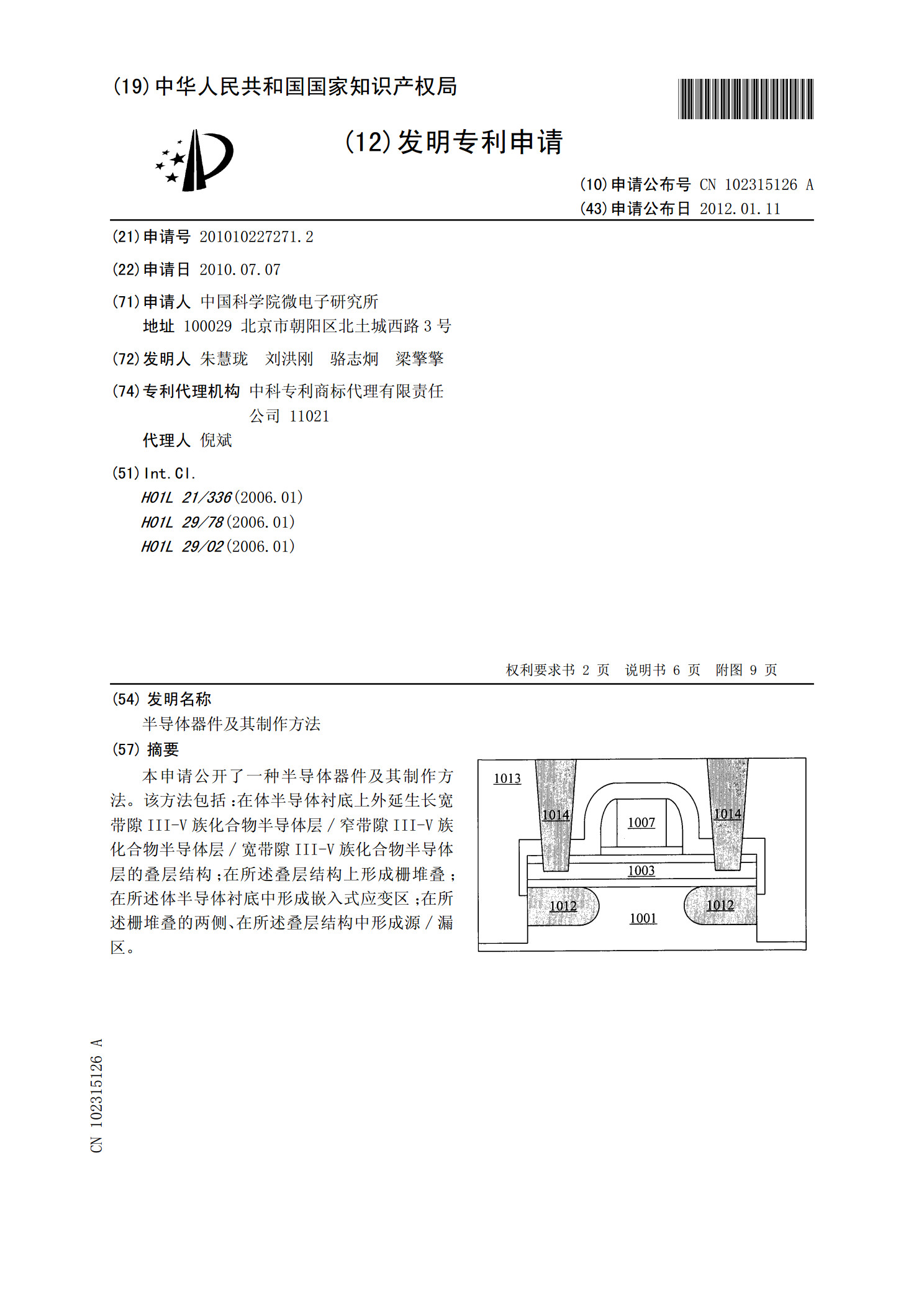

本申请公开了一种半导体器件及其制作方法。该方法包括:在体半导体衬底上外延生长宽带隙III-V族化合物半导体层/窄带隙III-V族化合物半导体层/宽带隙III-V族化合物半导体层的叠层结构;在所述叠层结构上形成栅堆叠;在所述体半导体衬底中形成嵌入式应变区;在所述栅堆叠的两侧、在所述叠层结构中形成源/漏区。

半导体器件及其制作方法.pdf

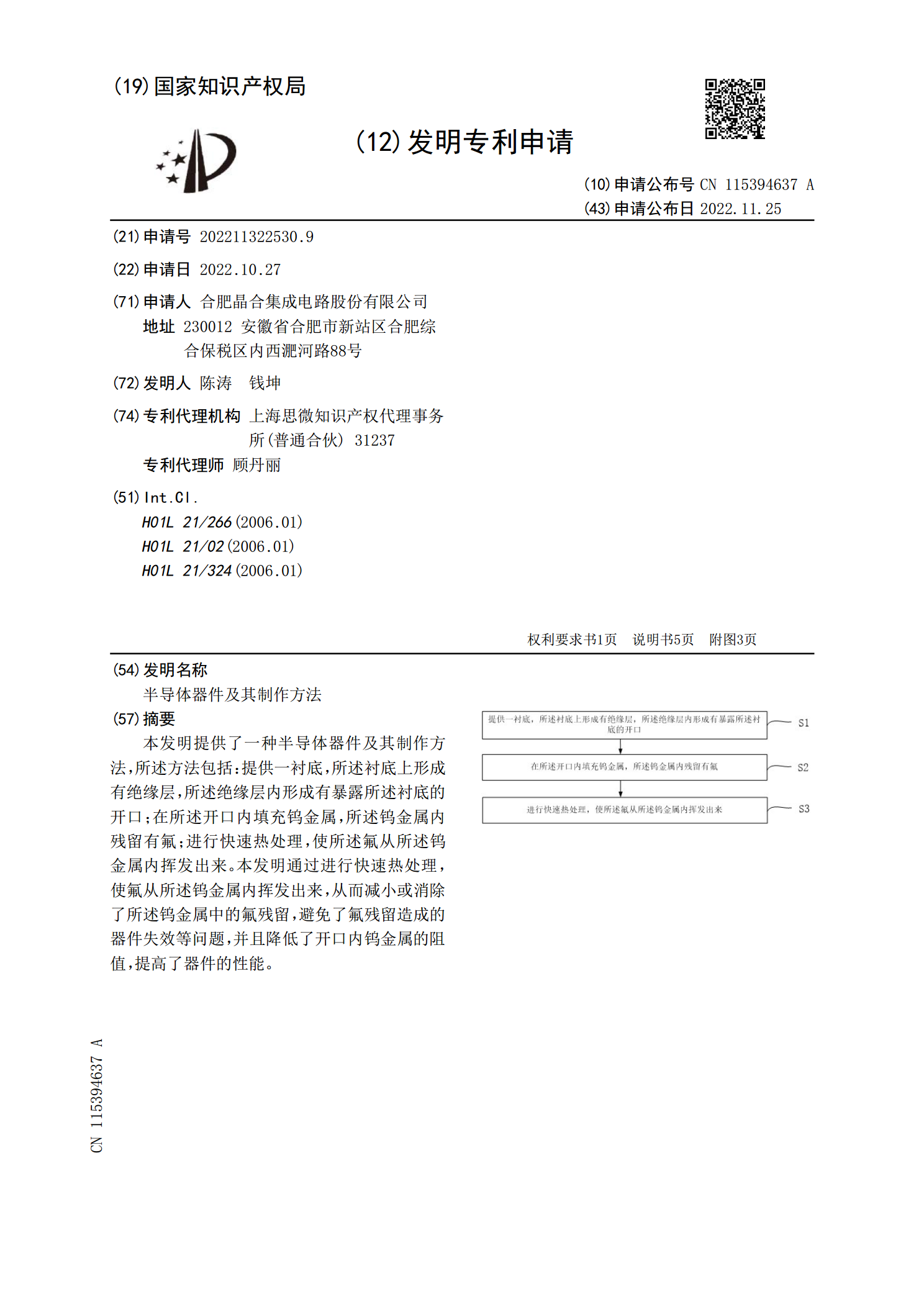

本发明提供了一种半导体器件及其制作方法,所述方法包括:提供一衬底,所述衬底上形成有绝缘层,所述绝缘层内形成有暴露所述衬底的开口;在所述开口内填充钨金属,所述钨金属内残留有氟;进行快速热处理,使所述氟从所述钨金属内挥发出来。本发明通过进行快速热处理,使氟从所述钨金属内挥发出来,从而减小或消除了所述钨金属中的氟残留,避免了氟残留造成的器件失效等问题,并且降低了开口内钨金属的阻值,提高了器件的性能。

半导体器件及其制作方法.pdf

本发明提供了一种半导体器件及其制作方法,所述方法包括:提供一衬底,所述衬底上形成有顶层金属层;在所述顶层金属层上形成钝化层,所述钝化层包含依次层叠的第一氧化物层、氮化物层与第二氧化物层。本发明通过将钝化层设置为氧化物、氮化物与氧化物三层层叠的结构来减小所述钝化层的应力,从而提高所述钝化层抵抗外界应力的能力,以避免所述顶层金属层变厚时在所述钝化层中产生裂纹,从而提高产品的可靠性。