芯片IO布局的方法及装置、SOC芯片.pdf

猫巷****正德

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

芯片IO布局的方法及装置、SOC芯片.pdf

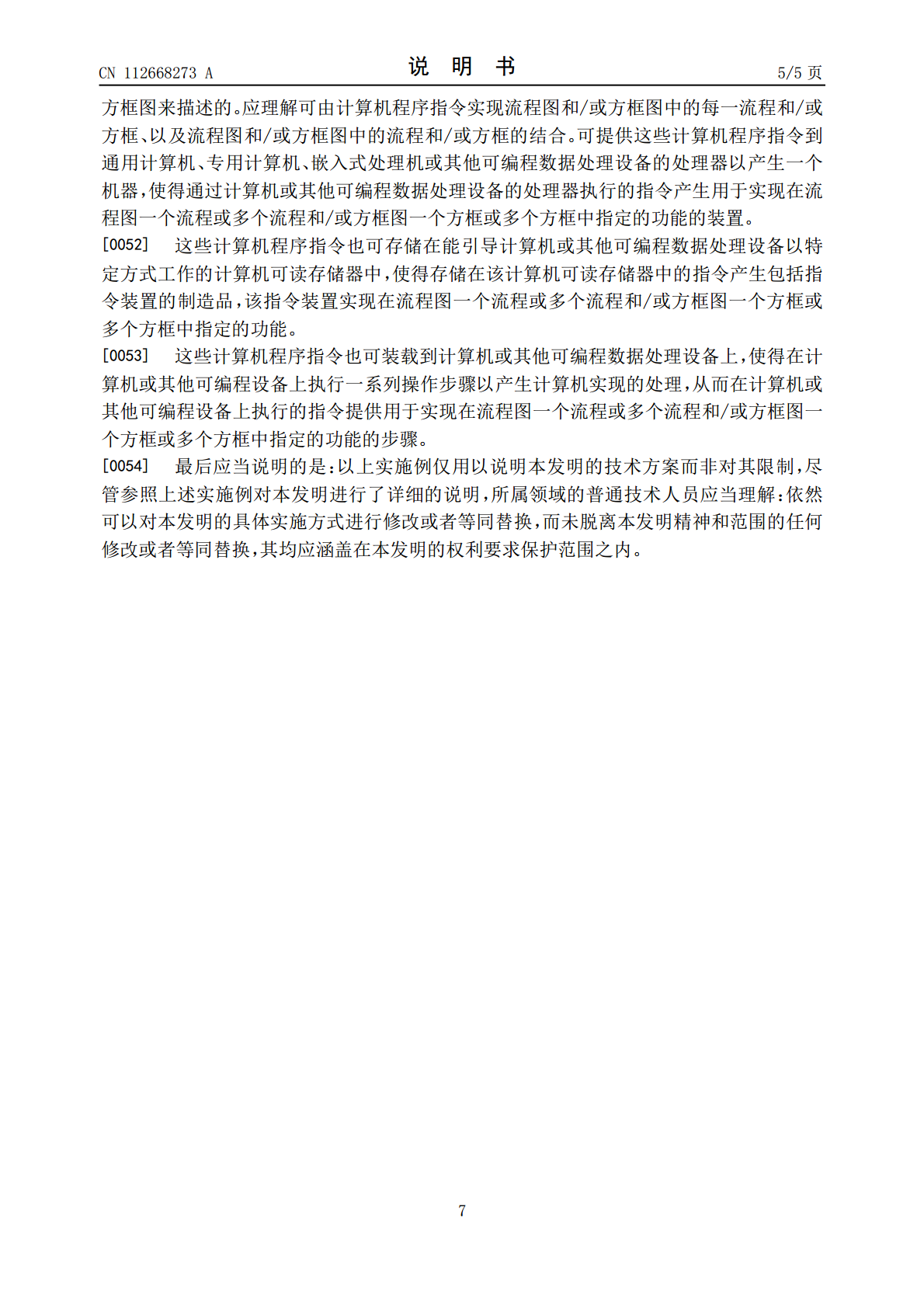

本发明涉及芯片设计技术领域,提供一种芯片IO布局的方法及装置、SOC芯片。所述方法包括:根据输入文件确定芯片的尺寸和用于放置所述芯片的IO引脚的预留位置;从所述输入文件获取所述IO引脚的目录,将所述IO引脚的目录导入脚本程序;通过执行所述脚本程序将所述IO引脚的图形按所述目录中的顺序布局到所述预留位置。本发明通过从输入文件获取芯片的IO引脚的目录将其导入脚本程序,通过执行脚本程序将IO引脚的图形按顺序布局到芯片的预留位置,可快速实现芯片IO的版图布局,无需手动对IO排序摆放,节约时间,提高IO版图布局的效

SoC芯片上以太网收发器的配置方法、装置、SoC芯片及车辆.pdf

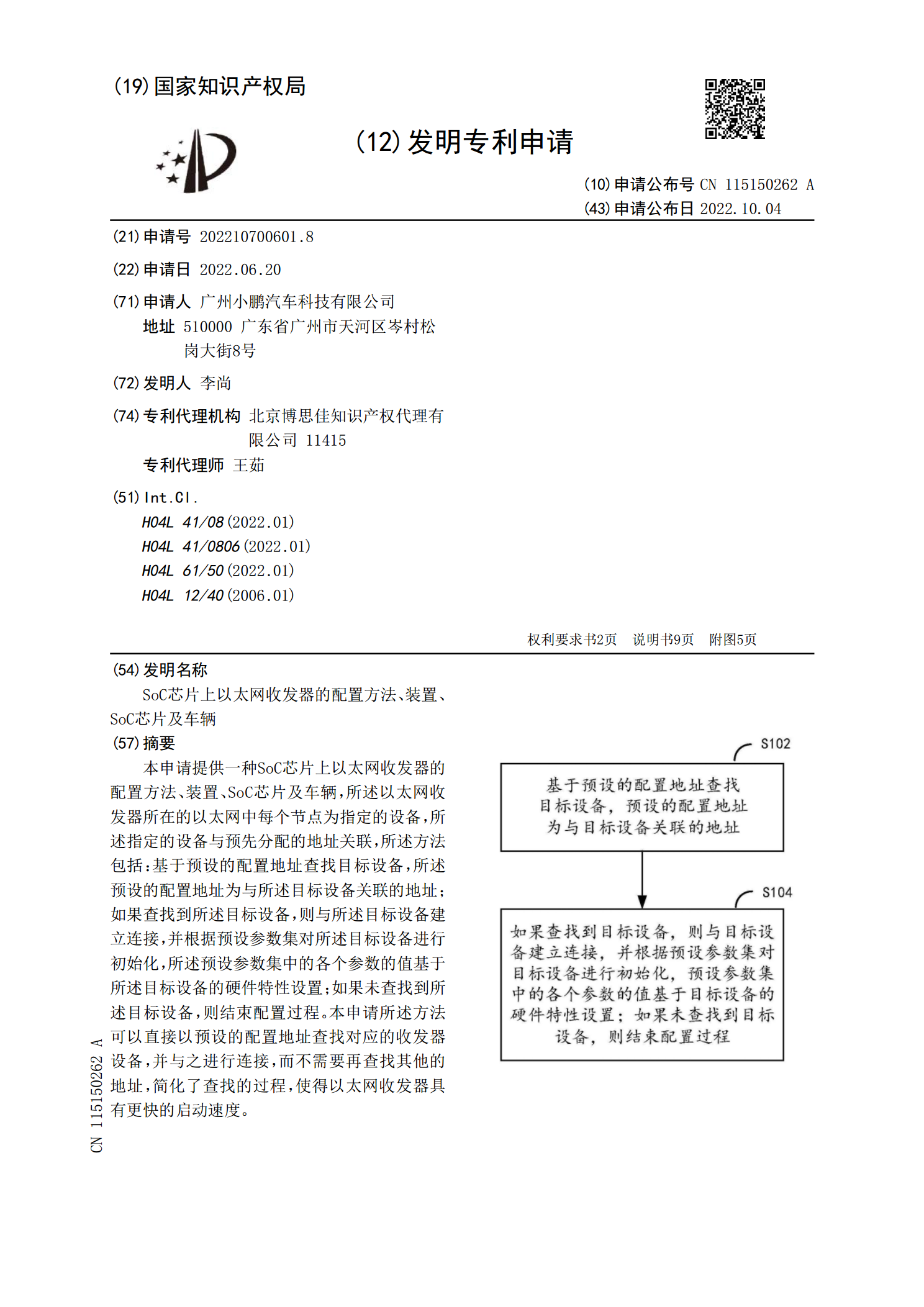

本申请提供一种SoC芯片上以太网收发器的配置方法、装置、SoC芯片及车辆,所述以太网收发器所在的以太网中每个节点为指定的设备,所述指定的设备与预先分配的地址关联,所述方法包括:基于预设的配置地址查找目标设备,所述预设的配置地址为与所述目标设备关联的地址;如果查找到所述目标设备,则与所述目标设备建立连接,并根据预设参数集对所述目标设备进行初始化,所述预设参数集中的各个参数的值基于所述目标设备的硬件特性设置;如果未查找到所述目标设备,则结束配置过程。本申请所述方法可以直接以预设的配置地址查找对应的收发器设备,

芯片布局方法.pdf

本发明公开了一种芯片布局方法,根据可编程逻辑器件芯片布线资源的分布规划建立顶层坐标系;对可编程逻辑器件芯片的所有资源进行分类,为每一类资源建立一个子坐标系;建立从子坐标系到顶层坐标系的映射;所有资源在子坐标系中的坐标为自变量,密度损失、线长损失、时序损失为目标函数,计算每个目标函数和自变量的关系和梯度,使用最优化求解得到合适的资源坐标;放置资源到相应的坐标。本发明通过以上技术方案,保证了可编程逻辑器件芯片资源布局的便利,方便全局布局阶段的建模,加速芯片资源的放置,提升软件性能。

AI SoC芯片及其启动方法.pdf

本发明提出的一种AISoC芯片及其启动方法,属于芯片领域。所述AISoC芯片包括:状态机,以及与所述状态机连接的目标模块;其中,所述状态机,用于接收目标信号,判断所述目标信号是否为第一目标信号,生成判断结果,并在所述判断结果为是时生成并发送第一响应信号至所述目标模块;所述目标模块,用于接收状态机发送的所述第一响应信号,并基于所述第一响应信号进行相应操作。本发明通过状态机判断接收到的信号是否为目标信号,当信号为目标信号时,发送相应信号至目标模块,使目标模块启动,实现了利用状态机提前配置关键IP或数据处理,以

芯片接合装置及芯片接合方法.pdf

本发明提供芯片接合装置及芯片接合方法,能够减少焊锡接合部中的空隙、界面的接合不良。在通过焊锡将半导体芯片接合在引线框架或衬底上的芯片接合机中,具有:输送部,其输送上述引线框架或衬底;焊锡供给部,其向上述引线框架或衬底上供给焊锡;搭载部,其将半导体芯片搭载、接合在上述引线框架或衬底上的焊锡上。所述芯片接合机还具有表面清洁化单元。将上述焊锡供给到上述引线框架或衬底上之后,所述表面清洁化单元除去在炉内熔融的焊锡表面的氧化膜。通过上述芯片接合设备,能够提高芯片接合品质。