氮化镓基垂直结构发光二极管及其制造方法.pdf

新月****姐a

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

氮化镓基垂直结构发光二极管及其制造方法.pdf

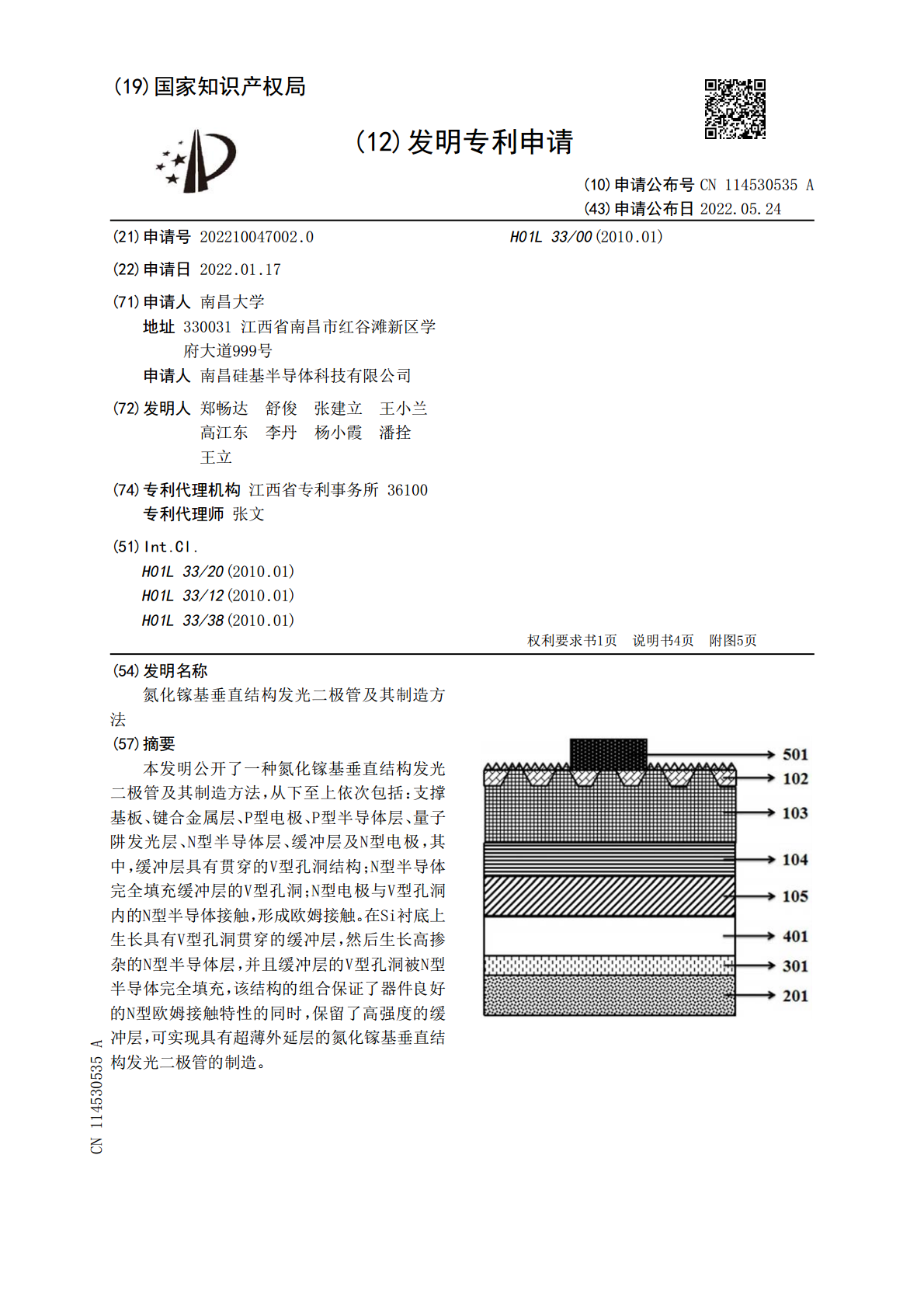

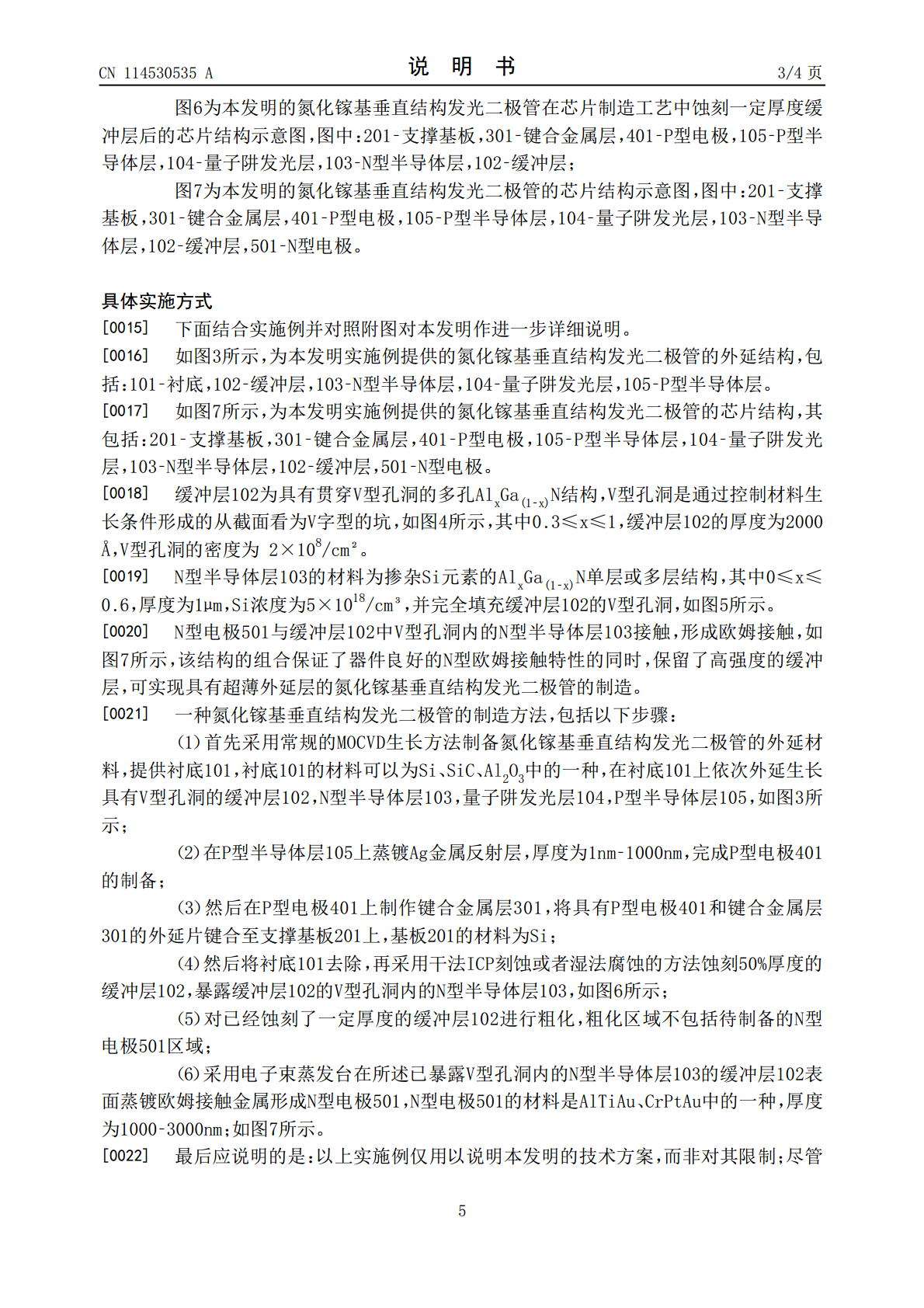

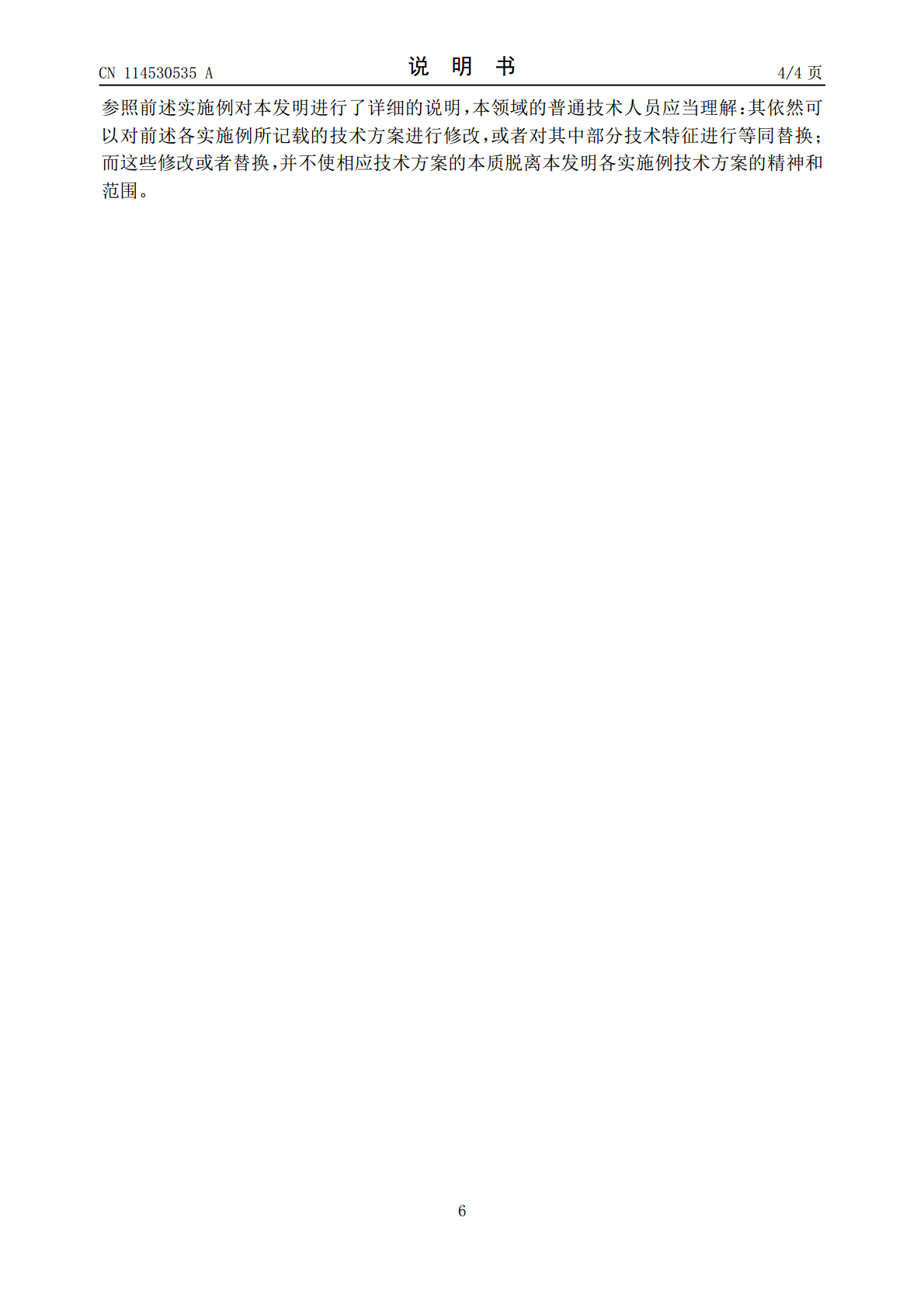

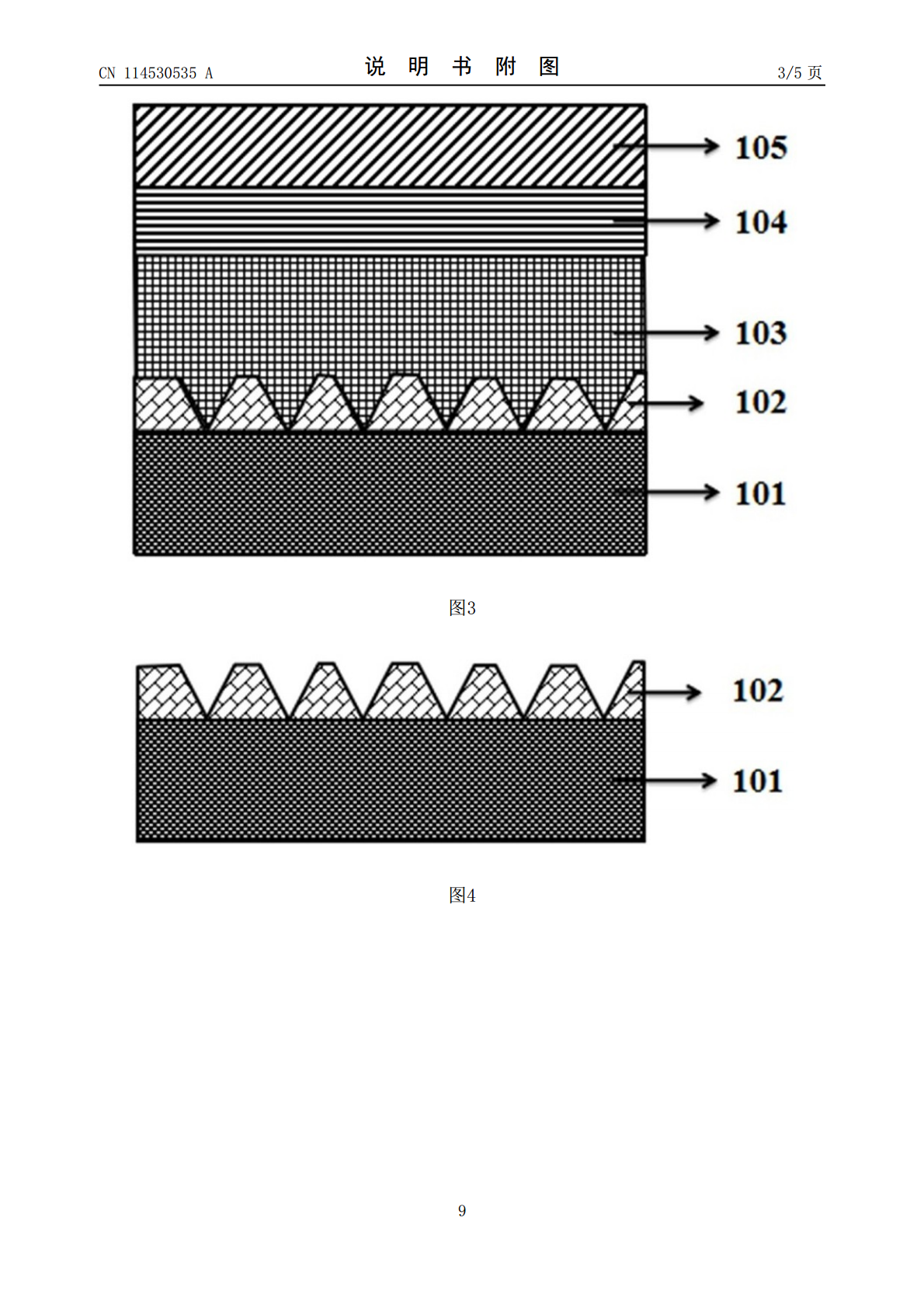

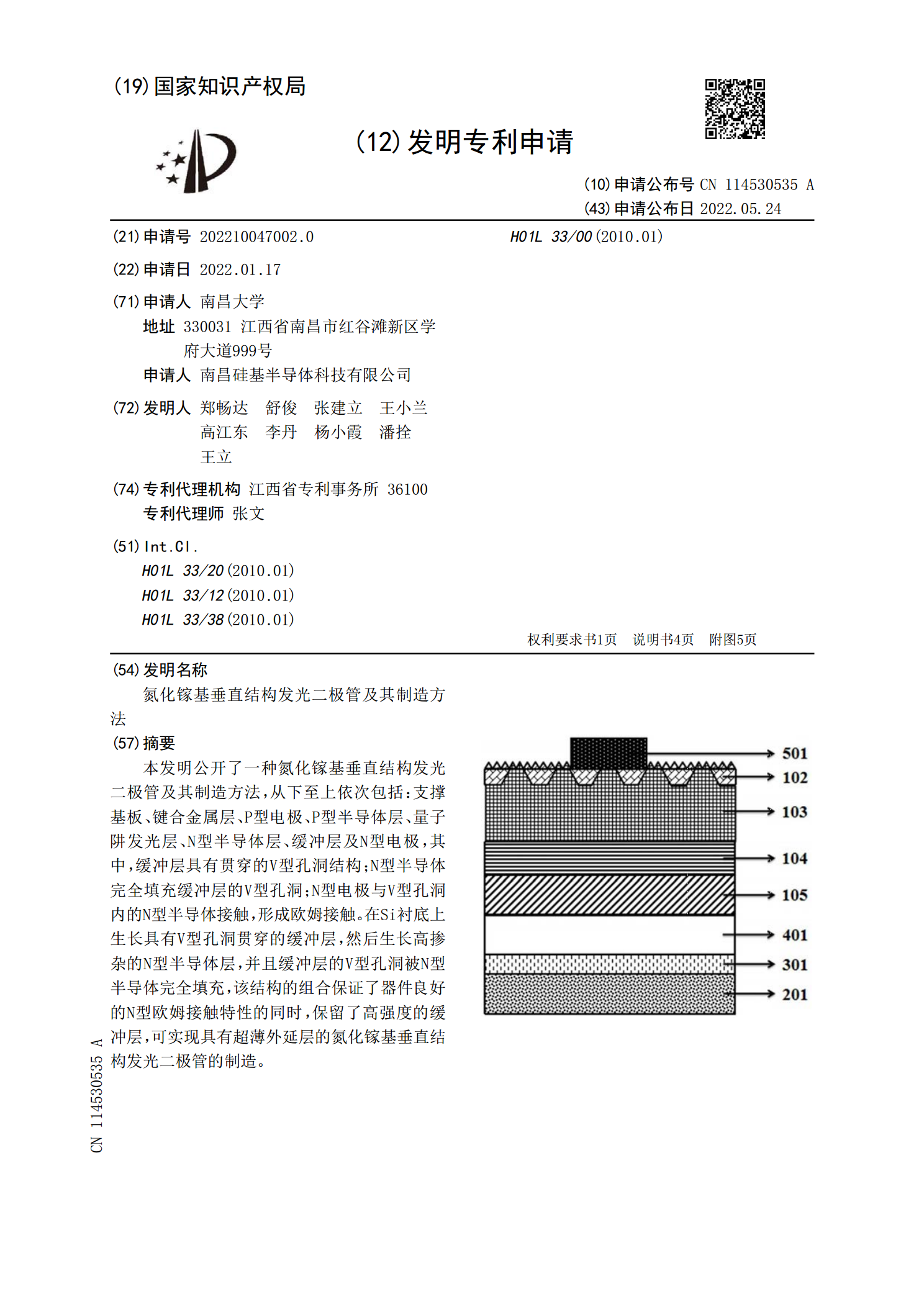

本发明公开了一种氮化镓基垂直结构发光二极管及其制造方法,从下至上依次包括:支撑基板、键合金属层、P型电极、P型半导体层、量子阱发光层、N型半导体层、缓冲层及N型电极,其中,缓冲层具有贯穿的V型孔洞结构;N型半导体完全填充缓冲层的V型孔洞;N型电极与V型孔洞内的N型半导体接触,形成欧姆接触。在Si衬底上生长具有V型孔洞贯穿的缓冲层,然后生长高掺杂的N型半导体层,并且缓冲层的V型孔洞被N型半导体完全填充,该结构的组合保证了器件良好的N型欧姆接触特性的同时,保留了高强度的缓冲层,可实现具有超薄外延层的氮化镓基垂

垂直氮化镓基发光二极管及其制造方法.pdf

本公开提供一种垂直GaN基半导体二极管及其制造方法。GaN基πi-V族半导体装置包括:基底;p型欧姆电极层,在基底上;p型GaN基πi-V族化合物半导体层,在p型欧姆电极层上;n型GaN基πi-V族化合物半导体层,在p型GaN基πi-V族化合物半导体层上;n型欧姆电极层,在n型GaN基IE-V族化合物半导体层上。p型欧姆电极层是具有70%或更高的高反射率的Ag基高反射电极,n型GaN基E-V族化合物半导体层的表面经受形成光子晶体的工艺和表面粗糙化的工艺中的至少一种工艺。

利用硅衬底制备垂直结构氮化镓基发光二极管器件的方法.pdf

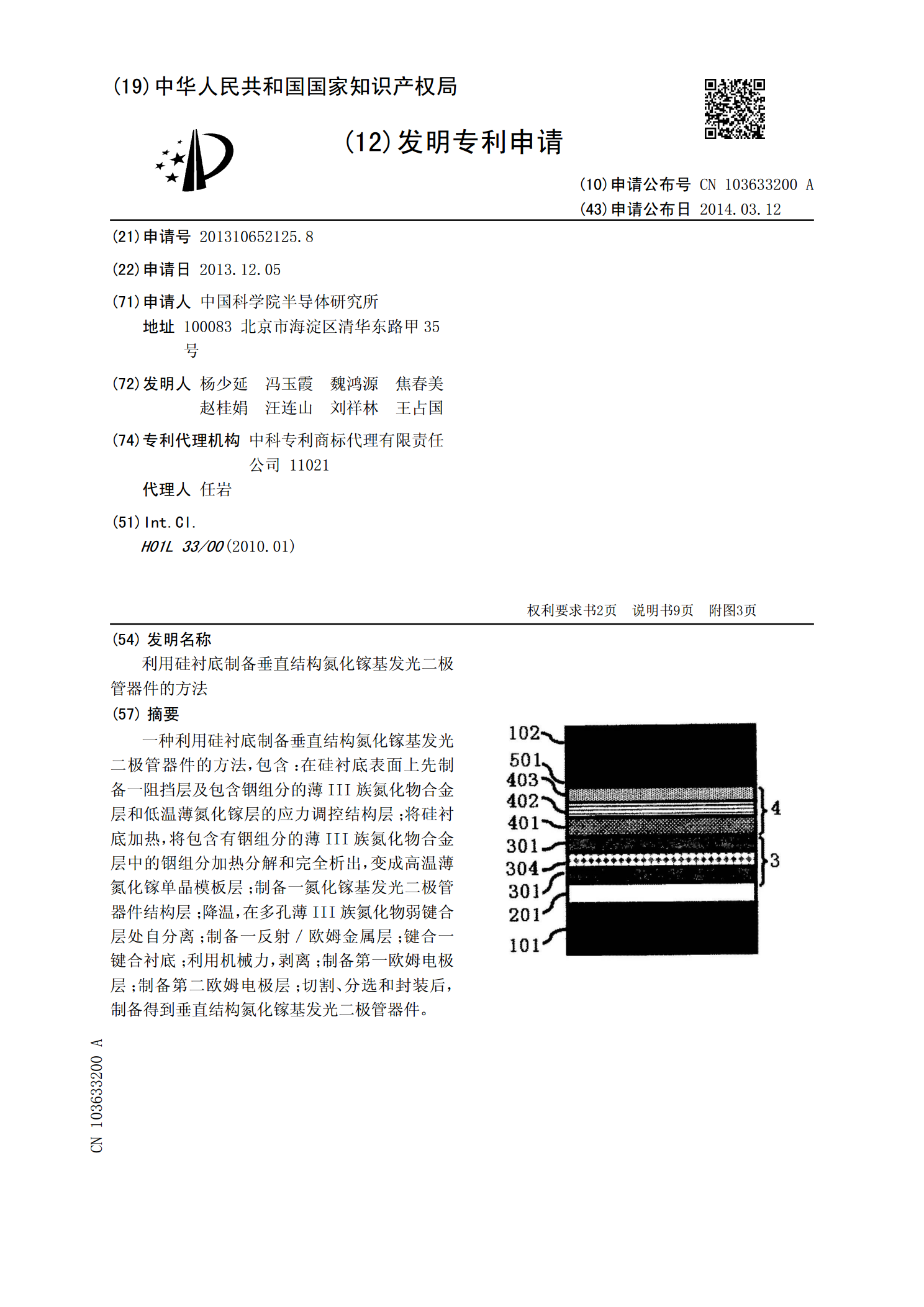

一种利用硅衬底制备垂直结构氮化镓基发光二极管器件的方法,包含:在硅衬底表面上先制备一阻挡层及包含铟组分的薄III族氮化物合金层和低温薄氮化镓层的应力调控结构层;将硅衬底加热,将包含有铟组分的薄III族氮化物合金层中的铟组分加热分解和完全析出,变成高温薄氮化镓单晶模板层;制备一氮化镓基发光二极管器件结构层;降温,在多孔薄III族氮化物弱键合层处自分离;制备一反射/欧姆金属层;键合一键合衬底;利用机械力,剥离;制备第一欧姆电极层;制备第二欧姆电极层;切割、分选和封装后,制备得到垂直结构氮化镓基发光二极管器件。

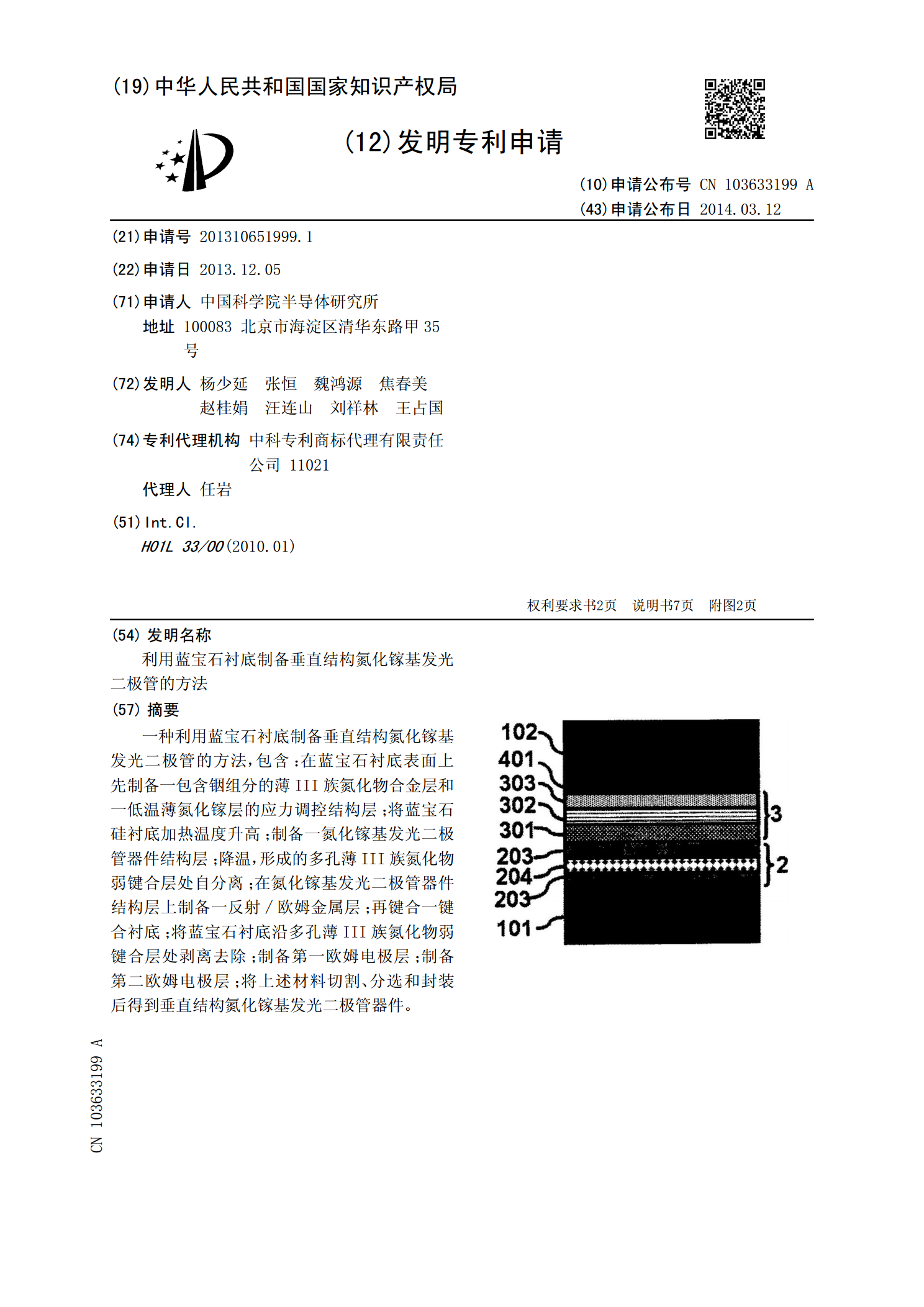

利用蓝宝石衬底制备垂直结构氮化镓基发光二极管的方法.pdf

一种利用蓝宝石衬底制备垂直结构氮化镓基发光二极管的方法,包含:在蓝宝石衬底表面上先制备一包含铟组分的薄III族氮化物合金层和一低温薄氮化镓层的应力调控结构层;将蓝宝石硅衬底加热温度升高;制备一氮化镓基发光二极管器件结构层;降温,形成的多孔薄III族氮化物弱键合层处自分离;在氮化镓基发光二极管器件结构层上制备一反射/欧姆金属层;再键合一键合衬底;将蓝宝石衬底沿多孔薄III族氮化物弱键合层处剥离去除;制备第一欧姆电极层;制备第二欧姆电极层;将上述材料切割、分选和封装后得到垂直结构氮化镓基发光二极管器件。

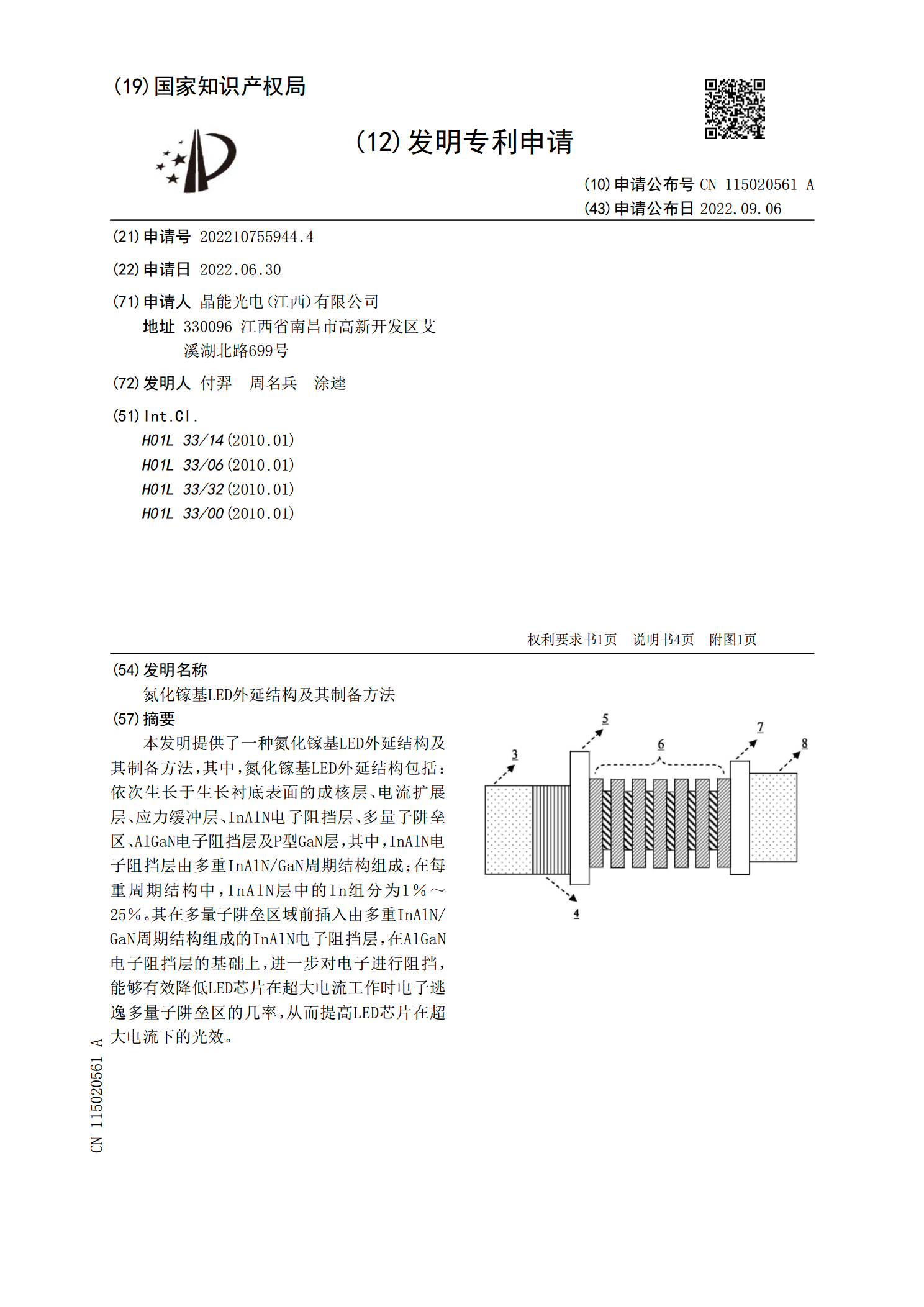

氮化镓基LED外延结构及其制备方法.pdf

本发明提供了一种氮化镓基LED外延结构及其制备方法,其中,氮化镓基LED外延结构包括:依次生长于生长衬底表面的成核层、电流扩展层、应力缓冲层、InAlN电子阻挡层、多量子阱垒区、AlGaN电子阻挡层及P型GaN层,其中,InAlN电子阻挡层由多重InAlN/GaN周期结构组成;在每重周期结构中,InAlN层中的In组分为1%~25%。其在多量子阱垒区域前插入由多重InAlN/GaN周期结构组成的InAlN电子阻挡层,在AlGaN电子阻挡层的基础上,进一步对电子进行阻挡,能够有效降低LED芯片在超大电流工作