CMOS器件及其制造方法.pdf

一条****淑淑

亲,该文档总共19页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

CMOS器件及其制造方法.pdf

本发明提供了一种CMOS器件及其制造方法,应用于半导体技术领域。在本发明提供的CMOS器件的制造方法中,并不需要像现有技术那样为了避免位于NMOS区和PMOS区之间的预留边界区(NP)出现doubleetch的情况,而加宽预留边界区(NP),本发明提供的制造方法允许预留边界区(NP)有一定宽度的doubleEtch,即形成所述开口,然后,在通过填充第二保护层的方式,将在形成源/漏区过程中导致的预留边界区(NP)引起的doubleEtch产生的开口填平,进而避免了doubleEtch产生的开口增大后

一种CMOS器件及其制造方法.pdf

本发明提供一种CMOS器件的制造方法,包括:提供衬底,所述衬底上具有沟道区域以及沟道区域上的栅介质层;在所述栅介质层上形成阻挡层;在所述阻挡层上形成功函数层;在所述功函数层上形成金属层;其中,在形成所述阻挡层之后,和/或形成所述功函数层之后,和/或形成所述金属层之后,还包括:进行等离子掺杂,等离子掺杂的离子为四族元素的离子。该方法调节阈值的控制精度高,且工艺灵活度高、简单易行,更适用于小尺寸器件中的多阈值的调控。

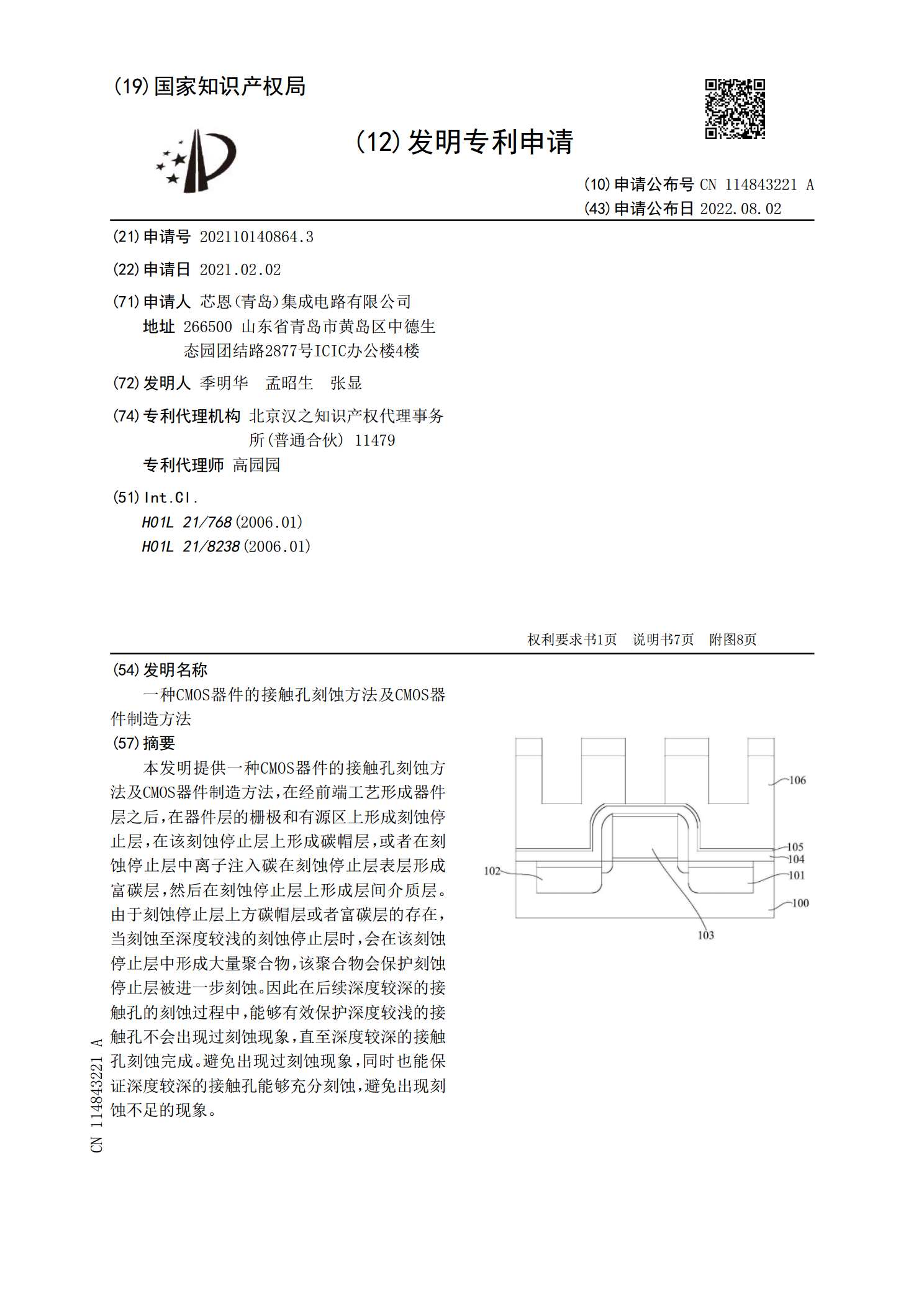

一种CMOS器件的接触孔刻蚀方法及CMOS器件制造方法.pdf

本发明提供一种CMOS器件的接触孔刻蚀方法及CMOS器件制造方法,在经前端工艺形成器件层之后,在器件层的栅极和有源区上形成刻蚀停止层,在该刻蚀停止层上形成碳帽层,或者在刻蚀停止层中离子注入碳在刻蚀停止层表层形成富碳层,然后在刻蚀停止层上形成层间介质层。由于刻蚀停止层上方碳帽层或者富碳层的存在,当刻蚀至深度较浅的刻蚀停止层时,会在该刻蚀停止层中形成大量聚合物,该聚合物会保护刻蚀停止层被进一步刻蚀。因此在后续深度较深的接触孔的刻蚀过程中,能够有效保护深度较浅的接触孔不会出现过刻蚀现象,直至深度较深的接触孔刻蚀

CMOS感光器件接触孔刻蚀方法及CMOS感光器件制造方法.pdf

提供了一种CMOS感光器件接触孔刻蚀方法及CMOS感光器件制造方法。CMOS感光器件接触孔刻蚀方法包括:步骤一,对包含氧化硅和氮化硅的层间介质层执行主刻蚀,以刻蚀层间介质层;步骤二,执行层间介质层过刻蚀,以进一步刻蚀层间介质层,氧化硅和氮化硅的刻蚀速率分别小于步骤一中的氧化硅和氮化硅的刻蚀速率,并且其中氧化硅刻蚀速率大于氧化硅刻蚀速率;步骤三,执行去胶;步骤四,执行刻蚀阻挡层刻蚀,以打开层间介质层刻蚀阶段的刻蚀阻挡层,使接触孔到达底部的镍硅化物层;步骤五,执行聚合物去除,用以清除刻蚀阻挡层刻蚀过程中等离子

CMOS集成器件的制造方法.pdf

本发明提供了一种CMOS集成器件的制造方法,应用于半导体技术领域。具体的,其针对现有技术中L90工艺平台为了节省光罩(1P4M,19ML),而提出去掉3.3VN/PwellPH和LDDPH4层光罩的方案,即,1.5V/3.3VCMOS管共用阱well光罩和离子注入IMP条件,并且3.3VNMOS使用1.5VPLDD0pocketIMP(As160KeV)打穿GPL(gateploy)来提升器件速度的过程中,由于栅极多晶硅膜层的均匀性差,导致的CMOS集成器件的器件稳定性差的问题,提出了可以通过在形成栅极结