抗干扰GNSS信号处理芯片、接收机和处理方法.pdf

慧娇****文章

亲,该文档总共21页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

抗干扰GNSS信号处理芯片、接收机和处理方法.pdf

本发明公开一种抗干扰GNSS信号处理芯片、接收机和处理方法,通过残留干扰检测电路检测当前的抗干扰效果,若当前权值更新周期下能够满足抗干扰要求,则按照当前权值更新周期下更新抗干扰信号权值直至干扰信号消失,若当前权值更新周期下不能满足抗干扰要求,则缩短当前权值更新周期,本实施例中的GNSS信号抗干扰方法,有利于在实现抗干扰功能的情况下尽量降低CPU负载,从而降低芯片的功耗,同时为CPU的其他线程留下了更多的时隙资源用于其他复杂计算。

GNSS接收机芯片、L波段信号解码方法和接收机.pdf

本发明公开了一种GNSS接收机芯片、L波段信号解码方法和接收机,通过CPU和L波段数字硬件电路共同完成对L波段符号的解调,与传统方案中由CPU单独完成L波段符号解调相比,降低了CPU的运算负载,能够在原有的GNSS接收机架构的基础上,实现L波段信号的解调,以实现高精度定位。本实施例中的方法降低了对CPU性能的要求,从而降低了芯片的成本和功耗;另外,累加电路将每N个符号同步时间偏差检测值进行非相干累加得到非相干累加和,以及将每N个符号插值结果进行相干累加得到相干累积和后,才向CPU发送一次中断以让CPU更新

基于CUDA的宽带GNSS接收机信号处理加速技术.docx

基于CUDA的宽带GNSS接收机信号处理加速技术随着全球定位系统(GNSS)技术的应用越来越广泛,GNSS接收机的性能和精度要求也越来越高,这使得GNSS信号处理成为接收机设计中的一项关键技术。近年来,GPU在计算机科学领域中的应用越来越广泛,并且由于其高并行计算能力和低成本等优势,被广泛应用于各种领域中的高性能计算。因此,基于CUDA的宽带GNSS接收机信号处理加速技术也在GNSS信号处理中得到了广泛的研究和应用。一、基于CUDA的宽带GNSS接收机信号处理1.1CUDA简介CUDA是一种并行计算平台和

GNSS软件接收机基带信号处理和导航解算的任务书.docx

GNSS软件接收机基带信号处理和导航解算的任务书任务书一、任务背景随着现代科技的不断发展,全球导航卫星系统(GNSS)在绝大多数领域中得到了广泛应用。GNSS软件接收机可以在普通计算机上实现GNSS操作,比传统硬件接收机更加灵活和方便,可以为各种设备提供定位、导航和时间同步等服务。本任务将要求完成GNSS软件接收机基带信号处理和导航解算,旨在为GNSS技术的进一步应用提供支持。二、任务目标1.实现GNSS软件接收机的基带信号处理,包括信号采集、载波频偏估计、码偏估计,以及伪距和载波相位的解调等操作;2.实

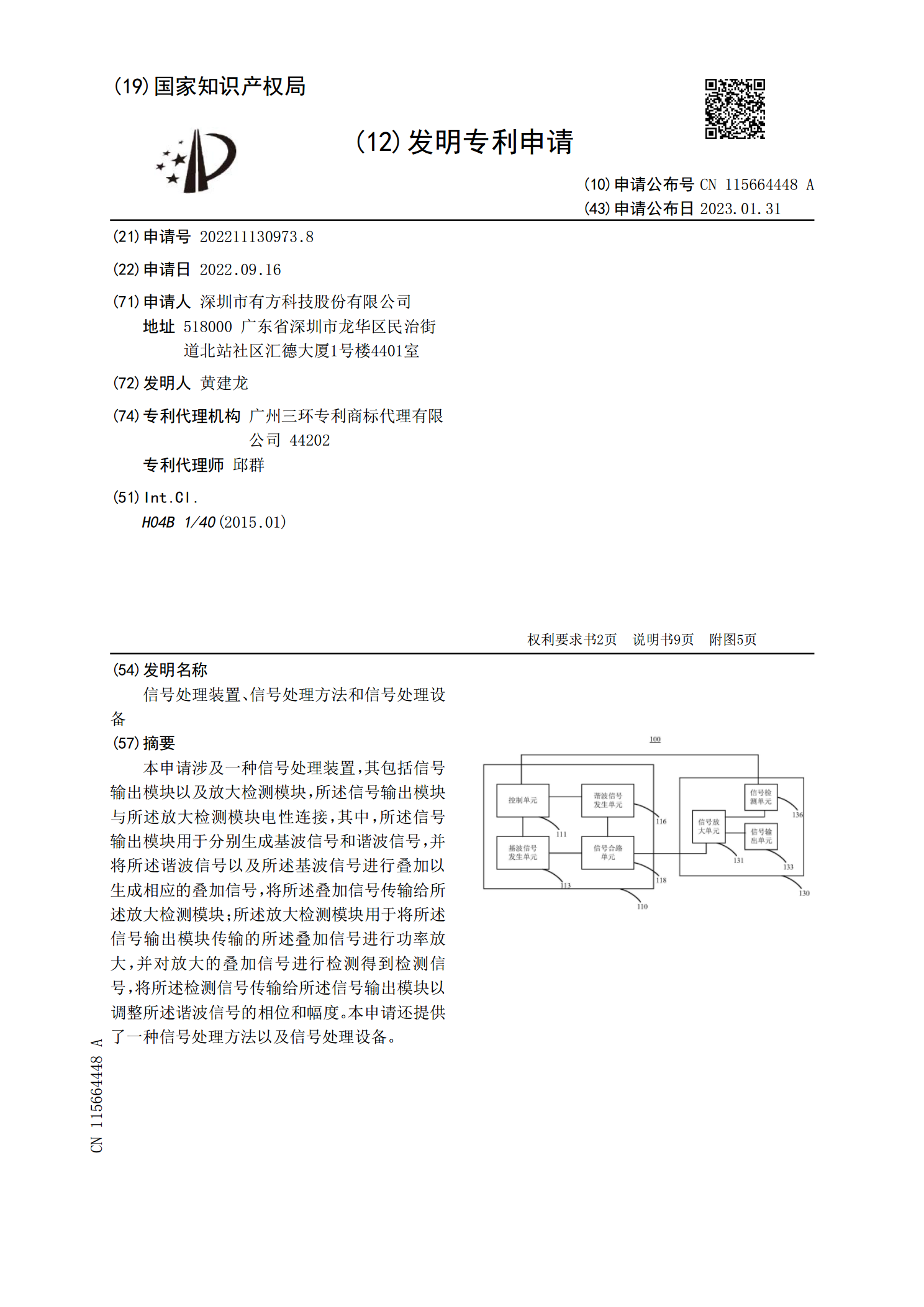

信号处理装置、信号处理方法和信号处理设备.pdf

本申请涉及一种信号处理装置,其包括信号输出模块以及放大检测模块,所述信号输出模块与所述放大检测模块电性连接,其中,所述信号输出模块用于分别生成基波信号和谐波信号,并将所述谐波信号以及所述基波信号进行叠加以生成相应的叠加信号,将所述叠加信号传输给所述放大检测模块;所述放大检测模块用于将所述信号输出模块传输的所述叠加信号进行功率放大,并对放大的叠加信号进行检测得到检测信号,将所述检测信号传输给所述信号输出模块以调整所述谐波信号的相位和幅度。本申请还提供了一种信号处理方法以及信号处理设备。