GNSS接收机芯片、L波段信号解码方法和接收机.pdf

是飞****文章

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

GNSS接收机芯片、L波段信号解码方法和接收机.pdf

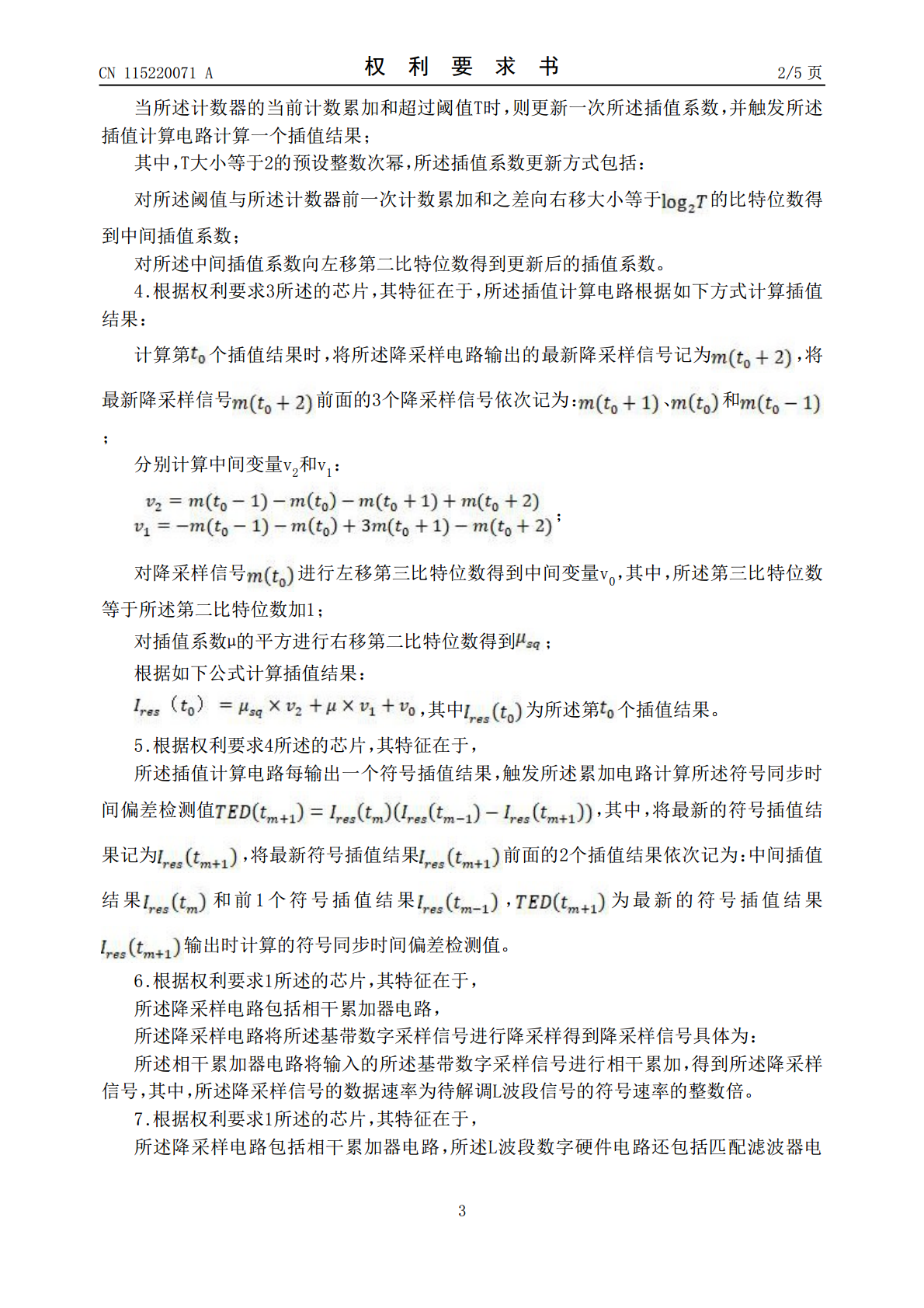

本发明公开了一种GNSS接收机芯片、L波段信号解码方法和接收机,通过CPU和L波段数字硬件电路共同完成对L波段符号的解调,与传统方案中由CPU单独完成L波段符号解调相比,降低了CPU的运算负载,能够在原有的GNSS接收机架构的基础上,实现L波段信号的解调,以实现高精度定位。本实施例中的方法降低了对CPU性能的要求,从而降低了芯片的成本和功耗;另外,累加电路将每N个符号同步时间偏差检测值进行非相干累加得到非相干累加和,以及将每N个符号插值结果进行相干累加得到相干累积和后,才向CPU发送一次中断以让CPU更新

抗干扰GNSS信号处理芯片、接收机和处理方法.pdf

本发明公开一种抗干扰GNSS信号处理芯片、接收机和处理方法,通过残留干扰检测电路检测当前的抗干扰效果,若当前权值更新周期下能够满足抗干扰要求,则按照当前权值更新周期下更新抗干扰信号权值直至干扰信号消失,若当前权值更新周期下不能满足抗干扰要求,则缩短当前权值更新周期,本实施例中的GNSS信号抗干扰方法,有利于在实现抗干扰功能的情况下尽量降低CPU负载,从而降低芯片的功耗,同时为CPU的其他线程留下了更多的时隙资源用于其他复杂计算。

接收无线信号的方法、芯片及无线接收机.pdf

本申请实施例公开了一种接收无线信号的方法、芯片及无线接收机,接收无线信号的方法包括:通过第一天线和第二天线分别接收第一射频信号和第二射频信号;其中,第一射频信号包括第一同步序列,第二射频信号包括第二同步序列;将第一同步序列和第二同步序列分别与本地同步序列进行相关同步,以获得对应的第一同步结果和第二同步结果;根据第一同步结果和第二同步结果分别确定第一射频信号对应的第一信噪比参数和第二射频信号对应的第二信噪比参数;基于第一信噪比参数与第二信噪比参数对第一射频信号和第二射频信号进行合并处理。

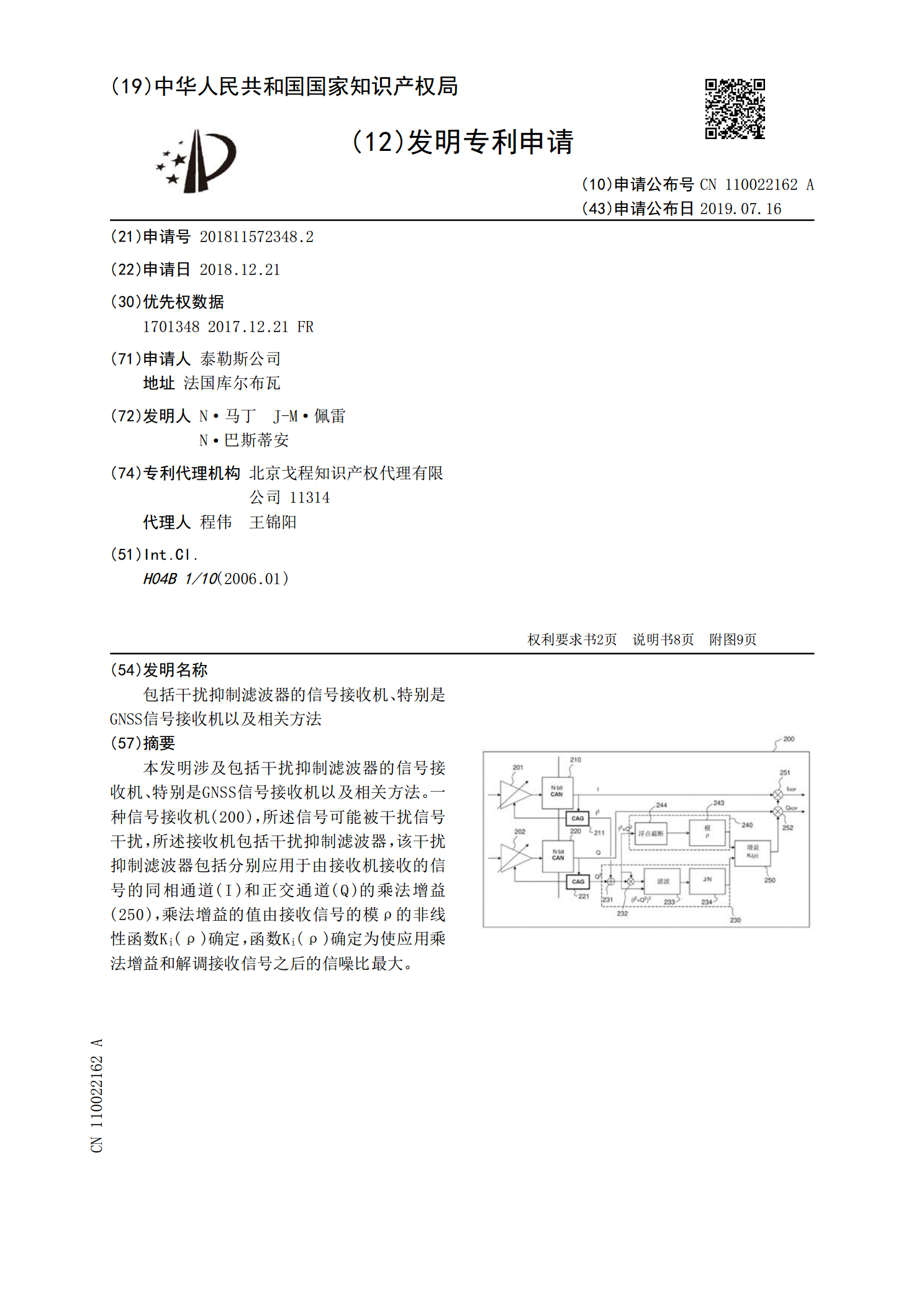

包括干扰抑制滤波器的信号接收机、特别是GNSS信号接收机以及相关方法.pdf

本发明涉及包括干扰抑制滤波器的信号接收机、特别是GNSS信号接收机以及相关方法。一种信号接收机(200),所述信号可能被干扰信号干扰,所述接收机包括干扰抑制滤波器,该干扰抑制滤波器包括分别应用于由接收机接收的信号的同相通道(I)和正交通道(Q)的乘法增益(250),乘法增益的值由接收信号的模ρ的非线性函数K

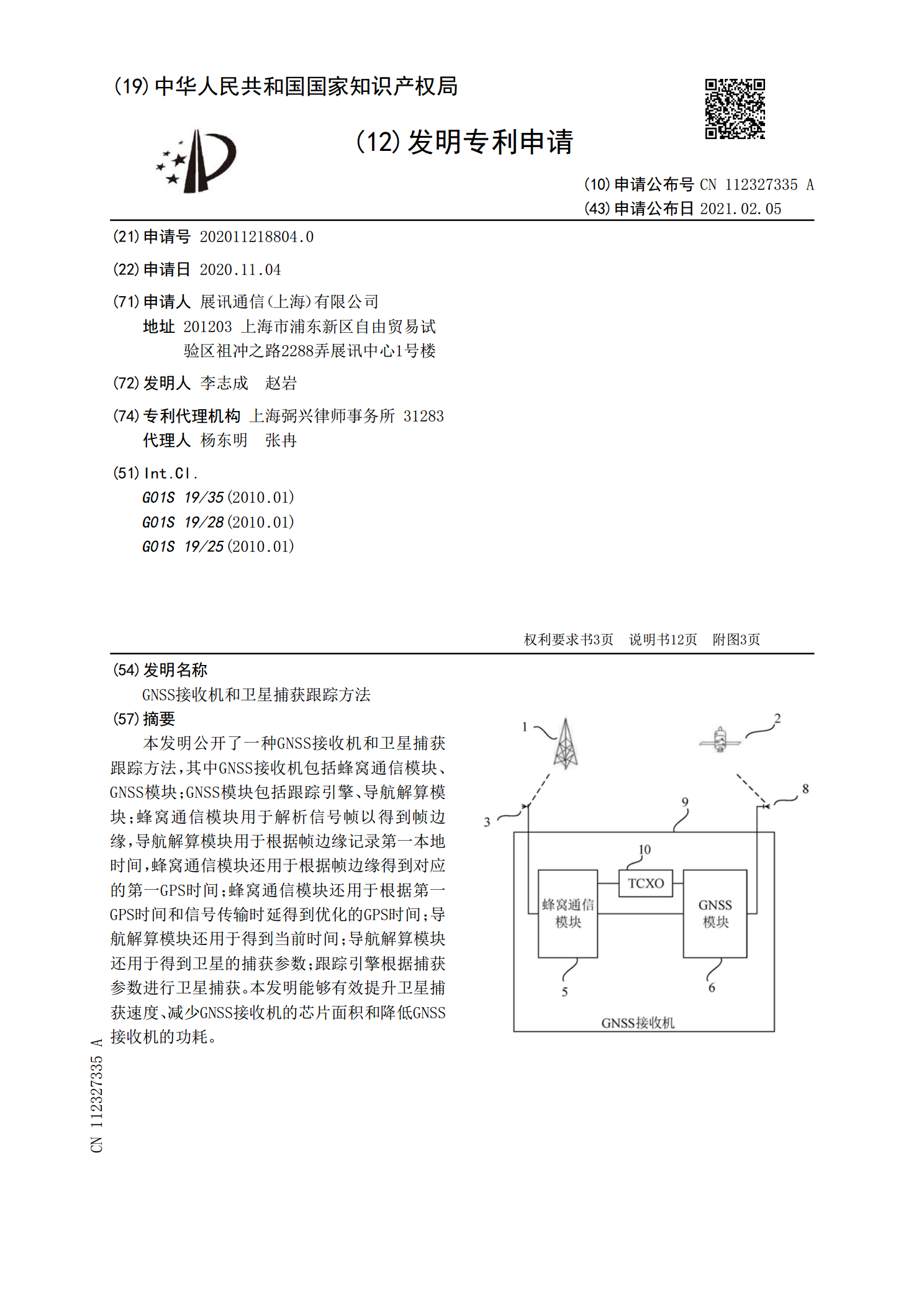

GNSS接收机和卫星捕获跟踪方法.pdf

本发明公开了一种GNSS接收机和卫星捕获跟踪方法,其中GNSS接收机包括蜂窝通信模块、GNSS模块;GNSS模块包括跟踪引擎、导航解算模块;蜂窝通信模块用于解析信号帧以得到帧边缘,导航解算模块用于根据帧边缘记录第一本地时间,蜂窝通信模块还用于根据帧边缘得到对应的第一GPS时间;蜂窝通信模块还用于根据第一GPS时间和信号传输时延得到优化的GPS时间;导航解算模块还用于得到当前时间;导航解算模块还用于得到卫星的捕获参数;跟踪引擎根据捕获参数进行卫星捕获。本发明能够有效提升卫星捕获速度、减少GNSS接收机的芯片