一种垂直结构LED芯片及其制作方法.pdf

努力****爱敏

亲,该文档总共13页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

一种垂直结构LED芯片及其制作方法.pdf

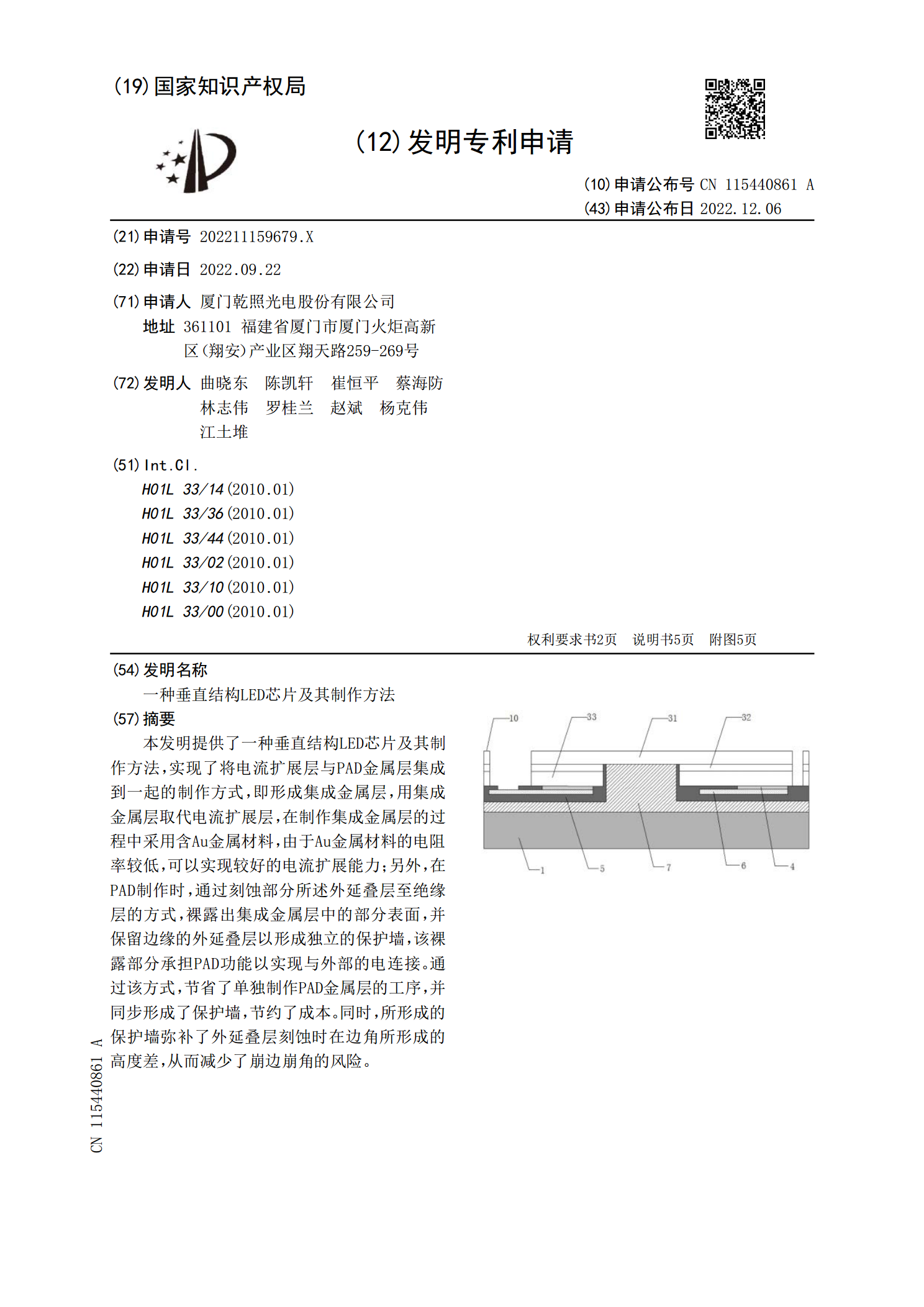

本发明提供了一种垂直结构LED芯片及其制作方法,实现了将电流扩展层与PAD金属层集成到一起的制作方式,即形成集成金属层,用集成金属层取代电流扩展层,在制作集成金属层的过程中采用含Au金属材料,由于Au金属材料的电阻率较低,可以实现较好的电流扩展能力;另外,在PAD制作时,通过刻蚀部分所述外延叠层至绝缘层的方式,裸露出集成金属层中的部分表面,并保留边缘的外延叠层以形成独立的保护墙,该裸露部分承担PAD功能以实现与外部的电连接。通过该方式,节省了单独制作PAD金属层的工序,并同步形成了保护墙,节约了成本。同时

垂直LED芯片结构及其制备方法.pdf

本发明提供一种垂直LED芯片结构及其制备方法,包括:1)提供蓝宝石衬底,在蓝宝石衬底上依次生长UID-GaN层、N-GaN层、多量子阱层以及P-GaN层;2)在P-GaN层上形成P电极;3)提供键合衬底,将键合衬底与步骤2)得到的结构键合;4)剥离蓝宝石衬底;5)去除UID-GaN层;6)在N-GaN层表面形成掩膜层,依据掩膜层,采用ICP刻蚀工艺去除部分位于切割道区域的GaN;7)去除掩膜层,采用湿法刻蚀工艺去除保留于切割道区域的GaN,同时形成台阶结构;8)对N-GaN层表面进行表面粗化,形成粗化微结

LED芯片结构的制作方法及LED芯片结构.pdf

本公开涉及色转换技术领域,尤其涉及一种LED芯片结构的制作方法及LED芯片结构,方法包括以下步骤:在芯片本体上涂覆二氧化硅材料,使其完全覆盖芯片本体的表面,以在芯片本体上形成二氧化硅覆盖层;对二氧化硅覆盖层的对应芯片本体内发光单元的位置刻蚀至使芯片本体的部分表面显露,以形成隔离矩阵槽;向二氧化硅覆盖层上涂覆色转换材料,直至完全填充隔离矩阵槽,以形成色转换层,本公开使二氧化硅覆盖层和芯片本体的氮化镓之间形成材料隔离分界线,保证了刻蚀过程中的刻蚀终点明确,从而避免了损伤到芯片本体内部的发光单元,保护了芯片本体

垂直堆叠的LED芯片、制作方法、设备以及其制作方法.pdf

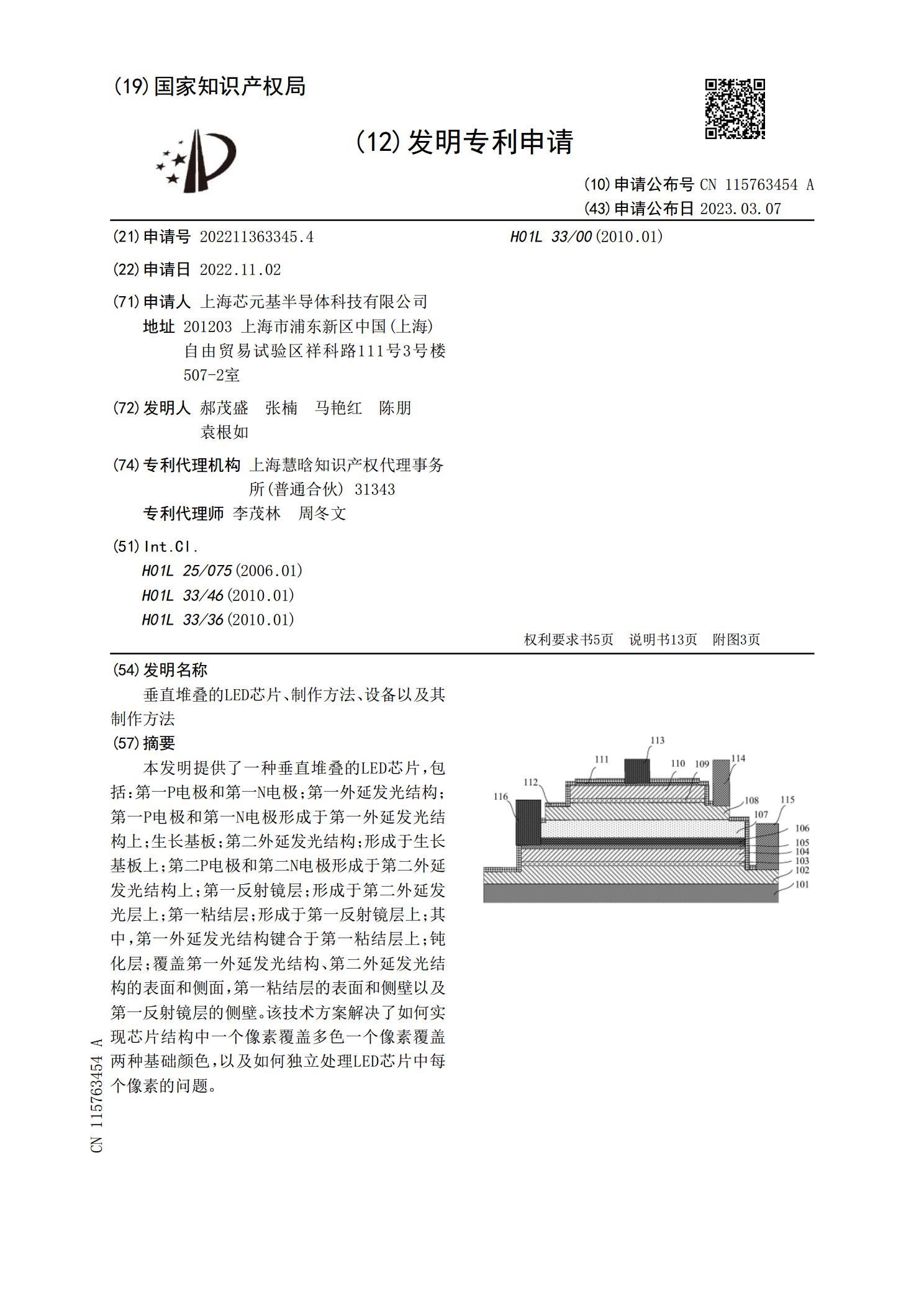

本发明提供了一种垂直堆叠的LED芯片,包括:第一P电极和第一N电极;第一外延发光结构;第一P电极和第一N电极形成于第一外延发光结构上;生长基板;第二外延发光结构;形成于生长基板上;第二P电极和第二N电极形成于第二外延发光结构上;第一反射镜层;形成于第二外延发光层上;第一粘结层;形成于第一反射镜层上;其中,第一外延发光结构键合于第一粘结层上;钝化层;覆盖第一外延发光结构、第二外延发光结构的表面和侧面,第一粘结层的表面和侧壁以及第一反射镜层的侧壁。该技术方案解决了如何实现芯片结构中一个像素覆盖多色一个像素覆盖

一种新型倒装LED芯片结构及其制作方法.pdf

本发明涉及一种新型倒装LED芯片结构及其制作方法,其芯片结构包括蓝宝石衬底、外延结构层、反光层、接触金属层以及采用DBR结构的绝缘层;其制作方法首先在蓝宝石衬底上依次生长出包括N-GaN层、量子阱层和P-GaN层的外延结构层,并蚀刻出N区电极槽;在P-GaN层的表面蒸镀反光层;在所述反光层上蒸镀采用DBR结构的绝缘层,该绝缘层留有空白区域,该空白区域使得反光层上的对应区域裸露,形成P区电极槽;在所述P区电极槽和N区电极槽内分别设置互不接触的P区接触金属和N区接触金属,形成接触金属层。与现有技术相比,本发明