一种具有低米勒电容的VDMOS器件结构及其制备方法.pdf

王秋****哥哥

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

一种具有低米勒电容的VDMOS器件结构及其制备方法.pdf

本发明提供一种低米勒电容的VDMOS器件结构及其制作方法。其器件结构的多晶硅栅分控制栅和屏蔽栅两部分,其中位于沟道上的多晶硅栅称为控制栅,控制沟道开启和关断,而位于厚场氧层上面的多晶硅与源电极相连或不相连,称为屏蔽栅。所述新型VDMOS器件的制作方法需要将常规VDMOS的制作方法与局部氧化(LOCOS)工艺相结合,利用一次栅极工艺同时形成控制栅和屏蔽栅,从而节省了制作器件的成本,所述厚氧区域10的引入能够显著减小器件的米勒电容,从而改善VDMOS器件的开关特性。

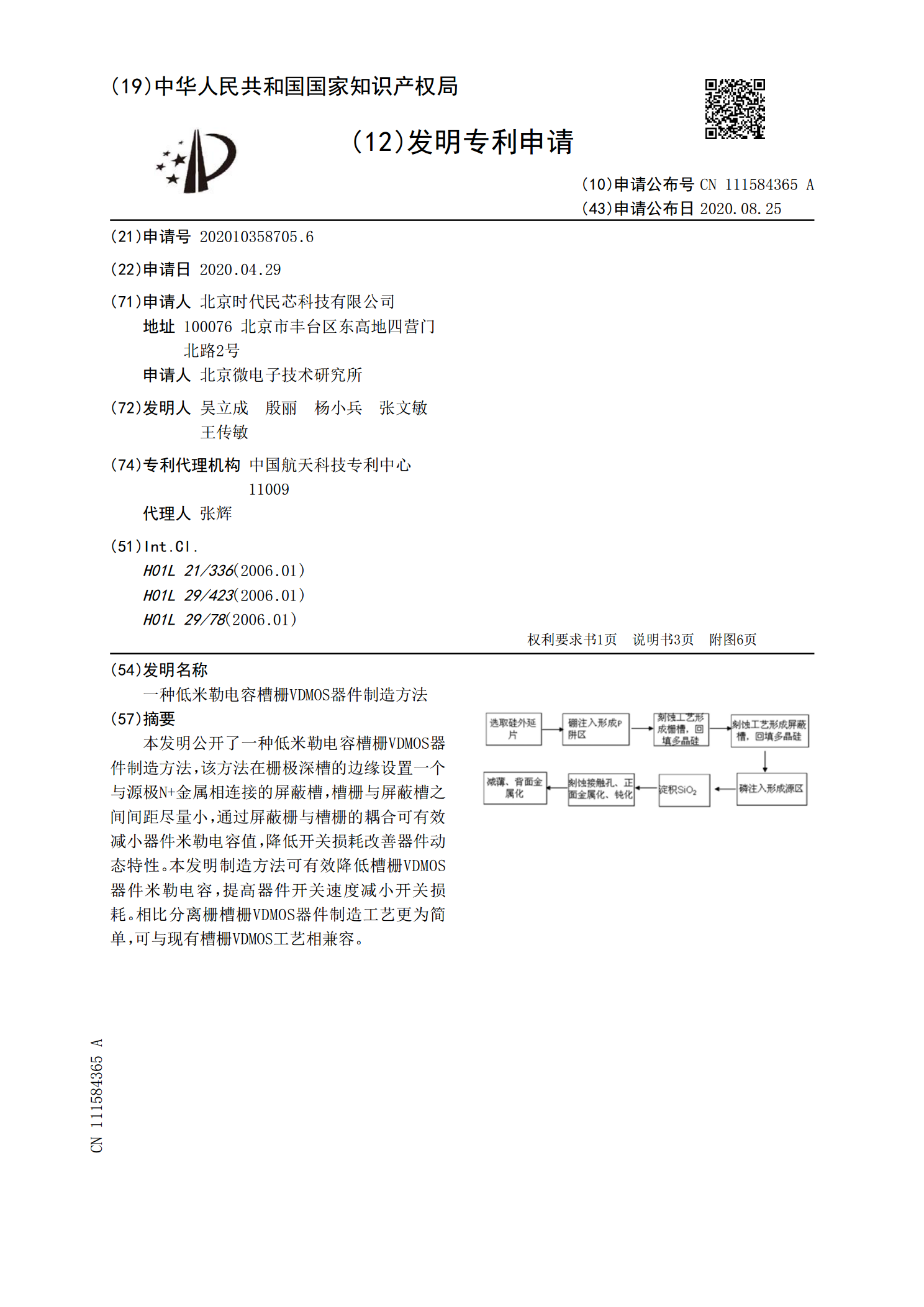

一种低米勒电容槽栅VDMOS器件制造方法.pdf

本发明公开了一种低米勒电容槽栅VDMOS器件制造方法,该方法在栅极深槽的边缘设置一个与源极N+金属相连接的屏蔽槽,槽栅与屏蔽槽之间间距尽量小,通过屏蔽栅与槽栅的耦合可有效减小器件米勒电容值,降低开关损耗改善器件动态特性。本发明制造方法可有效降低槽栅VDMOS器件米勒电容,提高器件开关速度减小开关损耗。相比分离栅槽栅VDMOS器件制造工艺更为简单,可与现有槽栅VDMOS工艺相兼容。

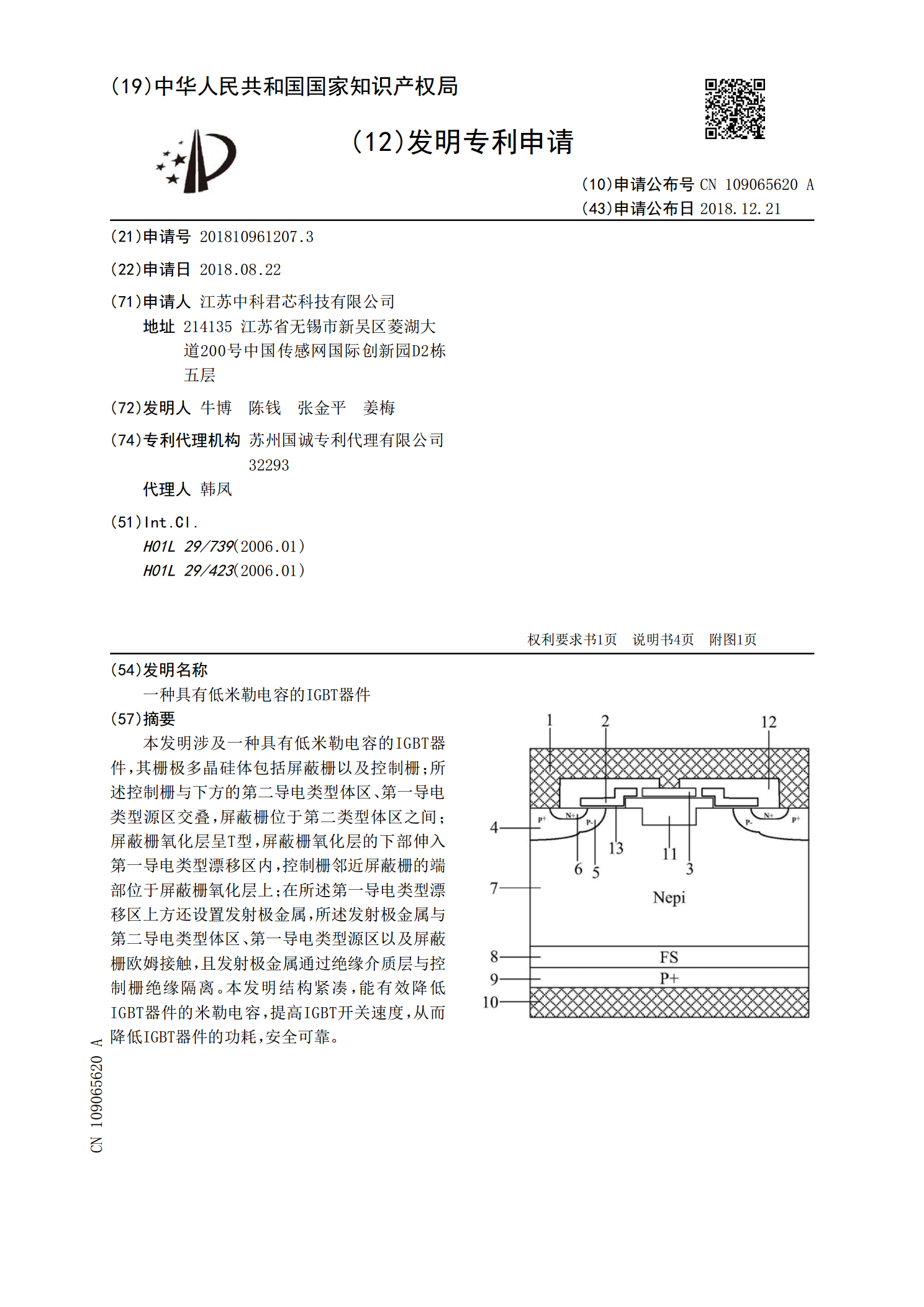

一种具有低米勒电容的IGBT器件.pdf

本发明涉及一种具有低米勒电容的IGBT器件,其栅极多晶硅体包括屏蔽栅以及控制栅;所述控制栅与下方的第二导电类型体区、第一导电类型源区交叠,屏蔽栅位于第二类型体区之间;屏蔽栅氧化层呈T型,屏蔽栅氧化层的下部伸入第一导电类型漂移区内,控制栅邻近屏蔽栅的端部位于屏蔽栅氧化层上;在所述第一导电类型漂移区上方还设置发射极金属,所述发射极金属与第二导电类型体区、第一导电类型源区以及屏蔽栅欧姆接触,且发射极金属通过绝缘介质层与控制栅绝缘隔离。本发明结构紧凑,能有效降低IGBT器件的米勒电容,提高IGBT开关速度,从而降

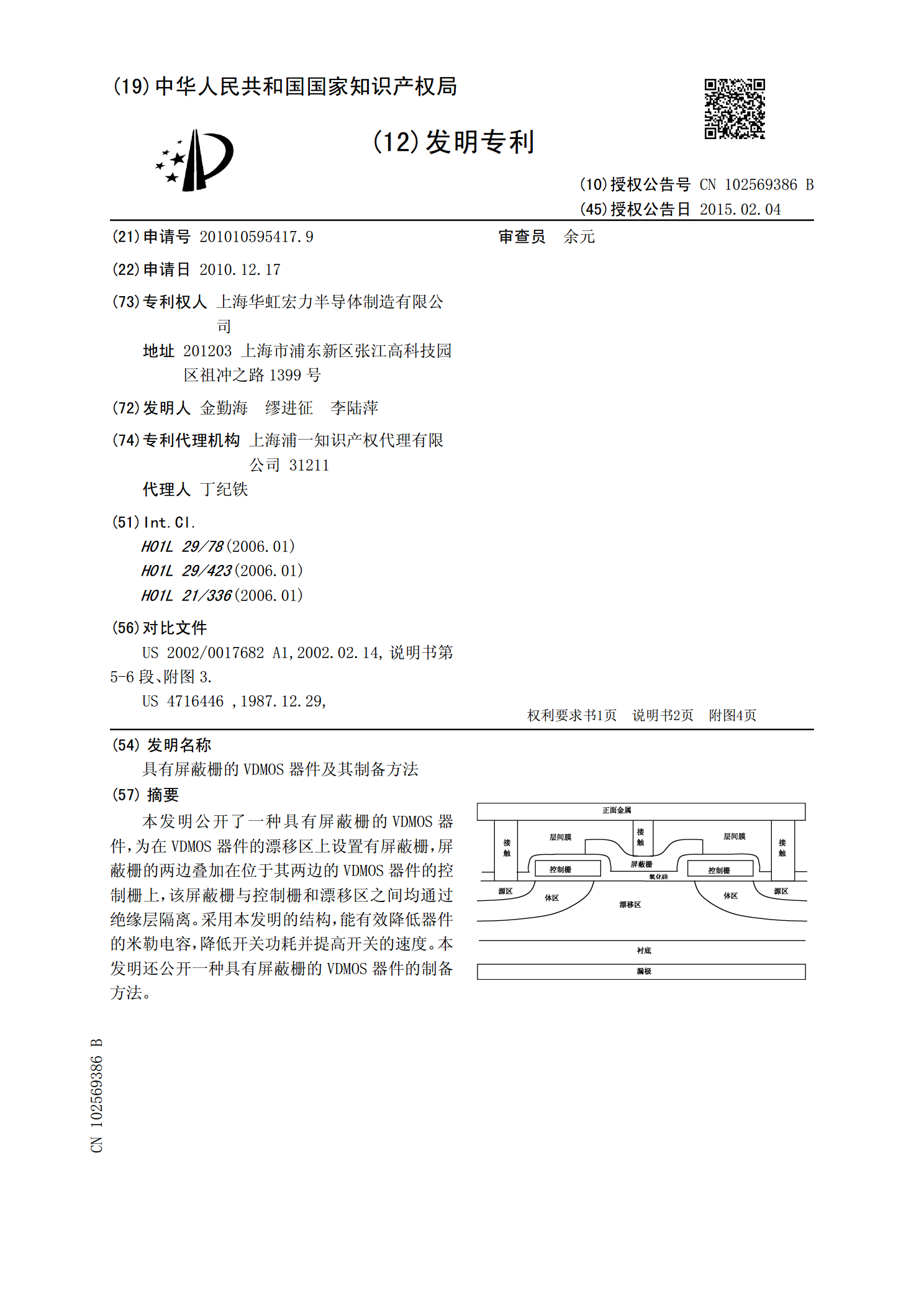

具有屏蔽栅的VDMOS器件及其制备方法.pdf

本发明公开了一种具有屏蔽栅的VDMOS器件,为在VDMOS器件的漂移区上设置有屏蔽栅,屏蔽栅的两边叠加在位于其两边的VDMOS器件的控制栅上,该屏蔽栅与控制栅和漂移区之间均通过绝缘层隔离。采用本发明的结构,能有效降低器件的米勒电容,降低开关功耗并提高开关的速度。本发明还公开一种具有屏蔽栅的VDMOS器件的制备方法。

一种低密勒电容的VDMOS器件.pdf

本发明提供一种低密勒电容的VDMOS器件结构,属于功率半导体器件技术领域。本发明提出的一种低密勒电容VDMOS器件,通过将多晶硅电极区进行不同类型掺杂,以PN结自隔离的方法将其分为三段,将与JFET区交叠的部分和金属化源极短接,从而使得栅漏的交叠面积大大减小,实现了对密勒电容的有效降低。另外通过在JFET区顶部引入高掺杂区以弥补导通电阻的增大。因此,本发明结构在保证VDMOS原有的基本电学性能的基础上,有效地降低了密勒电容,减小了器件的开关损耗。