多晶硅刻蚀方法.pdf

曾琪****是我

亲,该文档总共11页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

多晶硅刻蚀方法.pdf

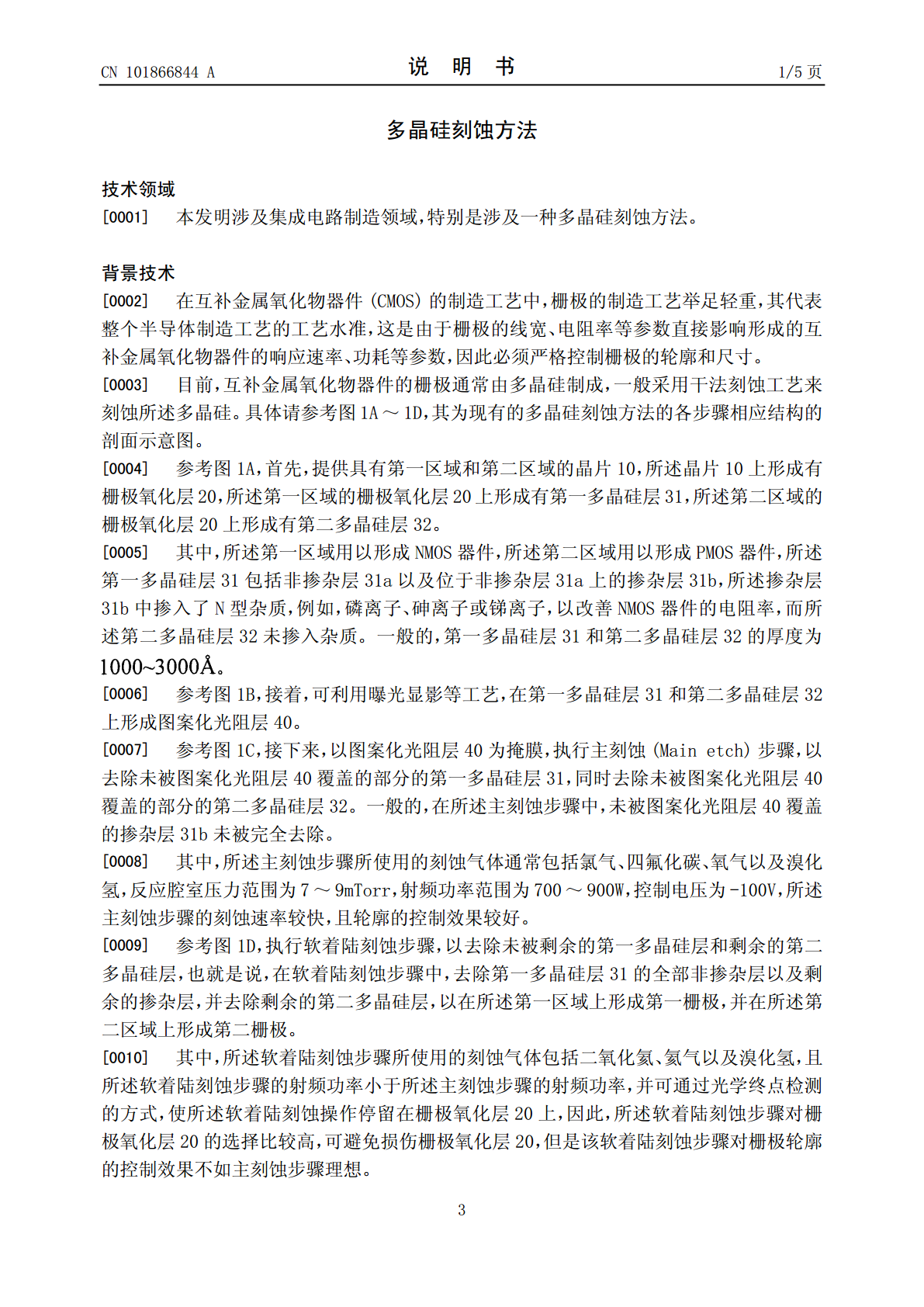

本发明公开了一种多晶硅刻蚀方法,该方法包括:提供具有第一区域和第二区域的晶片,所述第一区域形成有第一多晶硅层,所述第二区域形成有第二多晶硅层,其中,第一多晶硅层包括非掺杂层以及位于非掺杂层上的掺杂层;在第一多晶硅层和第二多晶硅层上形成图案化光阻层;执行第一刻蚀步骤,以去除未被图案化光阻层覆盖的部分第一多晶硅层和部分第二多晶硅层;执行第二刻蚀步骤,以去除未被图案化光阻层覆盖的剩余的第一多晶硅层和剩余的第二多晶硅层;在所述第一刻蚀步骤中,未被图案化光阻层覆盖的掺杂层被完全去除,从而确保形成具有垂直轮廓的栅极,

一种多晶硅刻蚀方法.pdf

本发明提供一种多晶硅刻蚀方法,包括以下步骤:S1:在多晶硅层表面形成SiN层,并刻蚀所述SiN层使其图形化,得到SiN硬掩膜层;S2:在所述SiN硬掩膜层周围未被刻蚀彻底的SiN残留颗粒与所述多晶硅层之间形成氧化层;S3:采用湿法腐蚀去除所述氧化层,使所述SiN残留颗粒因悬空而脱离所述多晶硅层;S4:以所述SiN硬掩膜层作为掩模对所述多晶硅层进行刻蚀。本发明避免了因氮化硅残留颗粒的遮挡阻碍后续多晶硅刻蚀,极大地降低了多晶硅残留缺陷的产生。本发明的多晶硅刻蚀方法无需增加光刻次数,对后续工艺几乎没有影响,并且

闪存器件浮栅多晶硅的刻蚀方法.pdf

本申请涉及半导体集成电路制造技术领域,具体涉及一种闪存器件浮栅多晶硅的刻蚀方法。该方法包括:形成半导体的基底层,所述基底层包括存储区,所述存储区中形成有多个存储单元,相邻两个存储单元之间相隔离;在所述基底层上沉积形成多晶硅层;使得所述多晶硅层的上表面平坦化;定义出闪存器件的存储区,对平坦化后的存储区位置处的多晶硅层进行回刻蚀,形成覆盖在各个所述存储单元位置处的浮栅结构。本申请可以解决相关技术中相邻两个存储单元之间残留的浮栅多晶硅层对相邻两个存储单元浮栅结构造成桥连的问题,能够提高晶片的良率。

水性分散体系和多晶硅片的刻蚀方法.pdf

公开了一种用于刻蚀多晶硅片的水性分散体系,它包括一种水性介质和分散于所述水性介质中的氢氧化铋和至少一种阴离子性或非离子性表面活性剂,所述氢氧化铋的浓度为0.0001-0.5mol/l,所述至少一种阴离子性或非离子性表面活性剂的浓度为1-5000ppm(以所述水性分散体系的总重量计)。还公开了用该水性分散体系刻蚀多晶硅片的方法和用此刻蚀方法得到的太阳能多晶硅片电池。

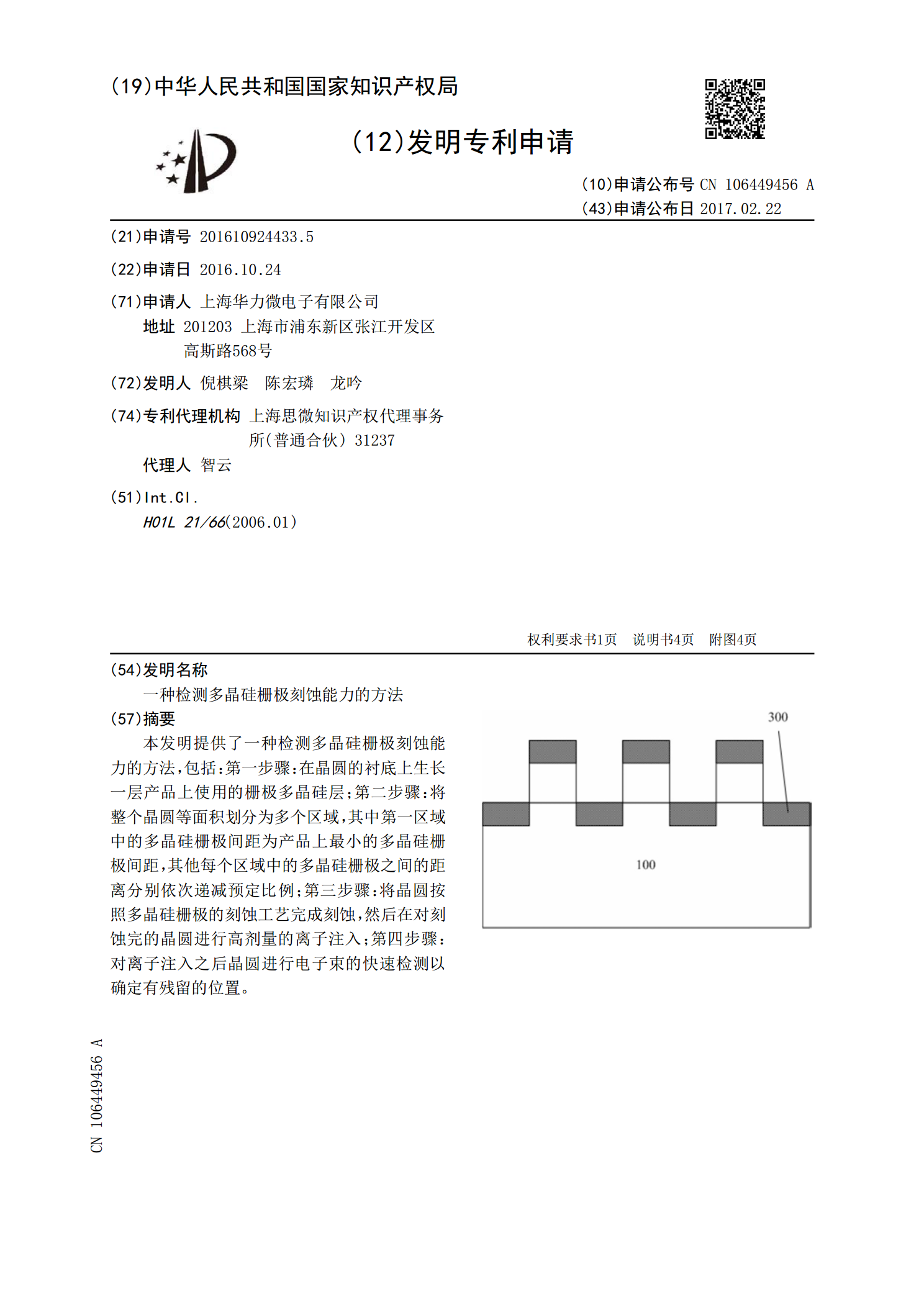

一种检测多晶硅栅极刻蚀能力的方法.pdf

本发明提供了一种检测多晶硅栅极刻蚀能力的方法,包括:第一步骤:在晶圆的衬底上生长一层产品上使用的栅极多晶硅层;第二步骤:将整个晶圆等面积划分为多个区域,其中第一区域中的多晶硅栅极间距为产品上最小的多晶硅栅极间距,其他每个区域中的多晶硅栅极之间的距离分别依次递减预定比例;第三步骤:将晶圆按照多晶硅栅极的刻蚀工艺完成刻蚀,然后在对刻蚀完的晶圆进行高剂量的离子注入;第四步骤:对离子注入之后晶圆进行电子束的快速检测以确定有残留的位置。