控制物理层芯片的方法及控制电路.pdf

秋花****姐姐

亲,该文档总共25页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

控制物理层芯片的方法及控制电路.pdf

本发明提供一种控制物理层芯片的方法及控制电路。其中,控制电路包括:定时时钟模块、第一寄存器模块、第一状态锁存模块、状态轮转模块和MDIO控制器;状态轮转模块,用于根据定时时钟模块提供的时钟信号和第一状态锁存模块提供的变化信息,对第一寄存器模块进行读操作,并根据读取结果向述MDIO控制器提供第一地址信息和控制数据信息;MDIO控制器,用于按照预设的周期将控制数据信息写入第一地址信息对应的PHY芯片的引脚的寄存器,以对PHY芯片的引脚的状态进行自动控制。采用本发明技术方案可以用同一个MDIO控制器对多个PHY

激光器驱动控制电路、芯片及控制方法.pdf

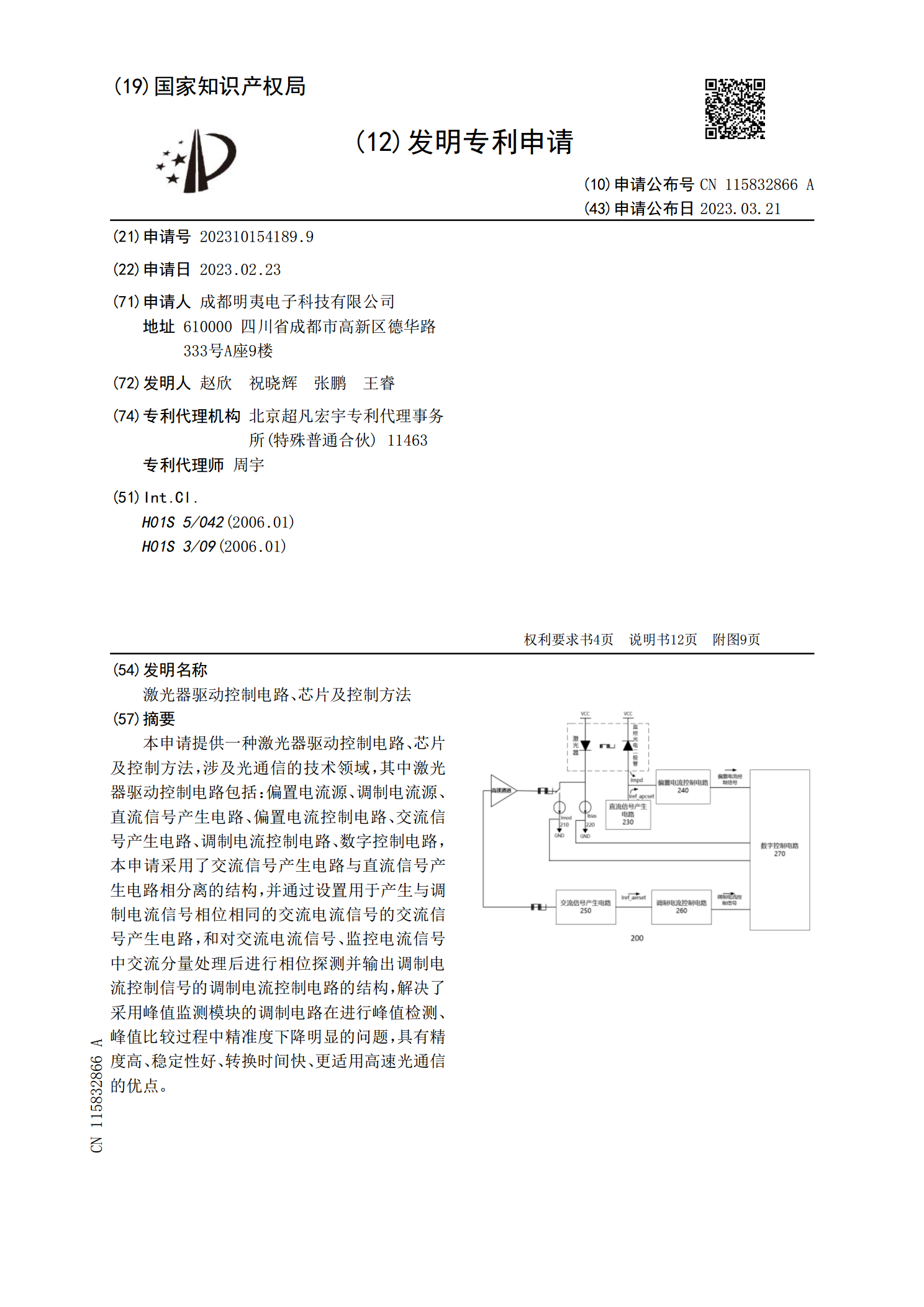

本申请提供一种激光器驱动控制电路、芯片及控制方法,涉及光通信的技术领域,其中激光器驱动控制电路包括:偏置电流源、调制电流源、直流信号产生电路、偏置电流控制电路、交流信号产生电路、调制电流控制电路、数字控制电路,本申请采用了交流信号产生电路与直流信号产生电路相分离的结构,并通过设置用于产生与调制电流信号相位相同的交流电流信号的交流信号产生电路,和对交流电流信号、监控电流信号中交流分量处理后进行相位探测并输出调制电流控制信号的调制电流控制电路的结构,解决了采用峰值监测模块的调制电路在进行峰值检测、峰值比较过程

感应面板的控制芯片、控制电路及控制方法.pdf

本发明提供一种感应面板的控制电路,第一控制芯片包含第一时钟输入管脚、时钟输出管脚、主要数据管脚及第一次要数据管脚,通过主要数据管脚传送一命令。第二控制芯片包含第二时钟输入管脚,用来接收时钟;以及第二次要数据管脚,用来接收命令。第三控制芯片包含:第三时钟输入管脚接收时钟;第三次要数据管脚,用来接收命令。第二控制芯片根据时钟及第一目标数值传送或接收第一数据;第三控制芯片根据时钟及第二目标数值传送或接收第二数据;第一目标数值不等于第二目标数值。本发明的分布式架构,有助于简化绕线的复杂度、使电路布局更有弹性,不增

Flash芯片读写控制电路和方法、AMOLED应用电路.pdf

本发明公开了一种用于Flash芯片的读写控制电路,包括:时序控制电路,其生成用于Flash芯片的读写时序信号;以及第一非易失性存储器,其用于存储与Flash芯片中的多个分区对应的多个标志位,所述标志位中的每一个指示与其对应的一个分区是否被正常写入。还公开了一种用于Flash芯片的读写控制方法和具有所述读写控制电路的用于电学补偿机制的AMOLED应用电路。通过设置标志位将每个分区做标记,并且设置备份存储区以保留原始的补偿数据,保证了例如在发生掉电的情况下显示的连续性和电学补偿数据的完整性。

动态范围控制电路、音频处理芯片及其音频处理方法.pdf

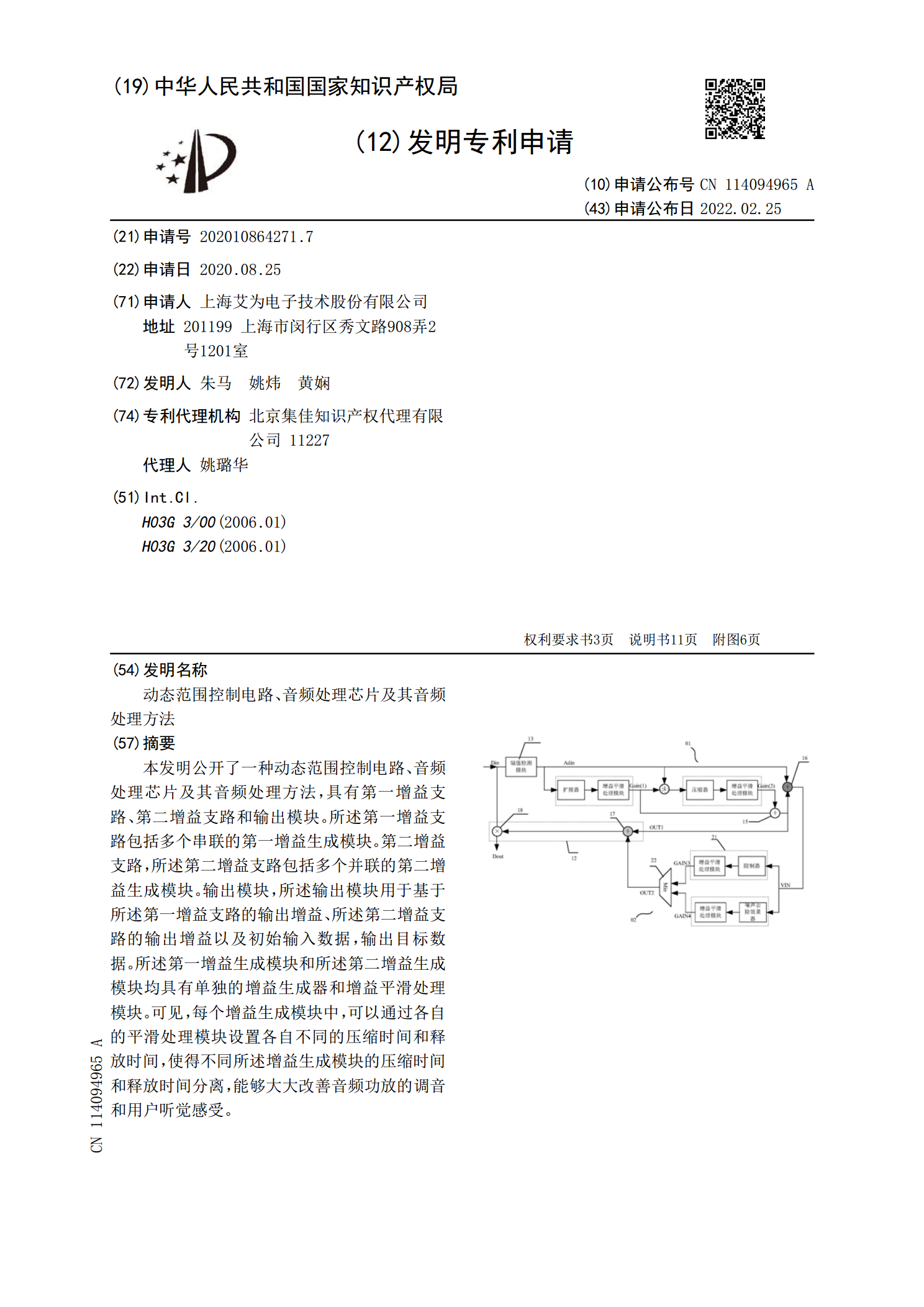

本发明公开了一种动态范围控制电路、音频处理芯片及其音频处理方法,具有第一增益支路、第二增益支路和输出模块。所述第一增益支路包括多个串联的第一增益生成模块。第二增益支路,所述第二增益支路包括多个并联的第二增益生成模块。输出模块,所述输出模块用于基于所述第一增益支路的输出增益、所述第二增益支路的输出增益以及初始输入数据,输出目标数据。所述第一增益生成模块和所述第二增益生成模块均具有单独的增益生成器和增益平滑处理模块。可见,每个增益生成模块中,可以通过各自的平滑处理模块设置各自不同的压缩时间和释放时间,使得不同