感应面板的控制芯片、控制电路及控制方法.pdf

宜欣****外呢

亲,该文档总共18页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

感应面板的控制芯片、控制电路及控制方法.pdf

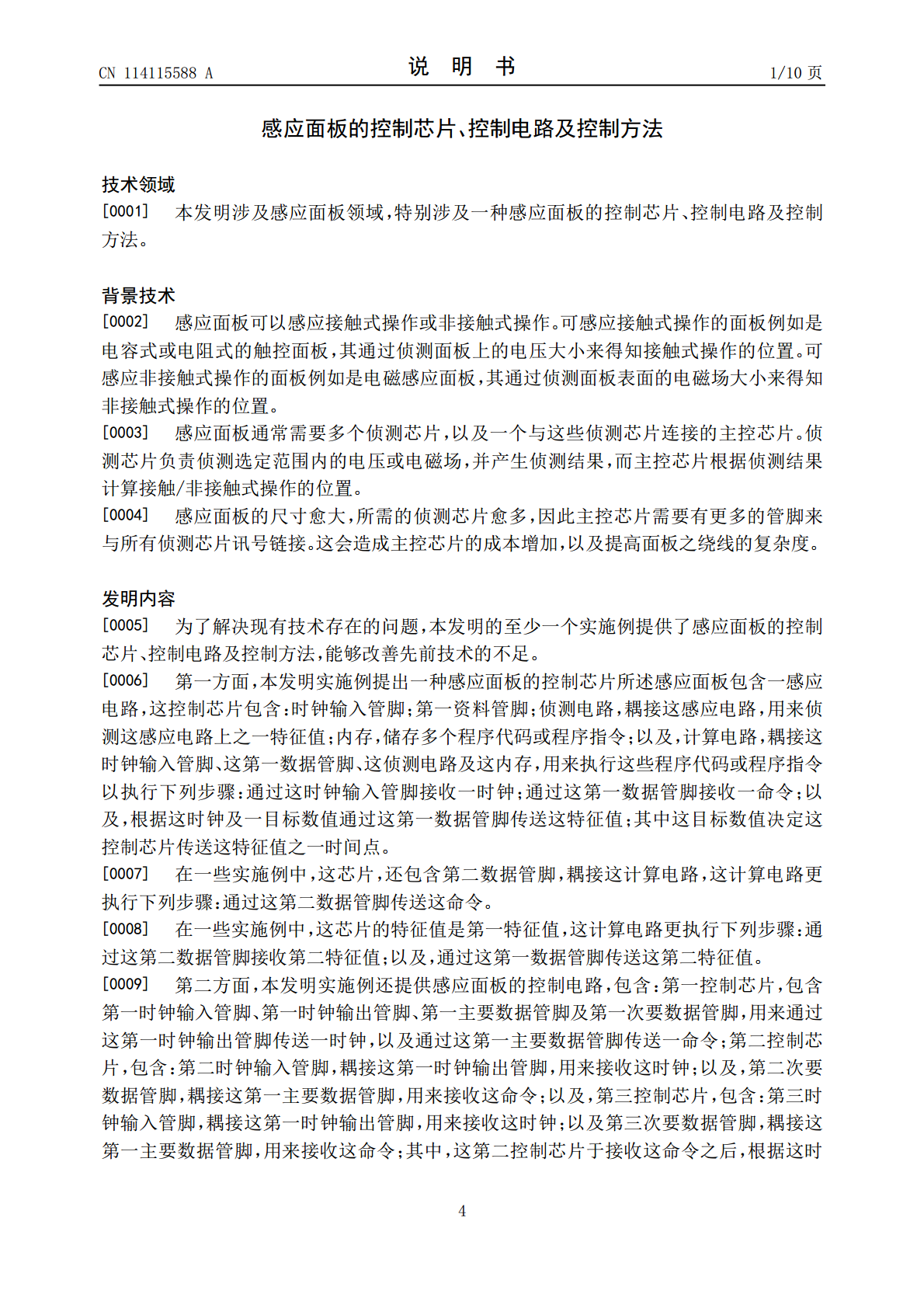

本发明提供一种感应面板的控制电路,第一控制芯片包含第一时钟输入管脚、时钟输出管脚、主要数据管脚及第一次要数据管脚,通过主要数据管脚传送一命令。第二控制芯片包含第二时钟输入管脚,用来接收时钟;以及第二次要数据管脚,用来接收命令。第三控制芯片包含:第三时钟输入管脚接收时钟;第三次要数据管脚,用来接收命令。第二控制芯片根据时钟及第一目标数值传送或接收第一数据;第三控制芯片根据时钟及第二目标数值传送或接收第二数据;第一目标数值不等于第二目标数值。本发明的分布式架构,有助于简化绕线的复杂度、使电路布局更有弹性,不增

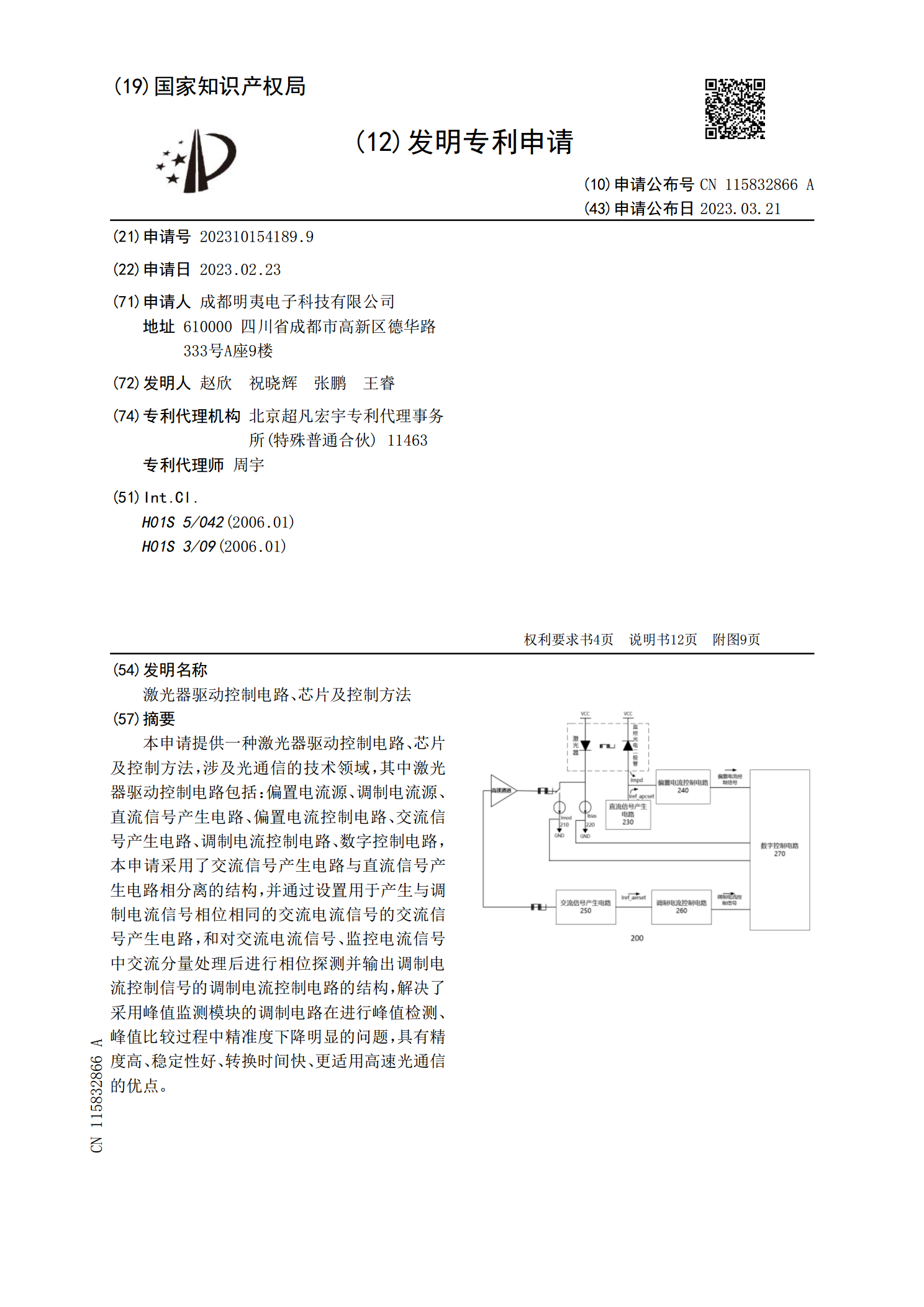

激光器驱动控制电路、芯片及控制方法.pdf

本申请提供一种激光器驱动控制电路、芯片及控制方法,涉及光通信的技术领域,其中激光器驱动控制电路包括:偏置电流源、调制电流源、直流信号产生电路、偏置电流控制电路、交流信号产生电路、调制电流控制电路、数字控制电路,本申请采用了交流信号产生电路与直流信号产生电路相分离的结构,并通过设置用于产生与调制电流信号相位相同的交流电流信号的交流信号产生电路,和对交流电流信号、监控电流信号中交流分量处理后进行相位探测并输出调制电流控制信号的调制电流控制电路的结构,解决了采用峰值监测模块的调制电路在进行峰值检测、峰值比较过程

TFT面板控制电路.pdf

一种TFT面板控制电路,包括薄膜晶体管T1、T2、T3、T4、T5、T6、T7、T8、T9、T10、T11、T12,所述T1的源极与前信号源FW连接,栅极与前二级驱动信号Gn‑2连接,漏极与T2的栅极、T4的栅极、T7的漏极、T3的源极、T9的源极连接;T7的源极与后信号源BW连接,栅极与后二级驱动信号Gn+2连接;所述T4的源极与时钟信号CK连接,T4的漏极通过第一电容与T4的栅极连接,T4的漏极还与当前级驱动信号Gn、T5的源极、T6的源极、T10的源极连接。本发明引入三个TFT组成的电位下拉结构,和

控制物理层芯片的方法及控制电路.pdf

本发明提供一种控制物理层芯片的方法及控制电路。其中,控制电路包括:定时时钟模块、第一寄存器模块、第一状态锁存模块、状态轮转模块和MDIO控制器;状态轮转模块,用于根据定时时钟模块提供的时钟信号和第一状态锁存模块提供的变化信息,对第一寄存器模块进行读操作,并根据读取结果向述MDIO控制器提供第一地址信息和控制数据信息;MDIO控制器,用于按照预设的周期将控制数据信息写入第一地址信息对应的PHY芯片的引脚的寄存器,以对PHY芯片的引脚的状态进行自动控制。采用本发明技术方案可以用同一个MDIO控制器对多个PHY

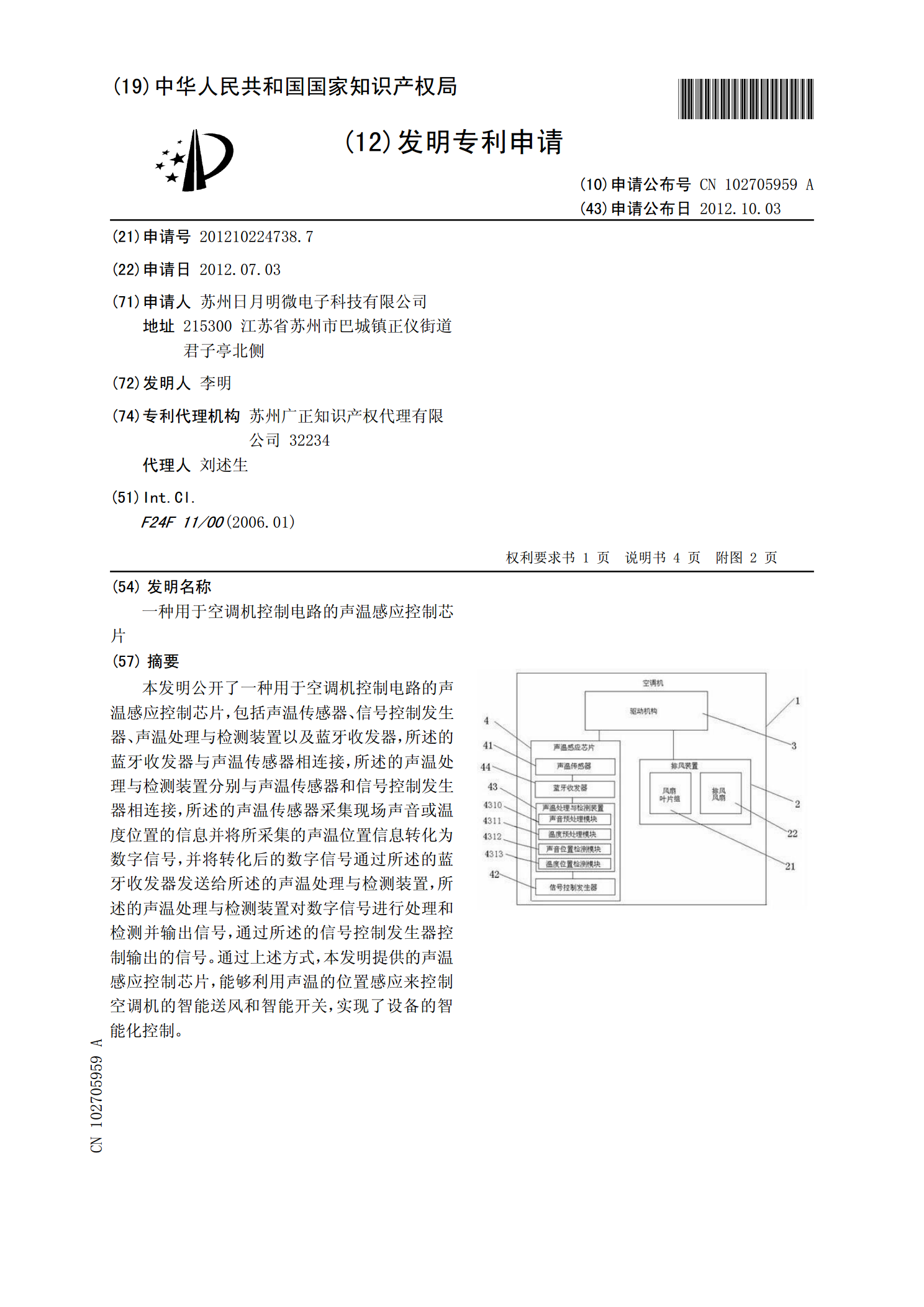

一种用于空调机控制电路的声温感应控制芯片.pdf

本发明公开了一种用于空调机控制电路的声温感应控制芯片,包括声温传感器、信号控制发生器、声温处理与检测装置以及蓝牙收发器,所述的蓝牙收发器与声温传感器相连接,所述的声温处理与检测装置分别与声温传感器和信号控制发生器相连接,所述的声温传感器采集现场声音或温度位置的信息并将所采集的声温位置信息转化为数字信号,并将转化后的数字信号通过所述的蓝牙收发器发送给所述的声温处理与检测装置,所述的声温处理与检测装置对数字信号进行处理和检测并输出信号,通过所述的信号控制发生器控制输出的信号。通过上述方式,本发明提供的声温感应