逻辑函数的化简.ppt

YY****。。

亲,该文档总共70页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

逻辑函数化简.ppt

第2章逻辑代数基础本节主要内容基本形式:“与-或”表达式、“或-与”“或-与”:若干个或项相与构成。也称为“和之积”表达式。例如:1、最小项与最大项3个变量A、B、C的8个最小项可以分别表示为:b)任意两个不同的最小项之积必为0。(2)最大项b)任意两个不同的最大项之和必为1。(3)最小项与最大项之间的互补关系2、逻辑函数表达式的标准形式例如上式可以写成为F(A,B,C)=M0M5M71、代数转换法第一步:将函数表达式转换为与-或表达式。即可以简写为:F(A,B,C)=m0+m1+m3+m6+m7=∑m(

逻辑函数的化简.ppt

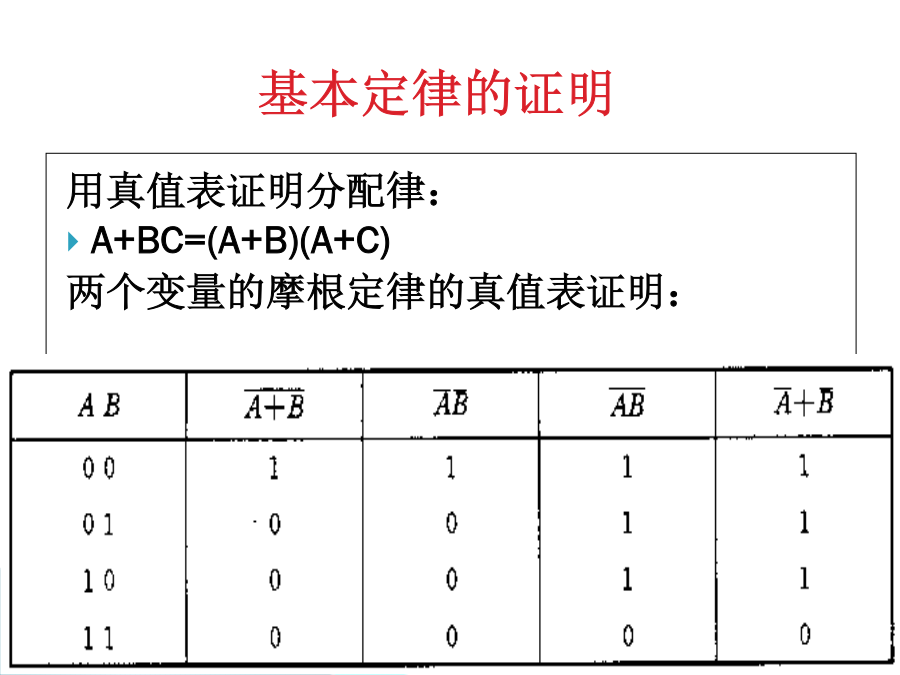

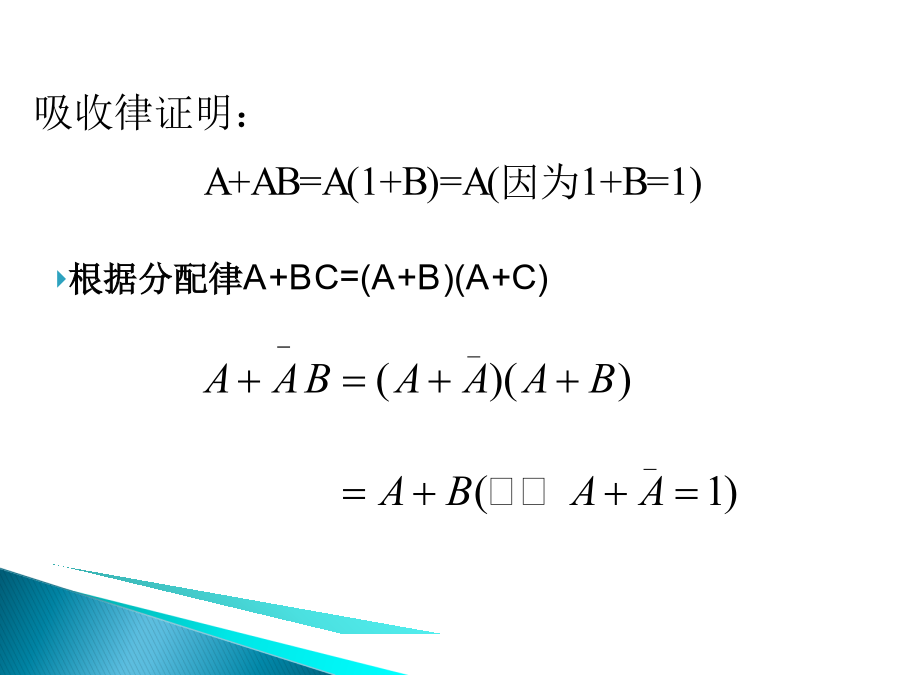

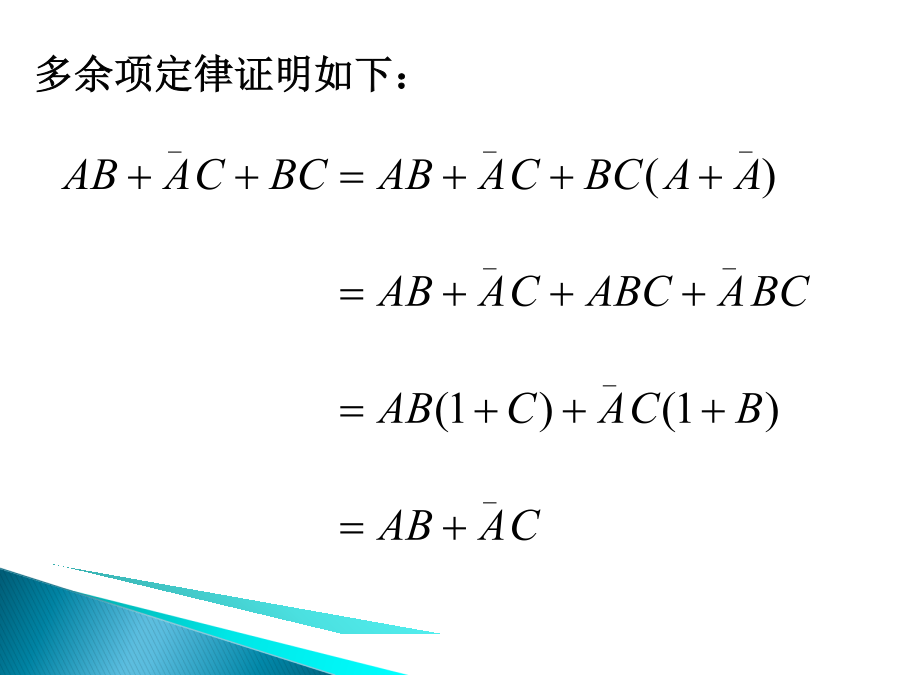

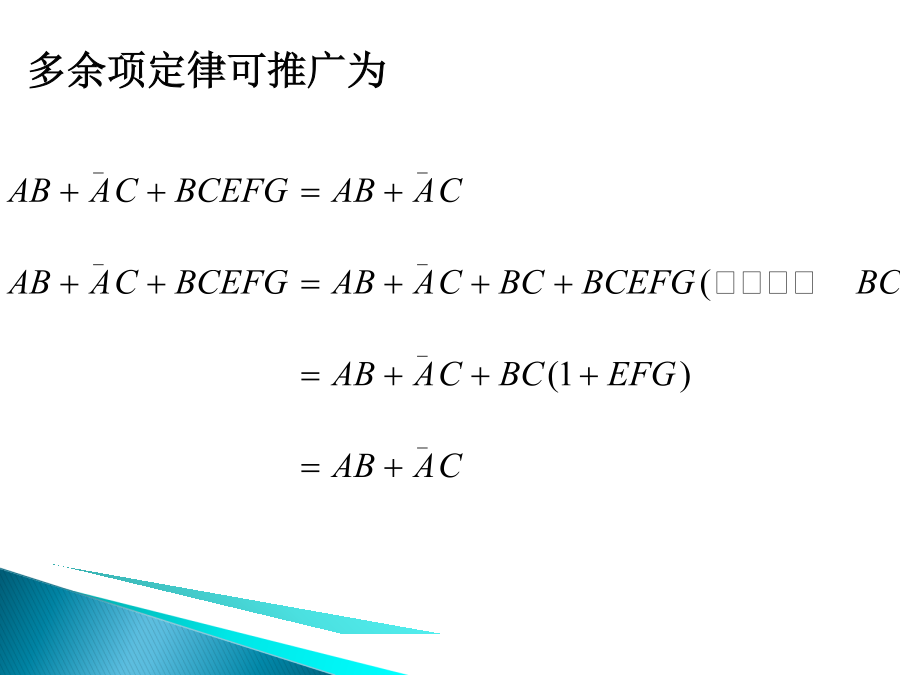

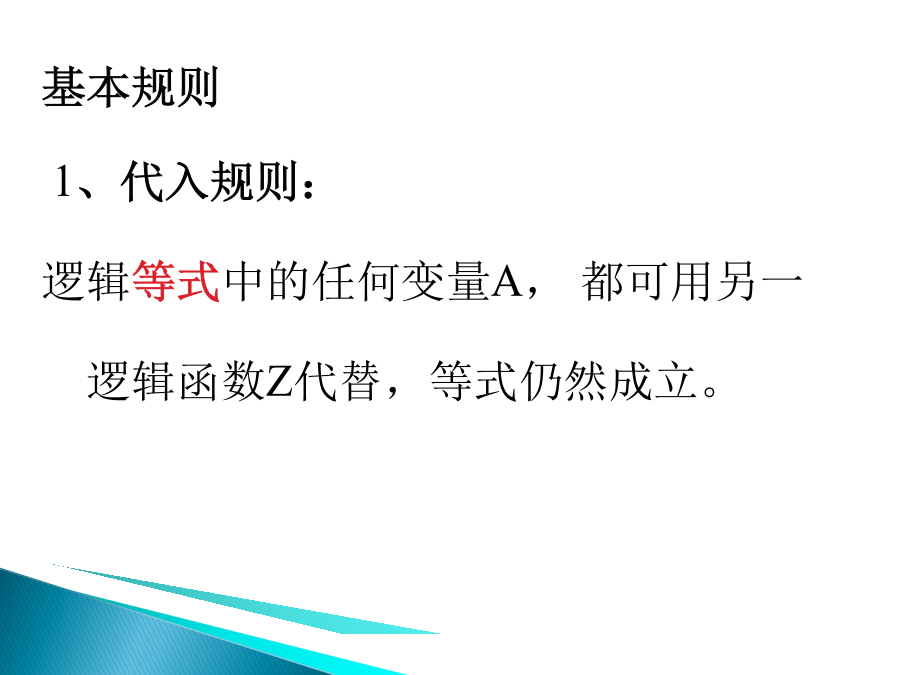

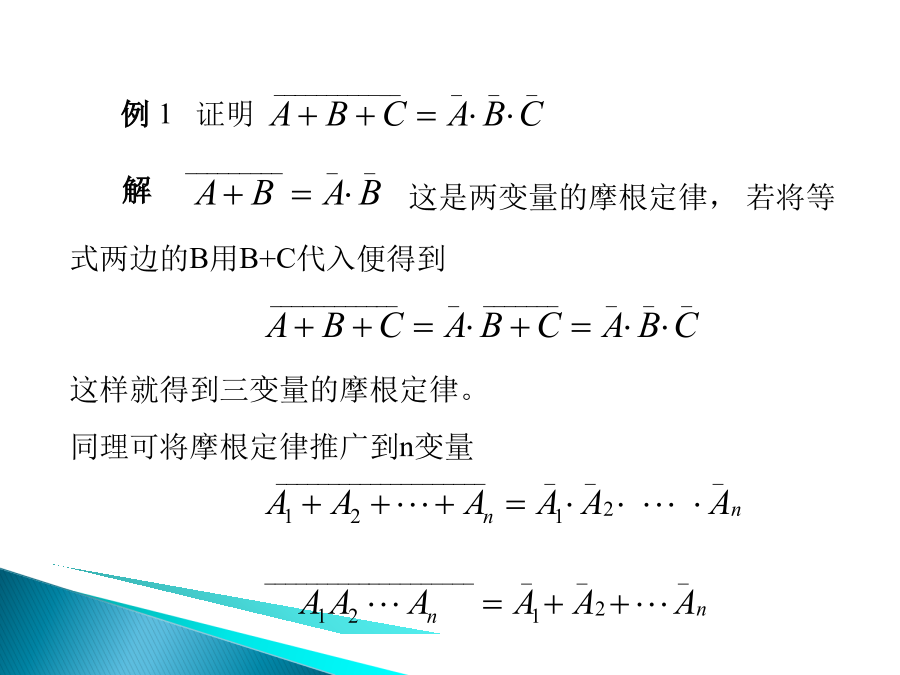

上节主要内容回顾本讲主要内容用真值表证明分配律:A+BC=(A+B)(A+C)两个变量的摩根定律的真值表证明:吸收律证明:A+AB=A(1+B)=A(因为1+B=1)多余项定律可推广为基本规则1、代入规则:逻辑等式中的任何变量A,都可用另一逻辑函数Z代替,等式仍然成立。例1证明2.对偶法则对于任何一个逻辑表达式F,如果将其中的“+”换成“·”,“·”换成“+”,“1”换成“0”,“0”换成“1”,则可得原函数F的对偶式G,且F和G互为对偶式。对偶法则:原式F成立,则其对偶式也一定成立。其对偶式为:3.反演

逻辑函数化简方法.ppt

一、标准与或表达式1.最小项的概念:对应规律:1原变量0反变量3.最小项的编号:4.最小项是组成逻辑函数的基本单元[例]写出下列函数的标准与或式:最简或与式1.2.2逻辑函数的公式化简法二、吸收法:三、消去法:四、配项消项法:综合练习:1.2.3逻辑函数的图形化简法2.变量卡诺图的画法五变量的卡诺图:3.卡诺图的特点:4.卡诺图中最小项合并规律:(2)四个相邻最小项合并可以消去两个因子(3)八个相邻最小项合并可以消去三个因子二、逻辑函数的卡诺图表示法三、用卡诺图化简逻辑函数AB[例]利用图形法化简函数

逻辑函数及其化简.ppt

第4章逻辑函数及其化简第一节逻辑函数式的最简形式例如与或式和或与式是最常用的逻辑表达式。最简与或式的标准是:①含的与项最少;②各与项中含的变量数最少。最简或与项的标准是:①含的或项最少;②各或项中含的变量数最少。与或式可变换成与非-与非式或与式变换成或非-或非式相乘而得到的n因子乘积项称为该函数的最小项。在一个最小项中,每个变量不是以原变量就是以反变量形式出现并仅出现一次。在n变量逻辑函数中,n个变量可以构成2n个最小项。如3变量A、B、C构成的任何逻辑函数,都有23=8个最小项;同理4变量的逻辑函数有2

逻辑代数和逻辑函数化简.ppt

与逻辑1.与逻辑:真值表真值表2.或逻辑:真值表例:根据输入波形画出输出波形3.非逻辑:(1)与非逻辑(1)或非逻辑(3)与或(非)逻辑(4)异或逻辑3.逻辑符号对照国标符号或:三、与普通代数相似的定理证明公式四、逻辑代数的一些特殊定理五、若干常用公式(5)六、关于异或运算的一些公式(4)常量和变量的异或运算2.2.2逻辑代数的基本规则例如:已知3.对偶规则:2.3.1逻辑表达式完备函数的概念或与式标准与或表达式1.最小项的概念:对应规律:1原变量0反变量3.最小项的编号:4.最小项标准表达式2.3.