时钟产生电路自校正系统及其校正方法.pdf

念珊****写意

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

时钟产生电路自校正系统及其校正方法.pdf

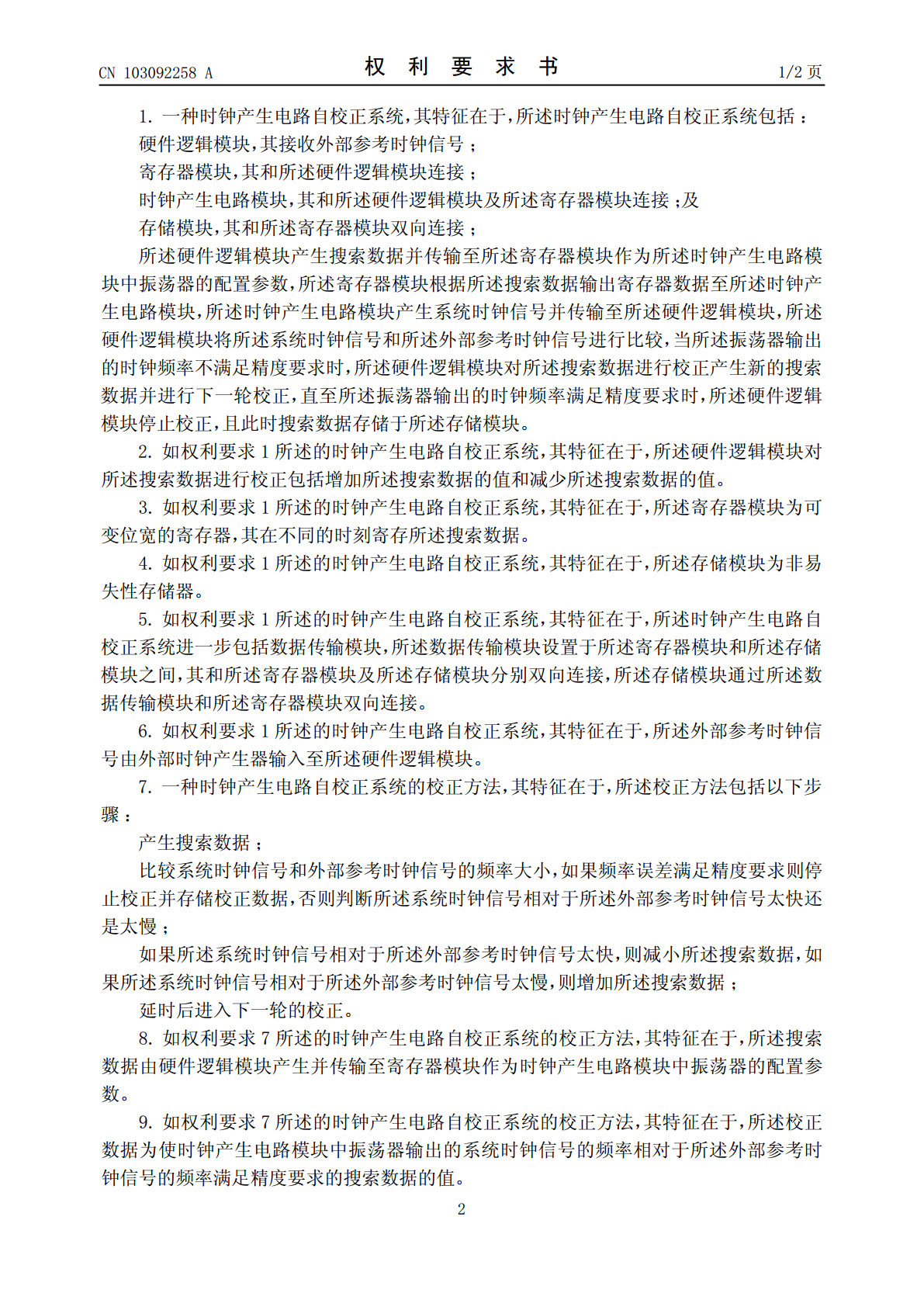

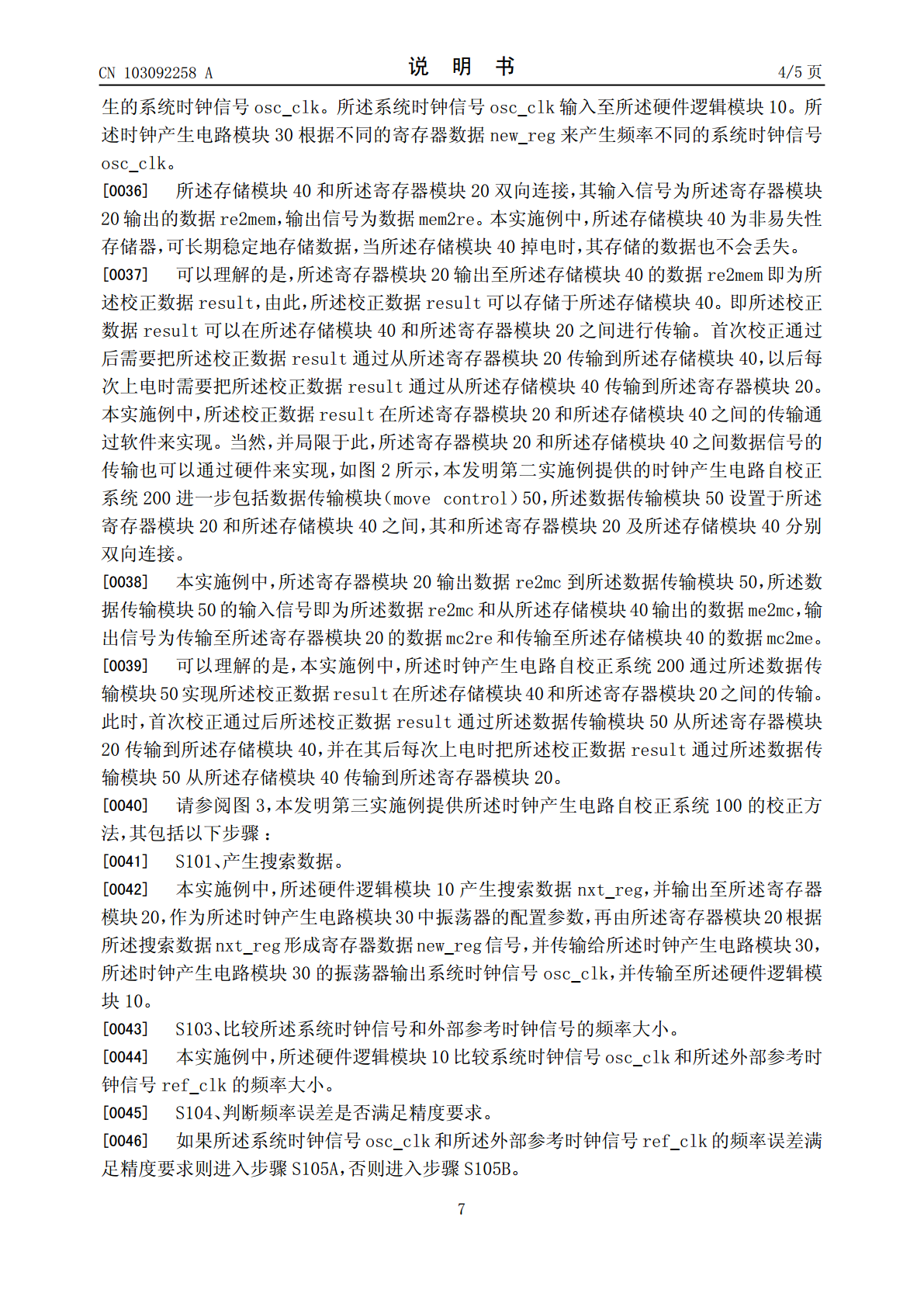

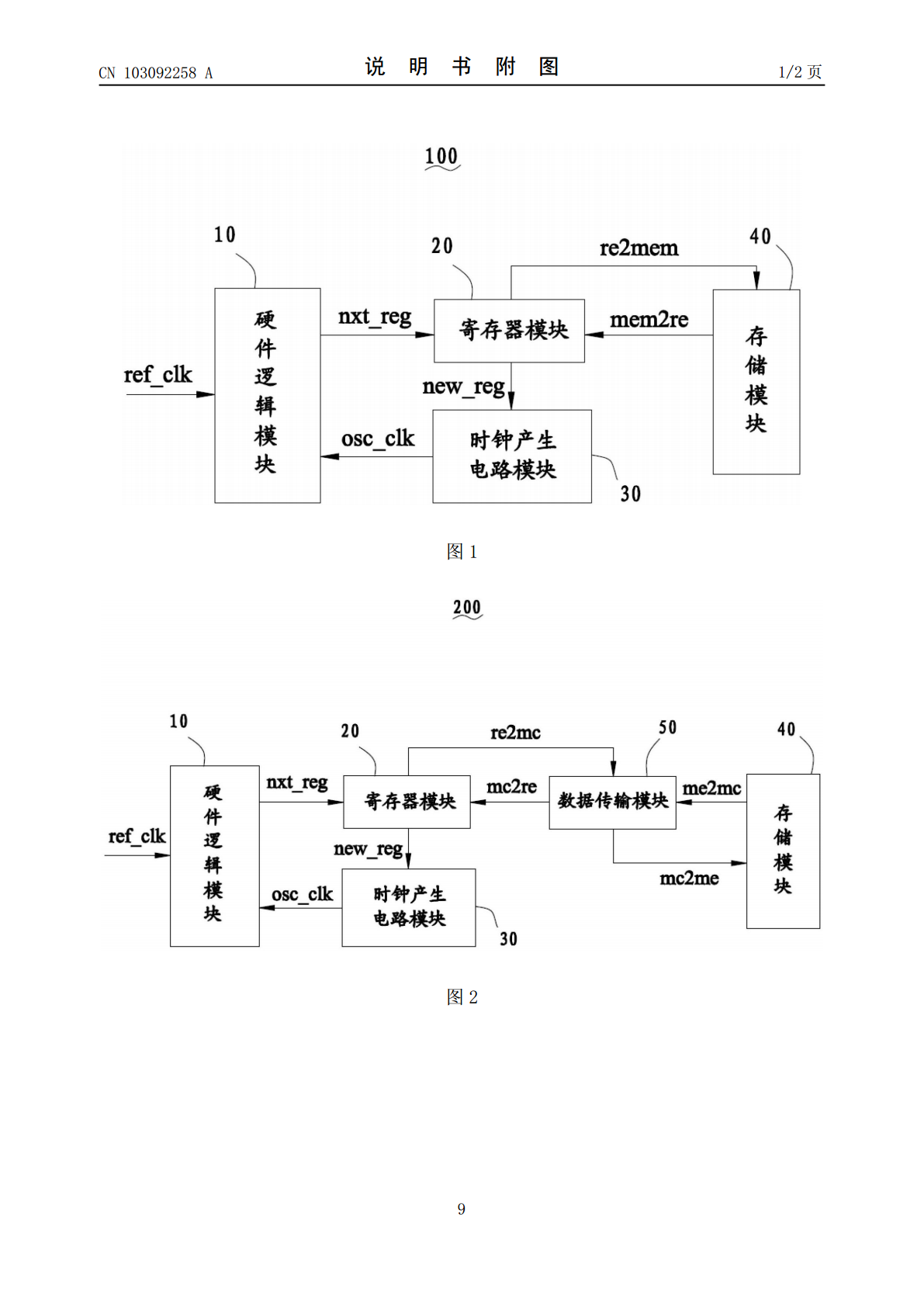

本发明提出一种时钟产生电路自校正系统和方法,其中系统包括硬件逻辑模块、和硬件逻辑模块连接的寄存器模块、和硬件逻辑模块及寄存器模块连接的时钟产生电路模块及和寄存器模块双向连接的存储模块,其中硬件逻辑模块产生搜索数据并传输至寄存器模块作为时钟产生电路模块的配置参数,寄存器模块输出寄存器数据至时钟产生电路模块,产生系统时钟信号并传输至硬件逻辑模块,系统时钟信号和外部参考时钟信号进行比较,当不满足精度要求时,对搜索数据进行校正产生新的搜索数据并进行下一轮校正,直至满足精度要求时,硬件逻辑模块停止校正,且此时搜索数

图像校正方法及其预处理方法、图像校正电路.pdf

本发明实施例公开了一种图像校正方法及其预处理方法、图像校正电路,其中所述预处理方法包括:获取各个目标灰阶下,至少三个颜色通道对应的色坐标信息;根据最高灰阶时的最高亮度,确定各个所述目标灰阶的目标亮度;根据各个所述目标灰阶下各个所述颜色通道的所述色坐标信息,确定各个所述目标灰阶下各个颜色通道的亮度比例;根据各个所述目标灰阶的目标亮度以及各个颜色通道的亮度比例,确定各个所述目标灰阶下各个颜色通道的配比亮度;在各个所述目标灰阶与对应的各个颜色通道的配比亮度之间分别建立关联关系。

一种自校正可拼接式光纤位移场传感系统及其校正方法.pdf

本发明提供了一种自校正可拼接式光纤位移场传感系统及其校正方法,包括:若干可拼接式柔性光纤传感装置,用于测量位移场;若干倾角自感知连接装置,用于可拼接式柔性光纤传感装置之间的连接;光纤解调仪,用于获取可拼接式柔性光纤传感装置的应变数据和倾角自感知连接装置的二轴倾角数据,对传感装置位移数据进行误差修正;可拼接式柔性光纤传感装置之间通过倾角自感知连接装置连接,且连接后的可拼接式柔性光纤传感装置的两端均还连接有倾角自感知连接装置,光纤解调仪与倾角自感知连接装置的自由端的一侧连接。本发明可根据大型结构的尺寸自主拼接

校正系统、校正装置和校正方法.pdf

本发明提供一种校正系统,至少1台校正控制装置,及与其通讯的处理装置;所述校正控制装置,包括:拍摄部,用于拍摄获得热像数据;校正控制部,根据基础图像信息来进行校正处理的控制;部分或全部的影响因素、部分或全部的基础图像信息、部分或全部的影响因素与基础图像信息的对应关系,其中之一或多个或全部,来源于所述处理装置或校正控制装置;用于校正处理的基础图像信息,为基于影响因素与基础图像信息的对应关系,根据所获取的影响因素的数据,根据所述对应关系,确定的基础图像信息。由此,来解决现存的问题。

自校准的低噪声工作周期校正电路及其方法.pdf

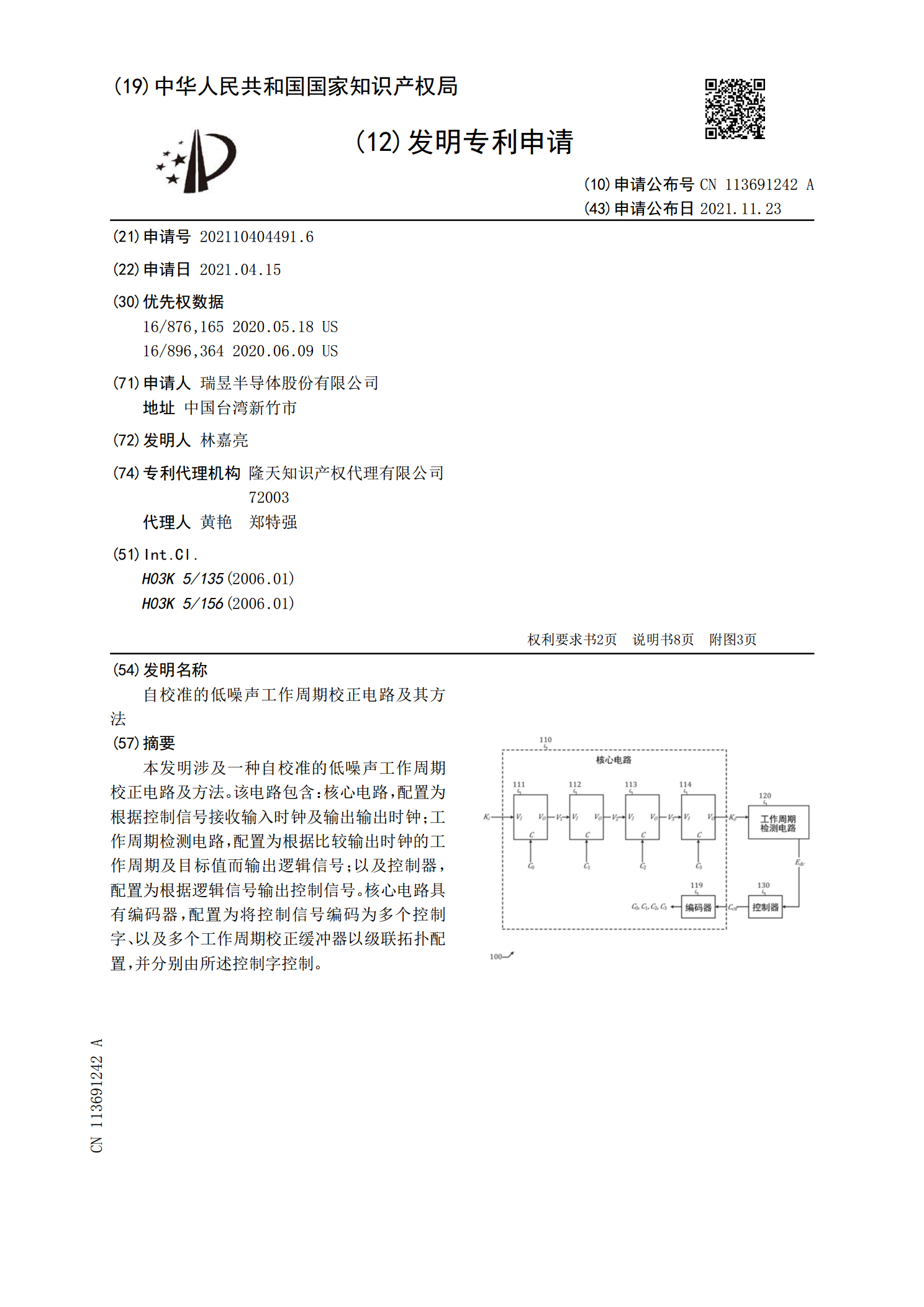

本发明涉及一种自校准的低噪声工作周期校正电路及方法。该电路包含:核心电路,配置为根据控制信号接收输入时钟及输出输出时钟;工作周期检测电路,配置为根据比较输出时钟的工作周期及目标值而输出逻辑信号;以及控制器,配置为根据逻辑信号输出控制信号。核心电路具有编码器,配置为将控制信号编码为多个控制字、以及多个工作周期校正缓冲器以级联拓扑配置,并分别由所述控制字控制。