自校准的低噪声工作周期校正电路及其方法.pdf

论文****轩吖

亲,该文档总共14页,到这已经超出免费预览范围,如果喜欢就直接下载吧~

相关资料

自校准的低噪声工作周期校正电路及其方法.pdf

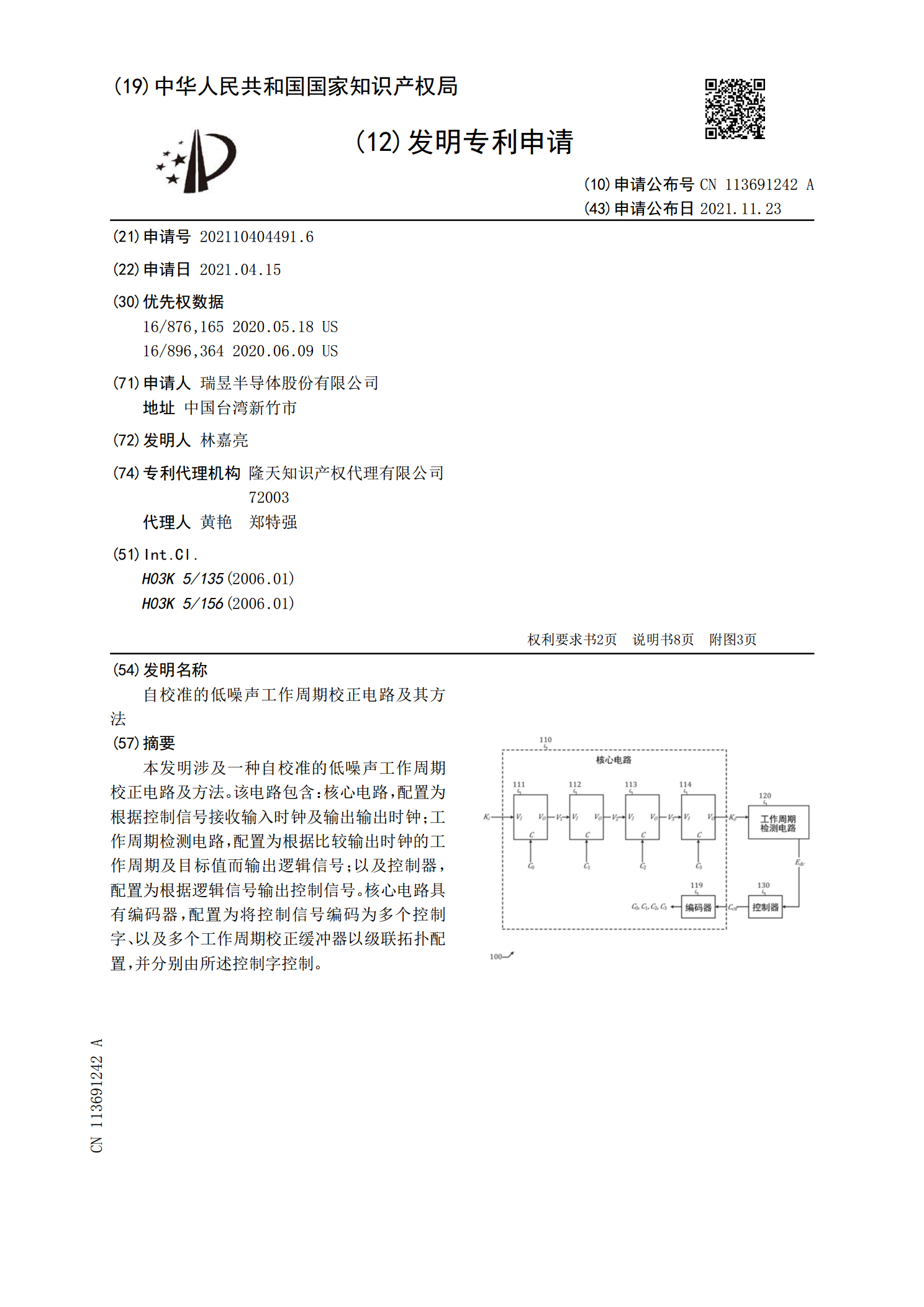

本发明涉及一种自校准的低噪声工作周期校正电路及方法。该电路包含:核心电路,配置为根据控制信号接收输入时钟及输出输出时钟;工作周期检测电路,配置为根据比较输出时钟的工作周期及目标值而输出逻辑信号;以及控制器,配置为根据逻辑信号输出控制信号。核心电路具有编码器,配置为将控制信号编码为多个控制字、以及多个工作周期校正缓冲器以级联拓扑配置,并分别由所述控制字控制。

时钟产生电路自校正系统及其校正方法.pdf

本发明提出一种时钟产生电路自校正系统和方法,其中系统包括硬件逻辑模块、和硬件逻辑模块连接的寄存器模块、和硬件逻辑模块及寄存器模块连接的时钟产生电路模块及和寄存器模块双向连接的存储模块,其中硬件逻辑模块产生搜索数据并传输至寄存器模块作为时钟产生电路模块的配置参数,寄存器模块输出寄存器数据至时钟产生电路模块,产生系统时钟信号并传输至硬件逻辑模块,系统时钟信号和外部参考时钟信号进行比较,当不满足精度要求时,对搜索数据进行校正产生新的搜索数据并进行下一轮校正,直至满足精度要求时,硬件逻辑模块停止校正,且此时搜索数

一种自校正射频模组及其校准系统和校准方法.pdf

本发明涉及射频技术领域,公开了一种自校正射频模组及其校准系统和校准方法,该自校正射频模组包括:串口模块、射频芯片和功率检测模块;本发明的自校正射频模组可以通过功率检测模块来获取射频芯片的实际输出功率,根据实际输出功率反馈实际输出信号至射频芯片的数据处理部分;射频芯片可以根据实际输出信号在有限幅度内自动调节增益,从而保证射频芯片的实际输出功率与目标输出功率相同。本发明通过将功率检测模块集成在小型化的射频模组中,从而构成了闭环体系,弱化了外部驻波变化对射频模组输出功率的影响,使得射频模组的实际输出功率与目标输

低噪声矢量水听器设计及其校准方法研究.docx

低噪声矢量水听器设计及其校准方法研究一、研究背景和意义水下声学测量在海洋勘探、水下通信、水下生物研究等领域具有重要的应用价值。矢量水听器作为一种高精度的水下声学传感器,可以实时获取水下目标的声场信息,为相关领域的研究提供了有力的技术支持。然而矢量水听器的性能受到环境噪声的影响,特别是低频噪声,这会导致测量结果的不准确,从而影响到实际应用。因此研究低噪声矢量水听器的设计及其校准方法具有重要的理论和实际意义。首先研究低噪声矢量水听器的设计方法,可以提高矢量水听器的性能,使其在各种复杂环境下都能实现高精度的声场

带连接管暖风芯子总成校正装置及其校准校正方法.pdf

本发明涉及汽车空调零部件制造领域,公开了一种带连接管暖风芯子总成校正装置,包括底板,底板上设有定位总成、夹紧总成和校正总成;校正总成包括通过滑轨底座倾斜安装在底板上的滑轨,滑轨上套有传感器支座,传感器支座靠近第一支撑条的一端设有圆孔,圆孔内设有第一传感器,传感器支座的另一端设有拉手,底板上位于滑轨底座端部的位置设有第二传感器,传感器支座朝向第二传感器的一端设有感应凸柱。本发明还公开了一种带连接管暖风芯子总成校正装置的校准方法和校正方法。本发明带连接管暖风芯子总成校正装置及其校准校正方法,在保证暖风总成连接