宽带ADC低抖动时钟驱动电路的分析与设计.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

宽带ADC低抖动时钟驱动电路的分析与设计.docx

宽带ADC低抖动时钟驱动电路的分析与设计一、引言宽带ADC是一种高精度、高速度的数据采集装置,其性能取决于时钟抖动的大小。时钟抖动会导致ADC采样的误差增大,因此如何降低时钟抖动,是设计宽带ADC低抖动时钟驱动电路的关键。本文将对该电路进行分析与设计。二、时钟抖动的影响时钟抖动是指时钟信号中存在的不稳定和不确定的波动。时钟信号在每个采样周期内需要保持稳定,因为在ADC每次采样时,时钟信号是用来同步数据转换的。如果时钟信号的稳定性不好,就会直接影响ADC采样精度,并且可能会导致噪声等问题。三、低抖动时钟驱动

低抖动时钟占空比校准电路的研究与设计综述报告.docx

低抖动时钟占空比校准电路的研究与设计综述报告随着数字电子技术的不断发展,时钟信号的准确性和稳定性在许多应用领域中扮演着非常重要的角色。特别是在通信、计算机和测量等领域,高性能时钟信号的要求越来越高。然而,在实际应用中,由于存在一些因素的干扰,时钟信号的稳定性会受到影响,从而导致时钟信号的抖动问题。因此,为了解决时钟信号抖动问题,低抖动时钟占空比校准电路得到了广泛关注。低抖动时钟占空比校准电路是一种可以有效减少时钟信号抖动的电路,通过对时钟信号的占空比进行校准来实现减小时钟信号抖动的目的。在本文中,我们将对

基于ADC检测技术的时钟抖动分析与仿真的中期报告.docx

基于ADC检测技术的时钟抖动分析与仿真的中期报告一、研究背景在现代数字通信中,时钟同步是实现高效数据传输和可靠通信的基础。时钟抖动是指时钟信号的不确定性,它是时钟同步误差的重要来源。时钟抖动可以来源于各种因素,如时钟精度、供电噪声、环境温度等,因此,时钟抖动的理解和分析对于系统设计和优化至关重要。此外,随着通信系统的不断发展,时钟同步的需求也在不断增加。目前,各种网络应用和服务,如4G/5G移动通信、云计算、物联网等,都要求高精度时钟同步。因此,研究时钟抖动的分析和消除方法,对于提高通信系统的性能和可靠性

一种实现低抖动的时钟产生电路.pdf

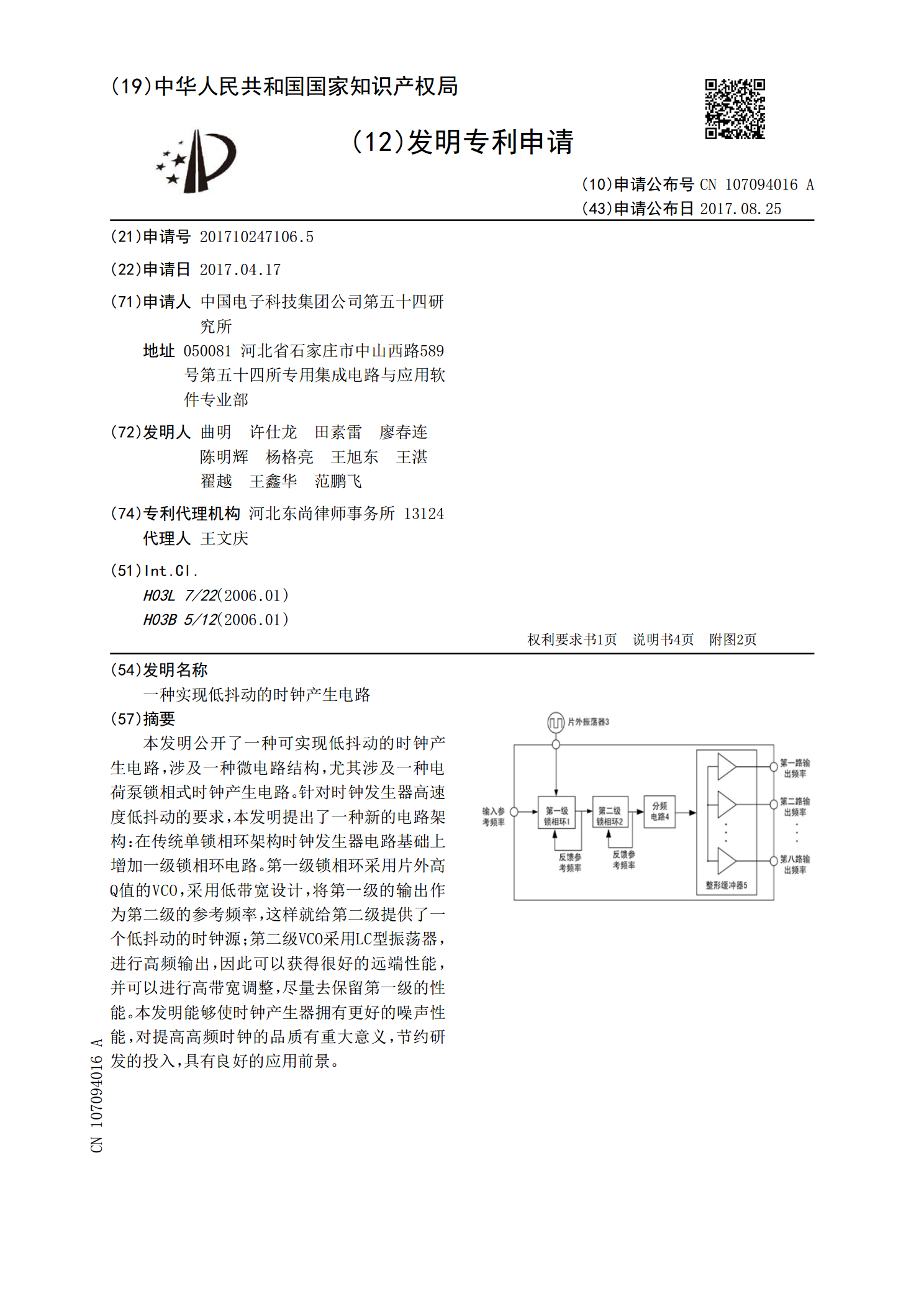

本发明公开了一种可实现低抖动的时钟产生电路,涉及一种微电路结构,尤其涉及一种电荷泵锁相式时钟产生电路。针对时钟发生器高速度低抖动的要求,本发明提出了一种新的电路架构:在传统单锁相环架构时钟发生器电路基础上增加一级锁相环电路。第一级锁相环采用片外高Q值的VCO,采用低带宽设计,将第一级的输出作为第二级的参考频率,这样就给第二级提供了一个低抖动的时钟源;第二级VCO采用LC型振荡器,进行高频输出,因此可以获得很好的远端性能,并可以进行高带宽调整,尽量去保留第一级的性能。本发明能够使时钟产生器拥有更好的噪声性能

D转换器的低抖动时钟稳定电路设计的开题报告.docx

用于高速A/D转换器的低抖动时钟稳定电路设计的开题报告一、选题随着信息技术的发展和应用的不断深入,对高速A/D转换器的需求也越来越多,而时钟稳定电路作为A/D转换器中的重要组成部分,其设计质量直接影响到整个系统的性能和稳定性。因此,本文选题为用于高速A/D转换器的低抖动时钟稳定电路设计。二、研究内容本文主要研究以下内容:1.时钟稳定电路的基本原理和设计要求:介绍时钟稳定电路的工作原理,分析其在高速A/D转换器中的重要性,探讨时钟稳定电路的设计要求。2.低抖动时钟稳定电路的设计思路与方法:介绍低抖动时钟稳定