基于FPGA和EPP的芯片测试电路设计.docx

快乐****蜜蜂

在线预览结束,喜欢就下载吧,查找使用更方便

相关资料

基于FPGA和EPP的芯片测试电路设计.docx

基于FPGA和EPP的芯片测试电路设计随着技术的不断发展和市场对芯片质量的逐渐提高,芯片测试电路设计的重要性也逐渐凸显出来。本篇论文将讨论基于FPGA和EPP的芯片测试电路设计,介绍其原理和优势,并针对几个重要的问题进行深入探讨。一、FPGA和EPP技术简介FPGA(FieldProgrammableGateArray)是一种可编程逻辑器件,通过烧录后可实现特定的逻辑电路功能。FPGA优点是可以在生产后进行编程,无需进行物理修改,减少了研发周期和生产成本,大大提高了设计效率和灵活性。EPP(Enhance

一种FPGA芯片测试平台和FPGA芯片测试方法.pdf

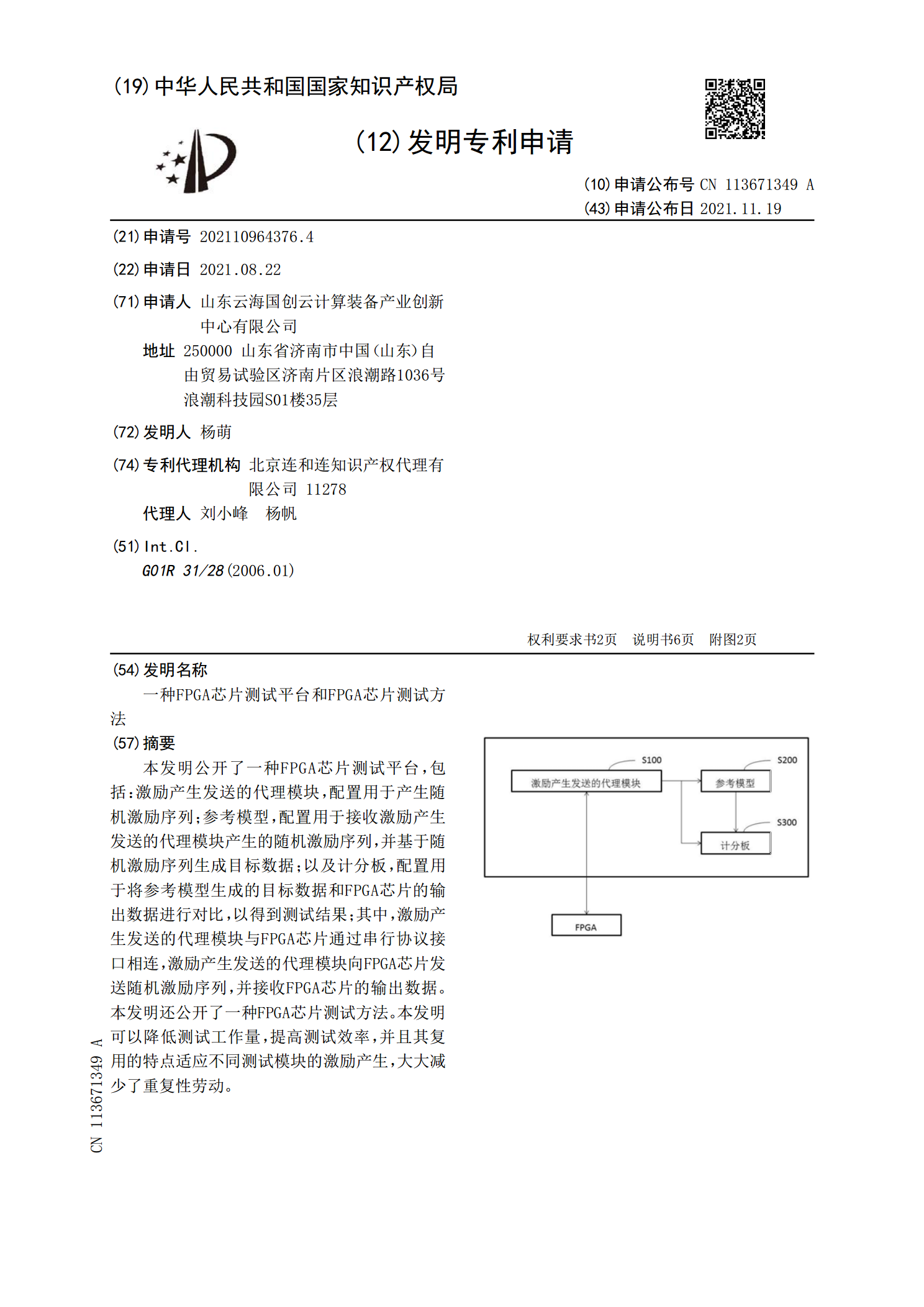

本发明公开了一种FPGA芯片测试平台,包括:激励产生发送的代理模块,配置用于产生随机激励序列;参考模型,配置用于接收激励产生发送的代理模块产生的随机激励序列,并基于随机激励序列生成目标数据;以及计分板,配置用于将参考模型生成的目标数据和FPGA芯片的输出数据进行对比,以得到测试结果;其中,激励产生发送的代理模块与FPGA芯片通过串行协议接口相连,激励产生发送的代理模块向FPGA芯片发送随机激励序列,并接收FPGA芯片的输出数据。本发明还公开了一种FPGA芯片测试方法。本发明可以降低测试工作量,提高测试效率

FPGA芯片关键电路设计的综述报告.docx

FPGA芯片关键电路设计的综述报告FPGA(FieldProgrammableGateArray)芯片是目前应用十分广泛的数字电路系统级集成芯片,其功能可通过可编程的内部电路架构进行实现和修改,使得FPGA芯片具有可重构的特点。FPGA芯片的设计底层依赖于关键电路的设计。因此,对FPGA芯片关键电路设计的综述是本文的重点,本文将从三个方面进行阐述:FPGA芯片关键电路的基本原理、FPGA芯片关键电路设计的过程和方法、FPGA芯片关键电路设计的未来发展方向。一、FPGA芯片关键电路的基本原理FPGA芯片关键

FPGA芯片关键电路设计的任务书.docx

FPGA芯片关键电路设计的任务书任务书:前言:FPGA(FieldProgrammableGateArray)芯片作为一种可现场编程的逻辑集成电路,已经成为数字电路设计中最为重要的一部分。在FPGA芯片的设计中,关键电路的设计是至关重要的一步,因为该设计直接决定了FPGA芯片的工作性能和稳定性。因此,本文的任务就是针对FPGA芯片关键电路设计进行探究和研究,并提供设计方案。一、任务背景FPGA芯片作为一种重要的信息处理器件已经广泛应用于各个领域。其主要特点是可以灵活调整功能,可以支持高速数字信号处理,可以

基于FPGA的混合信号芯片测试系统设计.docx

基于FPGA的混合信号芯片测试系统设计标题:基于FPGA的混合信号芯片测试系统设计摘要:随着科技的进步,集成电路的复杂度不断提高,混合信号芯片的测试变得越来越重要。本论文提出了一种基于FPGA的混合信号芯片测试系统设计,该系统以FPGA芯片为核心,通过数字信号处理技术进行模拟信号的数字化和处理,实现对混合信号芯片的全面测试,提高测试效率和精度。通过计算机控制系统和外围硬件电路的设计,实现了对混合信号芯片各个模块的测试。关键词:FPGA,混合信号芯片,测试系统,数字信号处理1.引言随着集成电路技术的快速发展